# Study Of IGBT Drive For Three Phase Load

By

Mohd Khairul Hanafi Bin Mhd Jamin

Dissertation Report submitted in partial fulfillment of the requirements for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

JUNE 2010

Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

# **CERTIFICATION OF APPROVAL**

# STUDY OF IGBT DRIVE FOR THREE PHASE LOAD

By

Mohd Khairul Hanafi Bin Mhd Jamin

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfillment of the requirement for the BACHELOR OF ENGINEERING (Hons) (ELECTRICAL & ELECTRONICS ENGINEERING)

Approved by:

Mr Saiful Azrin Bin Mohd Zulkifli

Project Supervisor

UNIVERSITI TEKNOLOGI PETRONAS

TRONOH, PERAK

Jun 2010

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

belle

MOHD KHAIRUL HANAFI BIN MHD JAMIN

#### ABSTRACT

This dissertation discusses the project, "Study of IGBT drive three for three phase load". This project deals with the IGBT theory, the three phase inverter and the gate driver characteristics. The objective of this project is to study and simulate the IGBT drive for the three phase load. This report also describe the hardware description that were used in this project that is the SEMIKRON SKiiP 39ACT4V1 Three-phase Bridge Rectifier and the SEMIKRON SKHI 23/12 (R) Driver. The methodology chapter explained the procedures of handling the project, starting from the problem statement until the procedure identification. It also lists out the tools and equipments needed to execute this project. The last chapter discusses the summarized information of the overall project. Throughout of this project, the author had deal with the new software and work with a lot of people. Some information in this report had been taken from other source and all had been credited in the reference.

#### ACKNOWLEDGEMENTS

First and foremost the author would like to take this opportunity to express his appreciation to all the parties that is involved in making Final Year Project (FYP) a success. The undergoing of this project would have not been possible without the assistance and guidance of certain individuals and organization whose contributions have helped in its completion.

The author would like to express his deepest appreciation to his project supervisor, Mr. Saiful Azrin Bin Mohd Zulkifli for his endless support, guidance and consultation regarding this project throughout the year.

Special thanks to lab technologist; Mdm. Siti Hawa who has given countless technical support to the author in providing both advice and components, hardware, or software the author requires in completion of the project and also Mr. Isnani who had given technical support during the fabricating process.

Last but not least, the author would like to give out her thanks to all those who have contributed directly or indirectly to the success of this project.

# TABLE OF CONTENTS

| CERTIFICATION OF APPROVAL    | ii   |

|------------------------------|------|

| CERTIFICATION OF ORIGINALITY | iii  |

| ABSTRACT                     | iv   |

| ACKNOWLEDGEMENT              | v    |

| LIST OF FIGURES              | viii |

| LIST OF TABLES               | x    |

# CHAPTER 1: INTRODUCTION

| 1.1 | Background of Study | . 1 |

|-----|---------------------|-----|

| 1.2 | Problem Statement   | . 2 |

| 1.3 | Objective           | 3   |

# CHAPTER 2: LITERATURE REVIEW

| 2.1 | Insula | ted-Gate Bipolar Transistor (IGBT) | 4  |

|-----|--------|------------------------------------|----|

|     | 2.1.1  | Introduction of IGBT               | 4  |

|     | 2.1.2  | IGBT Switching Characteristic      | 6  |

|     | 2.1.3  | Turn-on Transients                 | 7  |

|     | 2.1.4  | Turn-off Transient                 | 9  |

| 2.2 | Invert | er                                 | 11 |

|     | 2.2.1  | Inverter in Power Electronic       | 11 |

|     | 2.2.2  | Three Phase Inverter               | 11 |

| 2.3 | Gate I | Driver                             | 12 |

# CHAPTER 3: METHODOLOGY

| 3.1 | Proce  | dure Identified14                                             |

|-----|--------|---------------------------------------------------------------|

| 3.2 | Tools  | and Equipments Required15                                     |

| 3.3 | Projec | t Works16                                                     |

|     | 3.3.1  | Intensive Literature Reviews16                                |

|     | 3.3.2  | Selecting a suitable off-the-shelf IGBT inverter and the gate |

|     |        | driver16                                                      |

|     | 3.3.3  | Fabricating and Troubleshooting16                             |

# CHAPTER 4: RESULT AND DISCUSSION

| 4.1 | SEM    | KRON SKHI 23/12 (R) Driver17                                     |

|-----|--------|------------------------------------------------------------------|

|     | 4.1.1  | Device Description17                                             |

| 4.2 | SEM    | KRON SKiiP 39ACT4V1 Three-phase Bridge Rectifier22               |

| 4.3 | Drafti | ng the Block Diagram Connection of devices23                     |

| 4.4 | Plug   | Connectors PCB Driver                                            |

| 4.5 | Fabric | cating the PCB board for the interfacing between gate driver and |

|     | the IC | BTs25                                                            |

|     | 4.5.1  | EAGLE Layout Editor Software Designing Process25                 |

|     | 4.5.2  | Problem Encountered26                                            |

|     | 4.5.3  | GC-Power Station Layout Editor Software PCB Designing            |

|     |        | Process                                                          |

|     | 4.6    | Interfacing the Gate Driver and the IGBT Inverter via the PCB    |

|     |        | <i>board</i> 40                                                  |

# CHAPTER 5: CONCLUSION AND RECOMMENDATION

| 5.1 | Conclusion     | 42 |

|-----|----------------|----|

| 52  | Recommendation | 12 |

| REFERENCES |  |

|------------|--|

| APPENDICES |  |

# LIST OF FIGURES

| Figure 1: Physical structure of an IGBT                               | 5  |

|-----------------------------------------------------------------------|----|

|                                                                       |    |

| Figure 2: Inductive load test circuit                                 |    |

| Figure 3: Equivalent circuit of the IGBT                              |    |

| Figure 4: The flow Chart of the process involved in FYP               | 14 |

| Figure 5: Top View                                                    | 18 |

| Figure 6: Side View                                                   | 19 |

| Figure 7: SKHI 23/12(R) Dual IGBT Gate Driver                         | 20 |

| Figure 8: Connecting the SKHI 23/12 (R) with short cables             | 21 |

| Figure 9: SEMIKRON SKiiP 39ACT4V1 physical view                       | 23 |

| Figure 10: The block diagram of the bridge rectifier                  |    |

| Figure 11: The Layout Dimension of inverter                           |    |

| Figure 12: Creating a new project in editor menu                      |    |

| Figure 13: Add menu on the schematic                                  |    |

| Figure 14: The Pin header component menu                              |    |

| Figure 15: 56 units of pin headers in the schematic view              | 29 |

| Figure 16: Switch to board menu                                       |    |

| Figure 17: Grid Setting                                               |    |

| Figure 18: Plotting pin headers on the board                          |    |

| Figure 19: Completed Board                                            |    |

| Figure 20: Error on the Board                                         |    |

| Figure 21: The Open New File View                                     |    |

| Figure 22: Drawing the connection points on the board                 |    |

| Figure 23: The Completed connection between E-connectors and E-points |    |

| Figure 24: The route setting                                          |    |

|                                                                       |    |

| Figure 25: The connection of output phase points           | .37 |

|------------------------------------------------------------|-----|

| Figure 26: Output route line setting                       | .37 |

| Figure 27: The complete route for output phase connection  | .38 |

| Figure 29: The fabricated PCB board                        | .39 |

| Figure 30: Connecting the IGBT inverter with the PCB board | 39  |

| Figure 31: Side View of hardware initial setup             | 40  |

| Figure 32: Front View of hardware initial setup            | .41 |

# LIST OF TABLES

## **CHAPTER 1**

# INTRODUCTION

#### 1.1 Background Of Study

The insulated gate bipolar transistor or IGBT is a three-terminal power semiconductor device, noted for high efficiency and fast switching [1].Nowadays, IGBT has been widely use in the power electronics application. It switches electric power in many modern appliances: electric cars, variable speed refrigerators, airconditioners, and even stereo systems with switching amplifiers.

This project focuses on the application of the IGBTs as the inverter for the three-phase output system. In conjunction with that, this project also focusing on the gate driver characteristic that will drives the IGBTs gate to switch and implement it on the testing.

## 1.2 Problem Statement

In order to operate a three phase load, an AC power supply is needed to supply the load. Therefore, an inverter is needed to convert the DC supply to the AC if the user desired to produce a three-phase output from the single phase supply.

Current control is often used to improve the performance and reliability for the motor drives. A common type for a current control is consisting MOSFETs and it is not capable of conducting a high DC voltage. By implementing the IGBT on the current control, a higher level of DC voltage can be applied to the drive.

## 1.3 Objectives

The objective of this project is to study the characteristic of the IGBT gate drive to the three phase output. Cost will be minimized to achieve minimal expenses throughout project.

There are a few objectives need to be achieved by the end of project completion:

- 1. To study and familiarize with off-the-shelf IGBTs drive.

- 2. To design and configure required interfacing from drive to the PXI controller.

- 3. To build IGBT inverter by using individual IGBTs pairs and the gate driver.

- To consider incorporate additional functionality such as overcurrent and overvoltage protection to the circuitry.

- To incorporate protection functions monitoring of IGBT drive (e.g. overvoltage / over-current) using NI LabVIEW (software programming and configuration)

- 6. To test and commission IGBT inverter to the motor.

# **CHAPTER 2**

#### LITERATURE REVIEW

## 2.1 Insulated-Gate Bipolar Transistor (IGBT)

#### 2.1.1 Introduction of IGBT

The insulated gate bipolar transistor or IGBT is a three-terminal power semiconductor device. IGBT is well known for high efficiency and fast switching period. IGBT acts as electric power switches and widely use electric cars, variable speed refrigerators, air-conditioners, and even stereo systems with switching amplifiers. [2]

The IGBT combines the simple gate-drive characteristics of the MOSFETs with the high-current and low-saturation-voltage capability of bipolar transistors by combining an isolated gate FET for the control input, and a bipolar power transistor as a switch, in a single device.

The IGBT is used in medium- to high-power applications such as switchedmode power supply, traction motor control and induction heating. Large IGBT modules typically consist of many devices in parallel and can have very high current handling capabilities in the order of hundreds of amps with blocking voltages of 6,000 V [3]. The IGBTs combines the positive attributes of Bipolar Junction Terminal (BJTs) and MOSFETs. BJTs have lower conduction losses in the on-state, especially in devices with larger blocking voltages, but have longer switching times, especially at turn-off while MOSFETs can be turned on and off much faster, but their on-state conduction losses are larger, especially in devices rated for higher blocking voltages. Hence, IGBTs has lower on-state voltage drop with high blocking voltage capabilities in addition to fast switching speeds.[3]

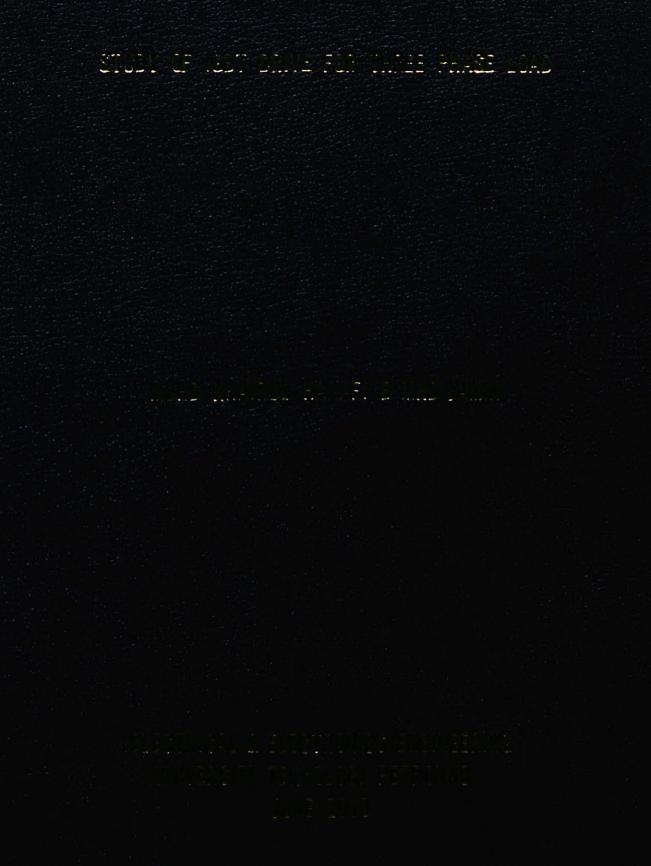

IGBT has a vertical structure as shown in Figure 2 below. This structure is quite similar to that of the vertical diffused MOSFET except for the presence of the p+ layer that forms the drain of the IGBTs.

This layer forms a pn junction (labeled J1 in the Figure 2), which injects minority carriers into what would appear to be the drain drift region of the MOSFET. The gate and source of the IGBTs are laid out in interdigited geometry similar to that used for the vertical MOSFET.

Figure 1: Physical structure of an IGBT

The IGBT structure shown in Figure 2 has a parasitic thyristor, which could latch up in IGBTs if it is turned on. The n+ buffer layer between the p+ drain contacts and the n+ drift layer, with proper doping density and thickness, can significantly improve the operation of the IGBTs in two important respects.

It can lower the on-state voltage drop of the device and shorten the turn-off time. On the other hand, the presence of this layer greatly reduces the reverse blocking capability of the IGBTs.

#### 2.1.2 IGBT Switching Characteristics.

An important performance feature of any semiconductor-switching device is its switching characteristics. User must really understand this characteristic. By having understanding this device switching characteristics, user can improve its utilization in the various applications.

The main performance switching characteristics of power semiconductor switching devices are the turn-on and turn-off switching transients in addition to the safe operating area (SOA) of the device

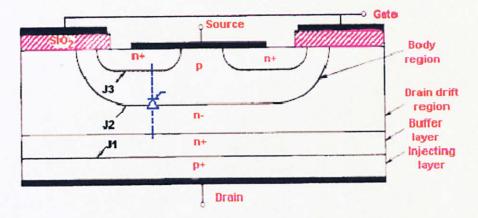

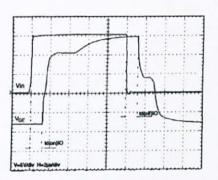

Since most loads are inductive in nature, which subjects devices to higher stresses, the turn-on and turn-off transients of the IGBTs are obtained with an inductive load test circuits as shown in Figure 4 below.

Figure 2: Inductive load test circuit

The load inductance is assumed to be high enough so as to hold the load current constant during switching transitions. The freewheeling clamp diode is required to maintain current flow in the inductor when the device under test is turned off.

#### 2.1.3 Turn-on Transients

The turn-on switching transients of IGBT are very similar to MOSFET since the IGBT is essentially acting as a MOSFET during most of the turn-on interval.

With gate voltage applied across the gate to emitter terminals of the IGBTs, the gate to emitter voltage rises up in an exponential fashion from zero to VGE(th) due to the circuit gate resistance (RG) and the gate to emitter capacitance (Cge). The Miller effect capacitance (Cgc) effect is very small due to the high voltage across the device terminals.[3]

Beyond VGE(th), the gate to emitter voltage continues to rise as before and the drain current begins to increase linearly as shown above. Due to the clamp diode, the collector to emitter voltage remains at Vdc as the IGBTs current is less than Io.

The gate to emitter voltage becomes temporarily clamped to VGE, Io. This means that the voltage required the IGBT current at Io. At this stage, the collector to emitter voltage starts decreasing in two distinctive intervals t<sub>fv1</sub> and t<sub>fv2</sub>.

The first time interval corresponds to the traverse through the action region while the second time interval corresponds to the completion of the transient in the ohmic region. During these intervals, the Miller capacitance becomes significant where it discharges to maintain the gate to source voltage constant.

When the Miller capacitance is fully discharged, the gate to emitter voltage is allowed to charge up to VG and the IGBT goes into deep saturation. The resultant turn on switching losses are shown in equation below:

The on energy loss is approximately estimated via this equation:

$$Eon = \frac{Vdc \ Io}{2} ton$$

where,

*Eon* = the on energy loss *Vdc* = DC Voltage *Io* = Current

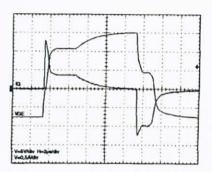

#### 2.1.4 Turn-off Transients

When a negative gate signal is applied across the gate to emitter junction, the gate to emitter voltage starts decreasing in a linear fashion. Once the gate to emitter voltage drops below the threshold voltage (VGE(th)), the collector to emitter voltage starts increasing linearly.

The IGBTs current remains constant during this mode since the clamp diode is off. When the collector to emitter voltage reaches the dc input voltage, the clamp diode starts conducting and the IGBTs current falls down linearly.

The rapid drop in the IGBT current occurs during the time interval tfi1, which correspond to the turn-off of the MOSFET. The tailing of the collector current during the second interval tfi2 is due to the stored charge in the n-drift region of the device.

This is due to the fact that the MOSFET is off and there is no reverse voltage applied to the IGBTs terminals that could generate a negative drain current so as to remove the stored charge.

The only way for stored charge removal is by recombination within the n-drift region. Since it is desirable that the excess carrier's lifetime be large so as to reduce the on-state voltage drop, the duration of the tail current becomes long.

This will result in additional switching losses within the device. This time increases also with temperature similar to the tailing effect in BJTs. A trade off between the on-state voltage drop and faster turn-off times must be made.

9

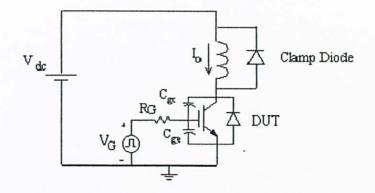

Figure 3: Equivalent circuit of the IGBTs

The removal of stored charge can be greatly enhanced with the addition of a n+ buffer layer, which acts as a sink for the excess holes and significantly shortens the tail time.

This layer has a much shorter excess carrier life time which results in a greater recombination rate within this layer. The resultant gradient in hole density in the drift region causes a large flux of diffusing holes towards the buffer region which greatly enhances the removal rate of holes from the drift region and shortens the tail time.[3]

This structure is referred to as Punch-Through (PT) IGBT while the structure without the n+ buffer region is referred to as Non Punch-Through (NPT) IGBT. The turn off energy loss, can be evaluated in a similar fashion as the turn-on losses.

#### 2.2 Inverter

#### 2.2.1 Inverter in Power Electronics

An inverter is an electrical device that converts direct current (DC) to alternating current (AC); the converted AC can be at any required voltage and frequency with the use of appropriate transformers, switching, and control circuits. An inverter is essentially the opposite of a rectifier. [4]

Static inverters have no moving parts and are used in a wide range of applications, from small switching power supplies in computers, to large electric utility high-voltage direct current applications that transport bulk power. Inverters are commonly used to supply AC power from DC sources such as solar panels or batteries.

The electrical inverter is a high-power electronic oscillator. It is so named because early mechanical AC to DC converters was made to work in reverse, and thus were "inverted", to convert DC to AC.

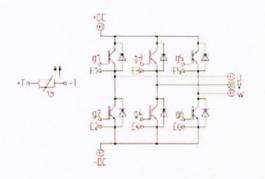

#### 2.2.2 Three Phase Inverter

Three-phase inverters are used for variable-frequency drive applications and for high power applications such as HVDC power transmission. A basic three-phase inverter consists of three single-phase inverter switches each connected to one of the three load terminals. [5] For the most basic control scheme, the operation of the three switches is coordinated so that one switch operates at each 60 degree point of the fundamental output waveform. This creates a line-to-line output waveform that has six steps.

The six-step waveform has a zero-voltage step between the positive and negative sections of the square-wave such that the harmonics that are multiples of three are eliminated as described above.

When carrier-based PWM techniques are applied to six-step waveforms, the basic overall shape, or *envelope*, of the waveform is retained so that the 3rd harmonic and its multiples are cancelled.

## 2.3 Gate Driver

Gate drivers are electronic circuits that apply correct power levels to insulated gate bipolar transistors (IGBTs).

With power-IGBTs, gate drivers can be implemented as transformers, discrete transistors, or dedicated integrated circuits (IC). They can also be integrated within controller ICs. Partitioning the gate-drive function of controllers that use pulse width modulation (PWM) improves controller stability by eliminating the high peak currents and heat dissipation needed to drive power-IGBTs at very high frequencies. [6]

With IGBTs, gate drivers serve as isolation amplifiers and often provide short-circuit protection. Because of their insulated gates, IGBTs require a continuous gate circuit in order to sustain gate current. There are four basic types of gate drivers. High-side gate drivers are used to drive IGBTs that are connected to a positive supply and not ground referenced (floating). Conversely, low-side gate drivers are used to drive IGBTs that are connected to a negative supply.

Dual gate or half-bridge gate drivers have both low-side and high-side gates. Three-phase drivers derive their name from the fact that they are used in three-phase applications. These drivers have three independent low-side and high-side referenced output channels. Typically, gate drivers have 1, 2, or 4 output channels. Their output voltage can be either inverted or non-inverted. [7]

## **CHAPTER 3**

# **METHODOLOGY OF PROJECT WORK**

## 3.1 Procedure Identification

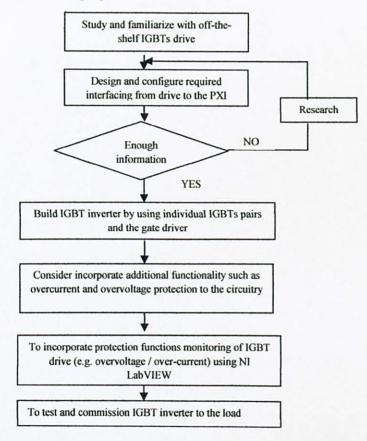

The process flow of the project will be done based on this simple flow below, which is applied throughout for this project.

Figure 4: The flow Chart of the process involved in FYP

## 3.2 Tools and Equipment Required

The tools and equipment which are required in this Final Year Project are a Windows based PC together with the programs such as Microsoft Office and National Instruments LABview software which is used to incorporate protection functions monitoring of IGBT drive and analyse the data obtained.

For the (Printed Circuit Board) PCB layout design, the EAGLE Layout Editor Software and the GC-Power Station Layout Editor Software were used for the designing process of fabricating the PCB board.

Apart from that, equipment needed basically would be data from the internet and other references. Microsoft Office programs include Microsoft Word used to type reports, Microsoft Excel to draw graphs and rearranging of data.

For the hardware, the SEMIKRON SKHI 23/12 (R) the dual IGBT driver and the SEMIKRON 39 AC12T4V1 the three-phase bridge inverter will be used.

#### 3.3 Project Works

#### 3.3.1 Intensive Literature Reviews

Intensive literature reviews has been done on the IGBT inverter application. There are two references that the author used for gaining knowledge on how to operate the IGBT inverter together with the gate driver. Resources from related books, internet and online journals have been accessed. The reviews are crucial to identify the method, tools and equipments that are needed for implementation of the device.

#### 3.3.2 Selecting a suitable off-the-shelf IGBT inverter and the gate driver

After considering several products that are available on the market, the most suitable gate driver and the IGBTs inverter for this project will be chosen. In conjunction with that, the author must also be familiarized with the device characteristics by studying and doing research from the product's user manual and from the journals.

#### 3.3.3 Fabricating and Troubleshooting

The fabrication of the unit will be the final step of this project. After fabrication completed, various testing will be done in order to make sure the expected result will gain and troubleshooting technique will be implement to overcome the encountered problems.

# **CHAPTER 4**

# **RESULTS AND DISCUSSION**

## 4.1 SEMIKRON SKHI 23/12 (R) Dual IGBT Gate Driver

#### 4.1.1 Device Description

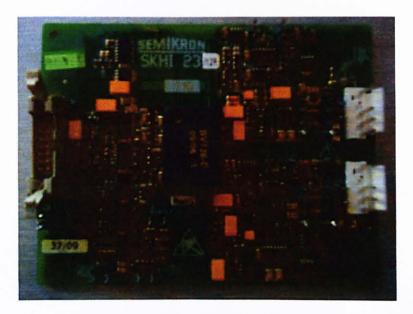

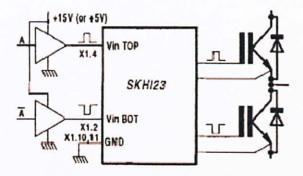

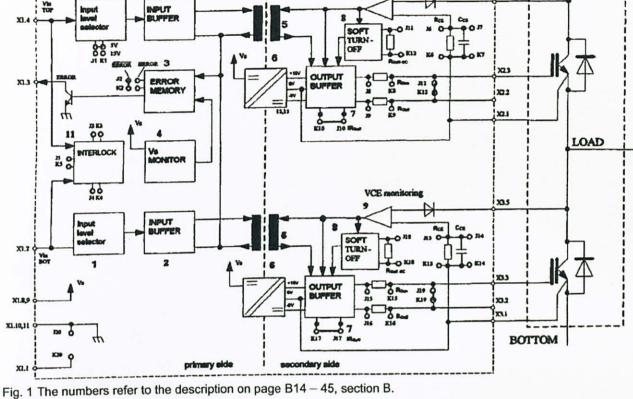

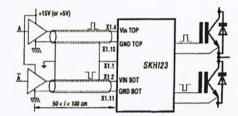

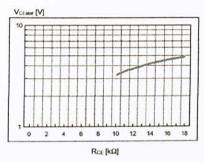

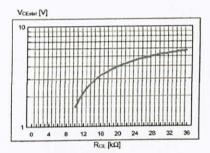

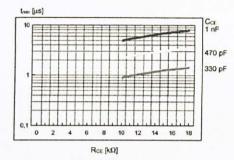

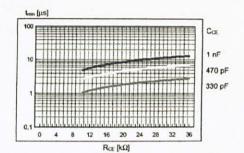

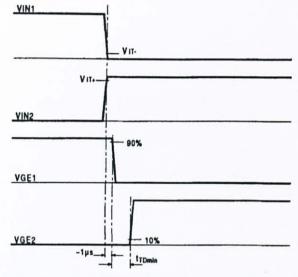

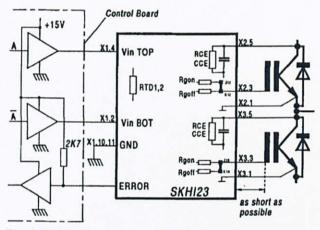

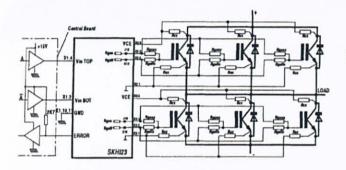

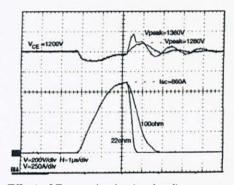

The SKHI 23/12 (R) Dual IGBT Gate Driver is used throughout for this project. SKHI 23/12 (R) device is a power semiconductor subsystem. By using SKHI 23/12 (R) driver, it can drives all SEMIKRON IGBTs with V<sub>CES</sub> up to 1200V. [8]

For this project, three units of the SKHI 23/12 gate driver will be implementing on the IGBTs inverter. Figure below shows this gate driver physical setup.

Figure 5: Top View

Figure 6: Side View

Figure 7: SKHI 23/12(R) Dual IGBT Gate Driver

Here are this gate driver features:

✓ Input Level Selector

The SKHI 23 has an input level selector circuit for two different levels. It is preset for CMOS (15V) level, but can be changed by the user to HCMOS (5V) [8]

✓ Interlock

An INTERLOCK circuit prevents the two IGBTs of the half bridge to switchon at the same time.

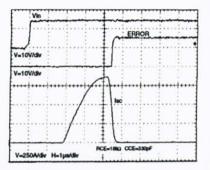

#### ✓ Error Memory

The ERROR MEMORY blocks the transmission of all turn-on signals to the IGBT if either a short circuit or malfunction of Vs is detected. During that time ,a signal is sent to the external control board through an open collector transistor.

#### ✓ Vs Monitor

This feature makes sure that the Vs actual is not below 13V and if the Vs is below 13V, a signal will be sent to the user.

#### ✓ Ferrite Transformer

With a FERRITE TRANSFORMER the information between primary and the secondary may flow in both directions and high levels of dc/dt and isolation are obtained.[8]

#### ✓ DC/DC converter

A high frequency DC/DC CONVERTER avoids the requirement of external isolated power supplies to obtain the necessary gate voltage .An isolated ferrite transformer in half-bridge configuration supplies the necessary power to the gate of the IGBT. With this feature, user can use the same power supply used in the external control circuit, even if user using more than one SKHI 23 such that in this project in three phase configuration.[8]

#### ✓ Output Buffer

The correct current to the gate of the IGBT will be control by the OUTPut BUFFER. If these signals do not have sufficient power, the IGBT will not switch properly.

#### ✓ Reset

When there is zero value for both of the input Vin, the RESET is performed

This gate driver needs to be powered up by 15V which is suitable for this project. Figure below shows how to connect the SKHI 23/12 (R) by using the short cables.

Figure 8: Connecting the SKHI 23/12 (R) with short cables.

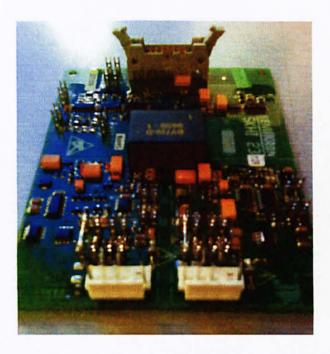

## 4.2 SEMIKRON SKiiP 39ACT4V1 Three-phase Bridge Rectifier

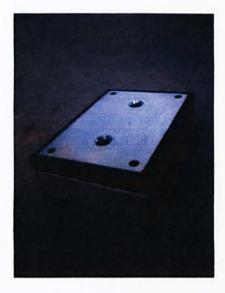

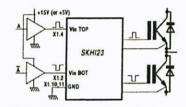

SEMIKRON SKiiP 39ACT4V1 is a trench 4 IGBTs build-up inverter. In this project, the SKiiP 39ACT4V1 will use to invert the DC supply up to 240V AC in order to produce the three-phase output.

Figures below show the physical view of the SEMIKRON SKiiP 39ACT4V1 unit.[9]

Figure 9: SEMIKRON SKiiP 39ACT4V1 physical view.

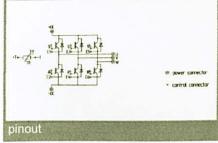

Figure below shows the block diagram of this bridge rectifier. The author had recognized all of the pins on the device and assigned each corresponding pin on the bridge inverter to the gate driver for the interfacing steps.

power connector

control connector

Figure 10: The block diagram of the bridge rectifier

## 4.3 Drafting the Block Diagram Connection of devices

For the first step into this project, the author had done a study about the interconnection between the gate driver and the inverter. The basic block diagram of the connection also has been constructed in order to be the guide of the next step which is the interfacing the devices together.

# 4.4 Plug Connectors PCB Driver

For the connection of the plug connectors to the PCB driver, the author had verified the types of connection that will use for the connection. Table 4.1 below shows the types of connection used:

| Driver Type    | Input Connector<br>(Primary Side to Controller) |                           | Output Connector<br>(Secondary Side to IGBT) |                       |

|----------------|-------------------------------------------------|---------------------------|----------------------------------------------|-----------------------|

|                | Male                                            | Female                    | Male                                         | Female                |

| SKHI 23/12 (R) | DIN 41651<br>(14 pins)                          | plug 14 pins<br>DIN 41651 | MOLEX<br>Series 41791<br>(5 pins)            | MOLEX<br>Series 41695 |

Table 1: Plug Connectors

# 4.5 Fabricating the PCB board for the interfacing between gate driver and the IGBTs

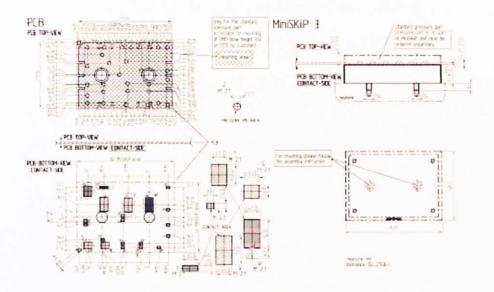

In order to do the interfacing between the gate driver and the IGBTs, the author must design a PCB board. The designed PCB board should take account all of the connection points between the gate driver and the inverter via the connectors that will be connected to the PCB board.

For the first phase of the designed process, the author had decided to use the EAGLE Layout Editor Software for the PCB layout software. The design should consider all of the pins on the bridge inverter in order to make this device fully operate.

## 4.5.1 EAGLE Layout Editor Software Designing Process

By using EAGLE Layout Editor Software, the process of designing the layout of the PCB board is been designed. Firstly, the entire dimension between the pins on the gate inverter is measured.

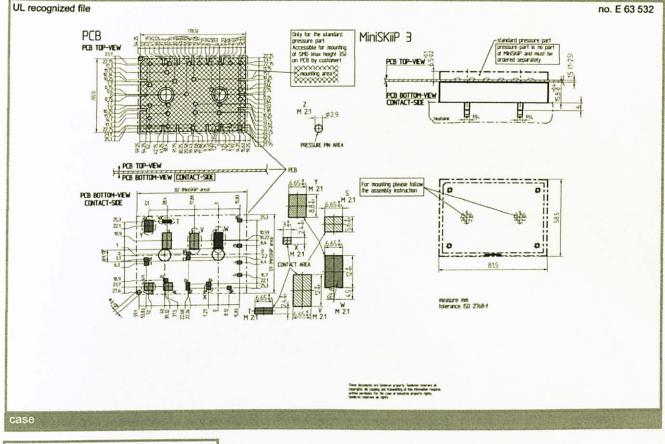

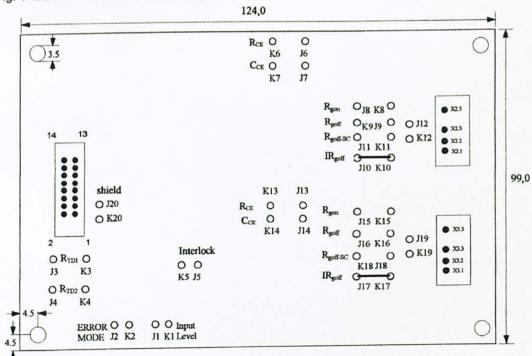

The details of the measurement can be getting from the SEMIKRON SKiiP 39ACT4V1 data sheet. Figure below shows the dimension of the inverter.

Figure 11: The Layout Dimension of inverter

Then after considering the dimension of the desired designed PCB board, the new project is created in the EAGLE Layout Editor.

| View Options Windo        | NAME OF TAXABLE PARTY OF TAXAB | Empty                           |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| b Open                    | Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Project                         |

| Open recent projects      | Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Lise the contex                 |

| Save all                  | Board ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | menu to create<br>new schematic |

|                           | D Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | or board files                  |

| Close project<br>Exit Alt | +X 😴 CAM Job                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | within this project.            |

| 😧 🔄 examples              | E W UP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

|                           | Script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

|                           | F Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

Figure 12: Creating a new project in editor menu

In this designing process, the author had the problem of choosing the correct block set in the library that is matching with the pins on the inverter.

After discussing with the PCB Lab Technician, Mr. Isnani and the supervisor, Mr. Saiful Azrin bin Mohd Zulkifli, the author had decided to choose the designation of the pins on the PCB is by using the pinhead block set that is available in the library of EAGLE Layout Editor.

By choosing to use the pinhead block in the library, the author had to consider placing a 56 set of pinheads on the design PCB board. To add the component on the schematic, the author use the add mode on the schematic menu.

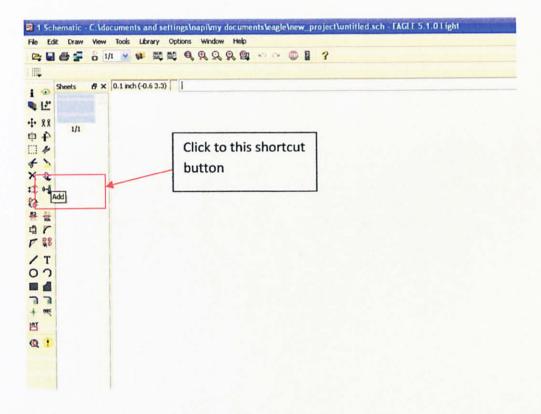

Figure 13: Add menu on the schematic

Then in the library menu, the pin header block set was choose .The pin header block set name is PINHD-1X1 PINHEADER.

| PINO-112<br>PINO-124<br>PINO-124<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-125<br>PINO-1 | PIN HEADER<br>PIN HEADER |         | PIN HEADER<br>Package: 1201<br>PIN HEADER | MALVE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------|-------|

| earch 🗹 Sm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ds 🗹 Description                                                                                                                                                                                                                                                                                                                             | Preview |                                           |       |

Figure 14: The Pin header component menu

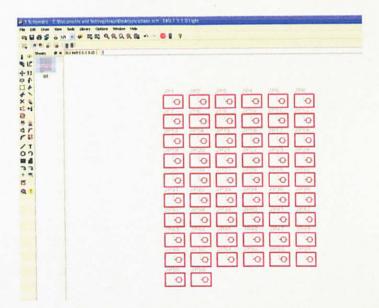

In the schematic view, all of the 56 units of pin headers were placed on the window. The view of the 56 units of pin headers can be seen as in Figure 15.

Figure 15: 56 units of pin headers in the schematic view

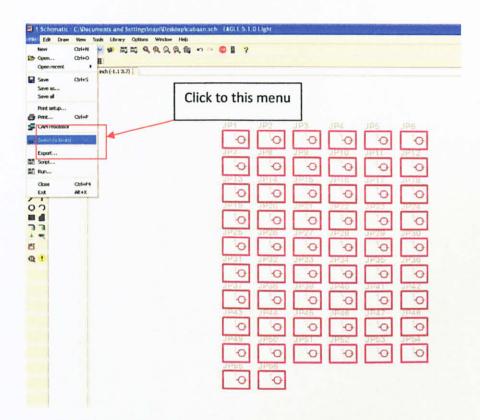

In order to place each unit of the pin header correctly according to the dimension of the actual pins on the inverter, from this schematic view the author had to use the switch to board menu from the layout editor menu.

Figure 16: Switch to board menu

After switching to board view, then the step of locating each of the pin headers can be implementing. Before proceeding, the author had set the grid setting in the View > Grid menu in the board view. The setting for the board view can be seen in Figure 17.

| Display  | / Colorise starts | Style          |

|----------|-------------------|----------------|

| O or     | n 💿 Off           | O Dots 💿 Lines |

| ize:     | 0.00 <b>1</b>     | mm 🖌 Finest    |

| ultiple: | 1                 |                |

| lt:      | 0.001             | mm 🌱 Finest    |

Figure 17: Grid Setting

For the grid setting, the grid size is set to 0.001 mm and the Alt is set to 0.001 mm. This setting will be applied for throughout of this design.

Then, by referring to the actual dimension of the pins on the inverter from the schematic diagram, the pin headers were placed on the board view. Figure 18 below shows the process of plotting the pin headers on the board.

Figure 18: Plotting pin headers on the board

After plotting all of the 56 points of the pin headers, Figure 19 below shows the complete board.

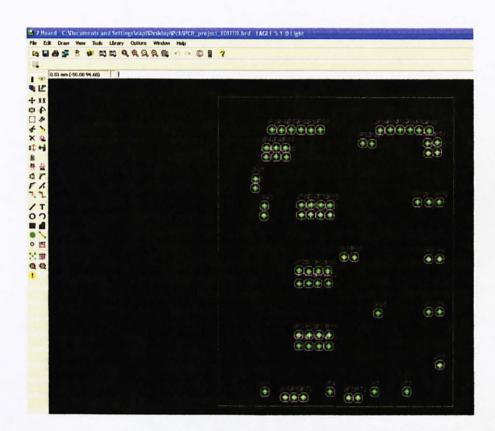

Figure 19: Completed Board

## 4.5.2 Problem Encountered

The designed PCB board is not fully functional due to the plotting error on the design stage of this board.

Some of the pins on the inverter are not touching the PCB pinheads; therefore the author had to redesign it again by considering the main problem.

Figure 20 below shows the area of error in the design. The error occurred due to the precision during the plotting process.

Figure 20: Error on the Board

Thus, to over come this error the author had decided to use another PCB layout editor that is more accurate and easy to use and detect the error during the design process.

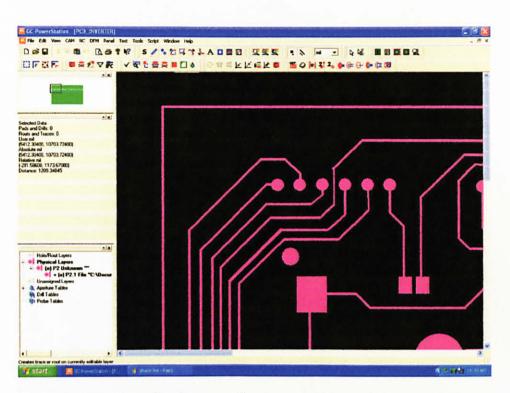

## 4.5.3 GC-Power Station Layout Editor Software PCB Designing Process.

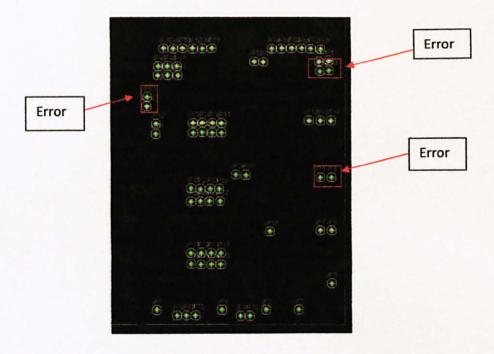

Because of the author's first design of the PCB board was not functional due to the error in the pin headers plotting process, therefore the author had decided to use another PCB layout editor that is more accurate and easy to use.

Firstly, a new project file is created. The layout of the GC-Power Station software can be seen as in Figure 21.

Figure 21: The Open New File View

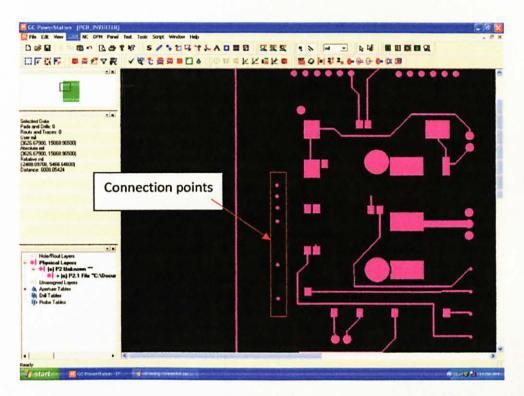

After that all of the pins point on the inverter were designed and placed correctly on the board. Then the process of placing the pin point for the connection between the E-connector and the E-points on the inverter (E1, E2, E3, E4, E5, and E6) was done. Figure 22 below shows the process of drawing the connection points.

Figure 22: Drawing the connection points on the board

These connection points will make the process of connecting between the connector point and the E-points on the inverter easier. Moreover, by using this technique the author can easily detecting and correcting the error on the connection route.

Then the points will be connected to the connector points via the connection points made. Figure 23 below shows the completed connection between the connection points and the connector's points.

Figure 23: The Completed connection between E-connectors and E-points

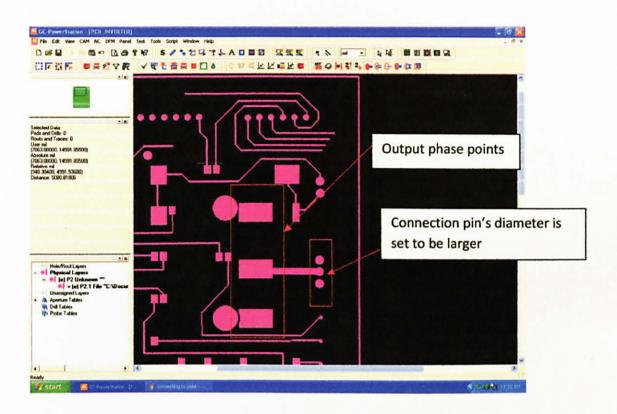

The same technique was applied to other points that were G-points, T-points, DC+ and DC-.For the output phase points, the design is slightly different from this technique. This is due to the capacity for the output phase voltage and current are higher. Figure below shows the route settings of the connection route.

| PAD Attril<br>6659.09100, | butes  <br>5967.99000) mil |             |          | Move   |

|---------------------------|----------------------------|-------------|----------|--------|

| + (e) P2.1 File           | "C:Vocuments a             | nd          | -        |        |

| Aperture:                 | a001.166                   | Select From | Aperture | Tables |

| Round                     | ▼ D1144                    | Net 0       | Туре:    | M.     |

|                           | Net Name:                  | -           | -        |        |

| Diameter:                 | 137.795000                 | mi          |          |        |

|                           |                            |             |          |        |

|                           |                            |             |          |        |

|                           |                            |             |          |        |

| Apply to a                |                            |             |          |        |

| OK                        | Cancel                     | Units       | 1        | Help   |

Figure 24: The route setting

Figure 25 below shows the process of drawing the output connection point. For the connection points, a bigger diameter size was chosen.

Figure 25: The connection of output phase points

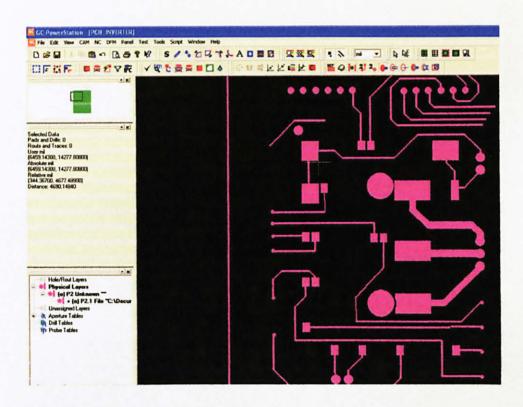

Because of the output phase carry the highest current and voltage on the board, therefore the route of the connection between the connection points was set to the setting as same as Figure 26 below.

| Properties   |                                                  | 2010.10     | ? 🕻         |

|--------------|--------------------------------------------------|-------------|-------------|

|              | 902.67600, 8046.84100)<br>3.34100, 8250.94300) m |             | Move        |

| + (e) P2.1 F | File "C:\Documents and                           |             | 0           |

| Aperture:    | a001.142                                         | exFion Aper | tian Tables |

| Round        | - D1120 N                                        | et 0        |             |

|              | Net Name:                                        |             |             |

| Diameter:    | 100.000000                                       | mil         |             |

| F Apoly II   |                                                  |             |             |

| OK           | Cancel                                           | Units       | Help        |

Figure 26: Output route line setting

The diameter is set to be 100 mil. This setting will make the route to be able to conduct the higher level of output voltage and current. Then, the completed tracks of the output phase route were done as shown in Figure 27 below.

Figure 27: The complete route for output phase connection.

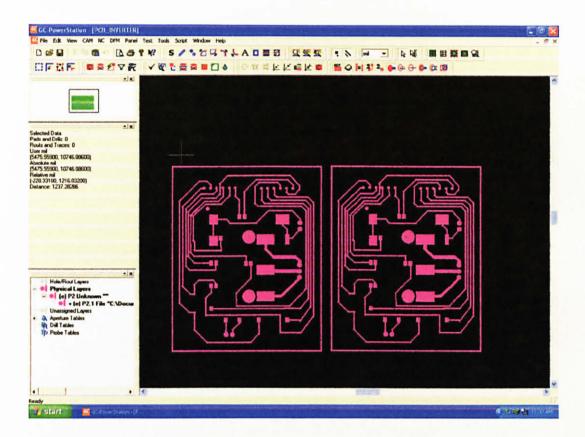

Finally, all the connection points then were connected to the correct points on the PCB layout. Figure 28 below shows the completed design of this project PCB design.

Figure 28: The completed PCB board design

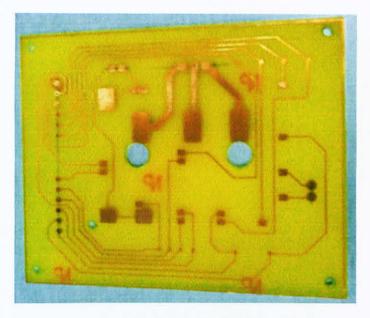

Figure 29 below shows the PCB board that was finally fabricated. This board then will be placed on top of the IGBT inverter and will be screwed with the m4 screw.

Figure 29: The fabricated PCB board

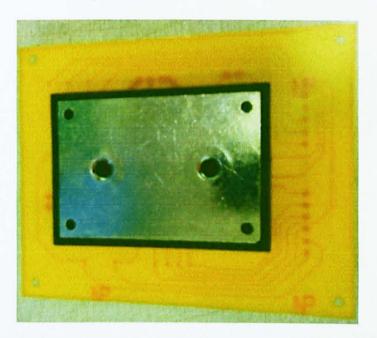

Figure 30: Connecting the IGBT inverter with the PCB board

## 4.6 Interfacing the Gate Driver and the IGBT Inverter via the PCB board

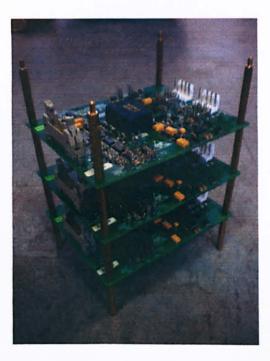

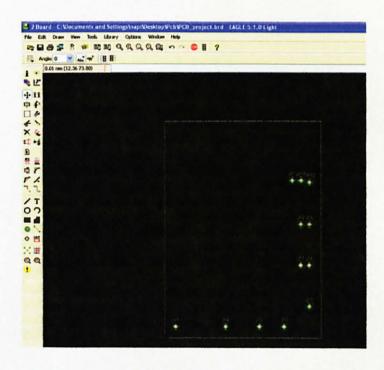

The next step of this project is the interfacing between the Gate Driver and the IGBT Inverter via the fabricate PCB board. In this phase, all of the connections between the hardware were make sure to be correct before proceeding with the next phase.

Figure 31 below shows the initial setup of this project hardware.

Figure 31: Side View of hardware initial setup

Figure 32: Front View of hardware initial setup

## **CHAPTER 5**

## **CONCLUSION AND RECOMMENDATION**

## 5.1 Conclusion

This project needs a very careful study and consistent works. There will be many obstacles that need to be handled and overcome in completing this project. However with the guidance from the supervisor, this project can be completed successfully as scheduled. Implementing knowledge from the class will be different from the knowledge gain from the hands-on experience.

In this project, the testing part cannot be implementing yet. This is due to the fact of time limitation of this project. However, the author had managed to get a clear view of this project's process and procedure involves in completing this project. The author also had managed to complete the important steps involved in this project which was the initial setup of the gate driver and the IGBT inverter which can help other semester student to continue the next stages.

## 5.2 Recommendation

For this semester, the author has to work very hard in order to complete this FYP project on schedule. However, flexibility is important for author to proceed with any modification to accommodate improvement for the problem encountered. For improvement of this project, the author suggests that:

### ✓ Exposure To The Product's Data Sheet

Student should be familiarizing with the product's data sheet. From this product's data sheet or product's manual, a lot of information about the product can be found such as the operating conditions, electrical characteristics and the schematic diagram.

### ✓ Meeting With Supervisor

From the meeting, the author will have opportunity to ask and get advices from the supervisor. This will help author a lot in completing this project successfully according to the schedule.

## ✓ Neater Design

The author plans to install the housing part for the device. This will prevent it from dust and exposed it to the potential hazard.

## REFERENCES

- [1] Synchronous motor by http://en.wikipedia.org/wiki/Synchronous\_motor

- [2] IGBT Basic by http://en.wikipedia.org/wiki/Insulatedgate\_bipolar\_transistor#18/12/2009

3:47:18 PM

- [3] IGBT description http://ocw.mit.edu/NR/rdonlyres/Electrical-Engineeringand-Computer-Science/6-012Fall-2009/781BD339-C575-45EF-A21F-F5E4C48D8E32/0/MIT6\_012F09\_lec14\_inverter.pdf

- [4] IGBT Basic: http://www.powerdesignersusa.com/InfoWeb/design\_center/articles/IGBTs/ig bts.shtm

- [5] IGBT gate driver by: http://www.rell.com/resources/RellDocuments/SYS\_25/Microsemi-Tutorial-IGBT-APT0201.pdf

- [6] Inverter by 6.012 Microelectronic Devices and Circuits Fall 2009

- [7] Inverter design www.discovercircuits.com/C/co-dctoac.htm

- [8] SkiiP\_39AC12T4V1\_101209 Datasheet

- [9] SKHI\_23\_12R\_101209 Datasheet

# APPENDICES

## **APPENDIX:** Gantt chart

| No. | Detail/Week                                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 1 | .6 | 17 |

|-----|------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|------|----|----|

| 1   | Component Purchasing and Researching           |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 2   | Submission of Progress Report 1                |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 3   | PCB Designing and Fabrication                  |   | _ |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 4   | Submission of Progress Report 2                |   |   |   |   |   |   |   |   |   |    |    |    |    |    | EXAN |    |    |

| 5   | Poster Exhibition (ElectrEx)                   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 6   | Submission of Draft Report                     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 7   | Submission of Dissertation (softbound)         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 8   | Oral Presentation                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

| 9   | Submission of Project Dissertation (Hardbound) |   | _ |   |   |   |   |   |   |   |    |    |    |    |    |      |    |    |

Progress

Suggested milestone

MiniSKiiP<sup>®</sup>3

3-phase bridge inverter

### SKiiP 39AC12T4V1

## Features

- Trench 4 IGBT's

- Robust and soft freewheeling diodes in CAL technology

- Highly reliable spring contacts for electrical connections

- UL recognised file no. E63532

## **Typical Applications**

- · Inverter up to 50 kVA

- Typical motor power 30 kW

## Remarks

- V<sub>CEsat</sub>, V<sub>F</sub>= chip level value

- Case temp. limited to  $T_c = 125^{\circ}C$ max. (for baseplateless modules  $T_c = T_s$ )

- product rel. results valid for T<sub>j</sub>≤150 (recomm. T<sub>op</sub> = -40 ... +150°C)

- For short circuit: Soft R<sub>Goff</sub> recommended

| Absolute         | Maximum Ratings                                                             | T <sub>s</sub> =        | = 25 °C, unless otherwis | e specified |

|------------------|-----------------------------------------------------------------------------|-------------------------|--------------------------|-------------|

| Symbol           | Conditions                                                                  |                         | Values                   | Units       |