# EDUCATIONAL PROCESSOR

By

# NIK ADLI HAKIMI BIN NIK MOHAMAD SHUKRI

DISSERTATION

Submitted to the Electrical & Electronics Engineering Programme in Partial Fulfilment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

> > © Copyright 2011

by

Nik Adli Hakimi Bin Nik Mohamad Shukri, 2011

# **CERTIFICATION OF APPROVAL**

# **EDUCATIONAL PROCESSOR**

by

# NIK ADLI HAKIMI BIN NIK MOHAMAD SHUKRI

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved:

Patrick Sebastian Project Supervisor

# UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

September 2011

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

diten.

Nik Adli Hakimi Bin Nik Mohamad Shukri

# ABSTRACT

This report discusses about the overview of the chosen project, which is an Educational Processor (EduCPU). The objective of this project is to develop a simple processor using TTL logic gates and also to develop simulation software for educational purpose. The software is responsible for sending instruction codes to the simple processor through serial communication in order to execute the instruction. The software written is also capable of simulating the behaviour of the simple processor. This educational processor would be used as a learning tool in Computer System Architecture course in in Universiti Teknologi PETRONAS (UTP) to assist students in understanding about computer system architecture. In order to complete this project, the scope of study basically will cover the computer system architecture and details about Central Processing Unit (CPU). The instruction format and CPU data path design both are based on MIPS architecture processor. The methodologies that are involved in this project are design and validation phase, constructing the hardware, and programming the user interface to interact with the educational processor.

# ACKNOWLEDGEMENTS

Firstly, I give my utmost gratitude to ALLAH the Almighty for his uncountable graces upon me and for the successful completion of this project in due course of time.

I would like to express the appreciation to my supervisor, Mr. Patrick Sebastian, Lecturer of Electrical & Electronics Department, UTP. The supervision and continuous support that he gave truly helped me throughout completing this project. He provided lots of guide, sample codes, and teaching me concepts in order to successfully complete this project. He also helped me in correcting various documents of mine with attention and care.

Lastly, great appreciation to my friends, who always helped me and giving me support when I needed it. Not to forget my appreciation to all UTP lecturers, students, staff, friends and to all whose their names are not mentioned here but they provided help directly or indirectly in completing my project.

# TABLE OF CONTENTS

| ABSTRACT                               | iv   |

|----------------------------------------|------|

| ACKNOWLEDGEMENTS                       | v    |

| TABLE OF CONTENTS                      | vi   |

| LIST OF FIGURES                        | ix   |

| LIST OF TABLES                         | xi   |

| LIST OF ABBREVIATIONS                  | .xii |

| CHAPTER 1 INTRODUCTION                 | 1    |

| 1.1 Background of Study                | 1    |

| 1.2 Problem Statement                  | 1    |

| 1.2.1 Problem Identification           | 1    |

| 1.2.2 Significance of Project          | 2    |

| 1.3 Objective and Scope of the Project | 2    |

| 1.3.1 Objectives                       | 2    |

| 1.3.2 Scope of the Project             | 3    |

| 1.4 Relevancy of Project               | 3    |

| 1.5 Feasibility of Project             | 3    |

| Chapter 2 LITERATURE REVIEW            | 4    |

| 2.1 Introduction to Processors         | 4    |

| 2.2 Instruction Set Architecture       | 4    |

| 2.3 Introduction to MIPS Architecture  | 5    |

| 2.4 CPU Functional Units               | 6    |

| 2.4.1 Program Counter (PC)             | 7    |

| 2.4.2 Instructions Memory              | 7    |

| 2.4.3 Instruction Register             | 7    |

| 2.4.4 Register File                                        |

|------------------------------------------------------------|

| 2.4.5 Random Access Memory (RAM)                           |

| 2.4.6 Control Logic                                        |

| 2.4.7 Arithmetic and Logic Unit (ALU)                      |

| 2.4.8 Address Bus and Data Bus                             |

| Chapter 3 METHODOLOGY                                      |

| 3.1 Project Flowchart                                      |

| 3.2 Research Methodology10                                 |

| 3.3 Instruction Set Design                                 |

| 3.4 Tools Required12                                       |

| 3.5 Instructions List                                      |

| 3.6 Datapath14                                             |

| 3.7 Graphical User Interface14                             |

| 3.8 Project Duration14                                     |

| Chapter 4 RESULTS AND DISCUSSION15                         |

| 4.1 Graphical User Interface                               |

| 4.2 Compiling20                                            |

| 4.2.1 R-Type20                                             |

| 4.2.2 I-Type                                               |

| 4.2.3 J-Type                                               |

| 4.3 Simulation: Test Code 1 – Adding values                |

| 4.4 Simulation: Test Code 2 – Multiplying values           |

| 4.5 Transmitting machine code through serial communication |

| 4.6 Hardware                                               |

| 4.7 Discussion                                             |

| Chapter 5 CONCLUSION & RECOMMENDATIONS                     |

| 5.1 Conclusion                                             |

| 5.2 Recommendations                        | .35  |

|--------------------------------------------|------|

| APPENDIX A PROJECT GANTT CHART             | . 37 |

| APPENDIX B – DATAPATH DESIGN               | . 39 |

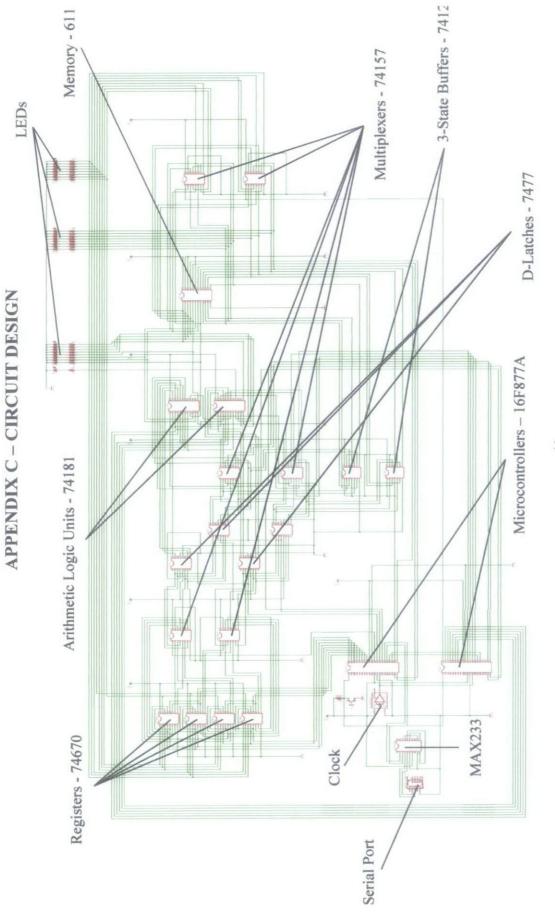

| APPENDIX C – CIRCUIT DESIGN                | . 40 |

| APPENDIX E – PERL SOURCE CODE              | . 44 |

| APPENDIX F – VISUAL BASIC 2010 SOURCE CODE | .47  |

# LIST OF FIGURES

| Figure 1: MIPS R-Type instruction format                               | 5 |

|------------------------------------------------------------------------|---|

| Figure 2: MIPS I-Type instruction format                               | 5 |

| Figure 3: MIPS J-Type instruction format                               | 6 |

| Figure 4: Project Flowchart                                            | 9 |

| Figure 5: Instruction Format Design                                    | 1 |

| Figure 6: R-Type instruction format                                    | 1 |

| Figure 7: I-Type instruction format                                    | 1 |

| Figure 8: J-Type instruction format                                    | 1 |

| Figure 9: EduCPU Main View                                             | 5 |

| Figure 10: Example of code with errors                                 | 6 |

| Figure 11: Code without any syntax error                               | 7 |

| Figure 12: EduCPU Datapath View                                        | 7 |

| Figure 13: Register View                                               | 8 |

| Figure 14: Memory View                                                 | 8 |

| Figure 15: Help Window                                                 | ) |

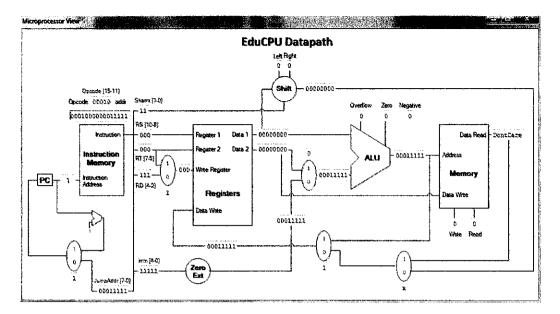

| Figure 16: Test Code 1, Line 1 Datapath View                           | 2 |

| Figure 17: Test Code 1, Line 1 Register View                           | 2 |

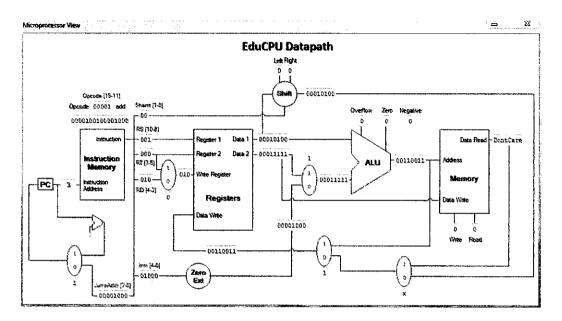

| Figure 18: Test Code 1, Line 3 Datapath View                           | 3 |

| Figure 19: Test Code 1, Line 3 Register View                           | 3 |

| Figure 20: Test Code 1, Line 4 Memory View                             | 1 |

| Figure 21: Reg $3 = \text{Reg } 1 + \text{Reg } 3$                     | 5 |

| Figure 22: Registers view after line 4 is transmitted                  | 5 |

| Figure 23: Registers view after line 5 is transmitted                  | 5 |

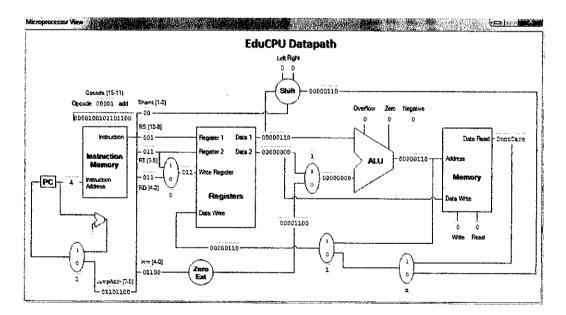

| Figure 24: Datapath view after transmitting line 6                     | 7 |

| Figure 25: Main view after transmitting line 4 for second time27       | 7 |

| Figure 26: Datapath view after transmitting line 4 for second time28   | 3 |

| Figure 27: Registers view after transmitting line 4 for second time    | ; |

| Figure 28: Datapath view after transmitting the last line of the code  | ) |

| Figure 29: Registers view after transmitting the last line of the code | ) |

| Figure 30: Main view after transmitting the last line of the code      | ) |

| Figure 31: Connection between PC and hardware                          | ) |

| Figure 32: Choosing the correct serial port  |  |

|----------------------------------------------|--|

| Figure 33: Hardware of Educational Processor |  |

# LIST OF ABBREVIATIONS

| RISC   | Reduced Instruction Set Computing                     |

|--------|-------------------------------------------------------|

| CISC   | Complex Instruction Set Computing                     |

| MIPS   | Microprocessor without Interlocked Pipeline<br>Stages |

| CPU    | Central Processing Unit                               |

| RAM    | Random Access Memory                                  |

| EPROM  | Erasable Programmable Read-only memory                |

| PC     | Program Counter                                       |

| CSA    | Computer System Architecture                          |

| TTL    | Transistor-transistor Logic                           |

| OPCODE | Operation Code                                        |

.

# CHAPTER 1 INTRODUCTION

This chapter discusses about the introduction to this project. It covers the background of study which discusses the background knowledge involved in this project. The problem statement and the reasons that lead to the implementation of this project are also discussed in this chapter.

# 1.1 Background of Study

This project is aimed to develop a simple educational processor which would be used as a teaching material in Computer System Architecture class. The main objective of this project is to provide an opportunity for the students taking this course to understand and examine how a processor executes an instruction. Students will be able to interactively interact with the basic of the processor to enhance students' learning environment.

The knowledge required in this project is the knowledge of digital electronics and also knowledge about computer system architecture. This project also requires the knowledge in microcontroller since this educational processor would be interfaced to a computer using a microcontroller via serial communication. In order to write the program that would be used to interface the educational processor and computer, knowledge about programming using C, Perl, and Visual Basic is also needed.

### **1.2 Problem Statement**

# **1.2.1** Problem Identification

The processor is one of the most important parts of a computer system. The development of the processor has evolved over the years. In 1945, a mathematician John Von Neumann outlined the design of a stored-program computer which became the primary design of most modern Central Processing Units (CPU) [1]. Most of the

processor designs now are very sophisticated and complex compared to its earlier development stage. This makes the learning process of how processors actually work becomes increasingly difficult.

The Electrical and Electronics Engineering students in Universiti Teknologi PETRONAS especially those taking Computer Systems as their major have the chance to learn about computer system through Computer System Architecture course. The course exposes the students to lectures and also lab assignments in order for the students to understand the basics of computer system architectures, including on how processors work.

The course does not focus on any specific computer architecture, but instead exposes the students to the general processor designs with MIPS architecture processor briefly explained. The course itself is also quite theoretical which makes it harder for the students to fully understand the concepts of processors.

# 1.2.2 Significance of Project

This project would give an opportunity to the Computer System Architecture students to explore and examine at the gate level about a MIPS-based architecture processor datapath. The students would be able to observe exactly what happens at each stage in the processors and how each logic device interact with each other in order to complete a CPU instruction.

# 1.3 Objective and Scope of the Project

#### 1.3.1 Objectives

The main objective of this project is to develop a simple MIPS based architecture processor as learning and teaching tool in Computer System Architecture course.

The sub objectives of the project are listed as the following:

To help students understand more about how a processor works.

- To construct the PCB boards and validate the prototype.

- To develop a software with a graphic user interface in order to give commands to the designed processor.

## 1.3.2 Scope of the Project

This project will start with literature reviews related to processors with MIPS architecture to fully understand how processors with MIPS architecture work. After that, the simple processor will be designed in design phase before actually implementing the design on real hardware. The software will also be designed in the design phase in order to let the processor communicate with a connected computer. Then, the prototype will be developed where the data path hardware is implemented using TTL logic gates designed during design phase. Further testing will be carried out to make sure the processor works by interfacing the processor with a computer.

# 1.4 Relevancy of Project

This educational processor will follow the format of MIPS architecture commands that is included in Computer System Architecture course syllabus. Instead of learning only in theory about how MIPS processors work, students taking Computer System Architecture course will also have the opportunity to clearly see how MIPS processors work. The educational processor will be combined with graphical user interface software. This project will significantly improve the students' understanding about processors, especially MIPS processors.

## 1.5 Feasibility of Project

The whole project will be done in two semesters. This includes three main areas which are research, development, and also improvement of the design. The software development tools (Microsoft Visual Studio 2010, Perl, MPLAB IDE, and PICKit) are available. The components needed for hardware implementation such as TTL gates and microprocessors are also readily available in the lab. Based on the description above, it is very clear that this project is feasible to be completed within the time frame.

# CHAPTER 2 LITERATURE REVIEW

This chapter discusses about the theories and paperwork reviews related to this project. Besides that, details on the educational processor's architecture and data path design would also be discussed in this chapter.

#### 2.1 Introduction to Processors

The processor or CPU is the portion of a computer system that carries out the instructions of a computer program, and is the primary element carrying out the functions of the computer or other processing device. The CPU carries out each instruction of the program in sequence, to perform the basic arithmetical, logical, and input/output operations of the system [2]. This term has been in use in the computer industry at least since the early 1960s [1]. The form, design and implementation of CPUs have changed dramatically since the earliest examples, but their fundamental operation remains much the same.

## 2.2 Instruction Set Architecture

The Instruction Set Architecture is the part of the processor that is visible to the programmer or compiler writer. It is an abstract model of a computer that describes what it does, rather than how it does it (functional definition). So, it can be said that the instruction set architecture and the instructions available in the processor determine the processor capabilities and performance [3]. The ISA also serves as the boundary between software and hardware.

The ISA varies from machine to machine. Instructions are classified by format and the number of operands they take. The three basics instruction types are data movement which copies data from one location to another, data processing which operates on data, and flow control which modifies the order in which instructions are executed. Instruction formats can take zero, one, two or three operands. It depends on how many bits are used to represent the whole instructions.

# 2.3 Introduction to MIPS Architecture

MIPS architecture is a 32-bit RISC instruction set architecture developed by MIPS Computer System (now known as MIPS Technologies). MIPS architecture is designed for high performance. To allow the user to get maximum performance, the complexity of individual instructions is minimized. This allows the execution of these instructions at significantly higher speeds [5]. MIPS instructions are classified into groups according to their coding formats [4]. These formats are:

• R-Type (register-to register instruction)

This group contains all instructions that do not require an immediate value, target offset, memory address displacement, or memory address to specify an operand. This includes arithmetic and logic with all operands in registers, shift instructions, and register direct jump instructions.

• I-Type (immediate operand)

This group includes instructions with an immediate operand, branch instructions, and load and store instructions. In the MIPS architecture, all memory accesses are handled by the main processor, so coprocessor load and store instructions are included in this group.

• J-Type (branch/jump instruction)

This group consists of the direct jump instructions. These instructions require a memory address to specify their operand.

Figures below describe the format of 32-bit MIPS instruction formats – R-Type, I-Type, and also J-Type instructions.

| 31 26      | 25 | 21  | 20 | 16  | 15 | 11    | 10 | 6   | 5       | 0      |

|------------|----|-----|----|-----|----|-------|----|-----|---------|--------|

| Opcode (6) | RS | (5) | RT | (5) | R  | D (5) | SA | (5) | Functio | on (6) |

| Figure 1 | : MIPS | R-Type | instruc | tion f | ormat |

|----------|--------|--------|---------|--------|-------|

|----------|--------|--------|---------|--------|-------|

| 31    | 26    | 25 | 21   | 20 | 16  | 15 |                | ) |

|-------|-------|----|------|----|-----|----|----------------|---|

| Opcod | e (6) | R  | 5151 | RT | (5) |    | Immediate (16) |   |

| Figure 2: | MIPS I-Type | instruction | format |

|-----------|-------------|-------------|--------|

|-----------|-------------|-------------|--------|

| 31 2       | 6 25 | ,                        | 0 |

|------------|------|--------------------------|---|

| Opcode (6) |      | Target Jump Address (26) |   |

# Figure 3: MIPS J-Type instruction format

The opcode field is the Operation Code field that indicates the code for each instruction. Each instruction has its own unique opcode. RS is the source or base register. RT acts as a second source register for R-Type instruction, but acts as the destination register for I-Type instruction. RD is the destination register (only present in R-Type instruction). SA (shift amount) is the amount of bits to be shifted. Only certain instructions use this field for execution. Immediate acts as the immediate operand or as address offset, depending on the instruction that is being executed. Target Jump Address is the memory word address to be jumped to [4]. It has 26-bit literal that is concatenated with the 6 most significant bits of the program counter to create 32-bit address.

Since 5 bits are allocated to registers (RS, RT, and RD) field, it follows that the MIPS architecture contains  $2^5 = 32$  internal registers that can be accessed by instructions given.

## 2.4 CPU Functional Units

It is important to understand the relationships between the CPU, the memory, and the program before looking into the details of how CPU works. The program is the list of instructions to be executed by the processor. Examples of programs are the software and applications that are available in our computers today. The memory temporarily stores the list of instruction of the program and also the data of the program during CPU execution. The CPU then reads the list of instructions stored in the memory one-by-one and performs the required execution on the data. Finally, the processed data is stored back into the memory.

#### 2.4.1 Program Counter (PC)

Program counter contains the next instruction address to be executed. Normally, PC will be increased after every instruction executed to point to the next address, except if any flow control instructions is executed which modifies the bits contained in the PC, thus modifies the sequence of the instructions.

# 2.4.2 Instructions Memory

The instructions memory contains the list of instructions to be executed by the CPU. The CPU fetches the instructions that it needs to execute from the instructions memory.

#### 2.4.3 Instruction Register

Instruction register contains the current instruction that the CPU is executing. It stores the current register temporarily and is connected to various other logic devices such as control logic and register files. After current instruction is completed, the content of this instruction register will be overwritten by the next instruction.

#### 2.4.4 Register File

Register file serves as the general purpose register to store temporary data that is executed by the CPU. Register files are similar to Random Access Memory (RAM), except that it does not have as much capacity as RAM. It is also faster than RAM. This makes the execution of register-register instructions faster.

#### 2.4.5 Random Access Memory (RAM)

RAM is a form of computer data storage. However, it is a volatile memory which means that the stored information is lost if the power is removed. It functions similarly to the register files – to store temporary data. However, it usually has much more capacity than the register file has.

## 2.4.6 Control Logic

Control logic controls the sequence and the datapath flow of an instruction. When an instruction is executed, it fetches and translates the opcode of the instruction. Then, it will output the control logic signals to the appropriate modules such as register files, ALU, memory, and also multiplexers that handle the data path.

# 2.4.7 Arithmetic and Logic Unit (ALU)

ALU is the unit that does the arithmetic and logical manipulation of data such as addition, subtraction, logical AND, logical OR, logical XOR, and many more. It is a fundamental building block of the CPU of a computer [6].

#### 2.4.8 Address Bus and Data Bus

Buses are used to simplify the movement of data from point to point in a CPU. It is connected to various logic devices in order to transfer data. In a bused system, only one communication from point to point could happen at any one time. Thus, a careful synchronization needs to be taken care of to make sure that the data is successfully transmitted.

# CHAPTER 3 METHODOLOGY

This chapter discusses about how the project would be carried out. It includes the method of research, tools, components, and software involved.

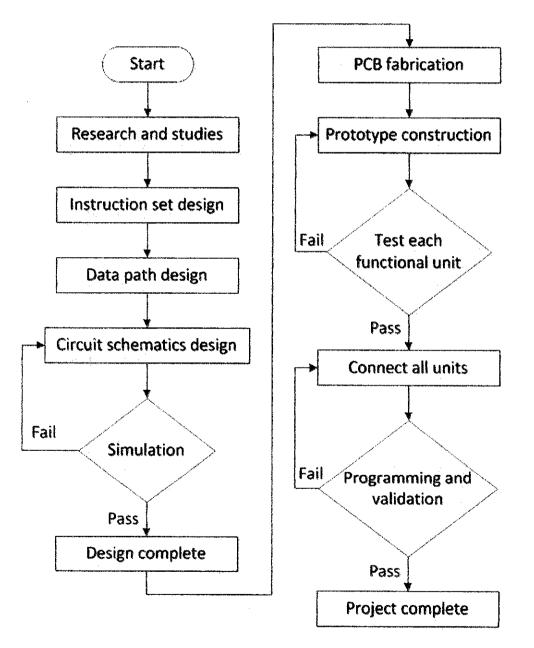

# 3.1 Project Flowchart

**Figure 4: Project Flowchart**

# 3.2 Research Methodology

The theories behind CPU design and CPU architectures, especially MIPS architecture are studied. However, studies regarding CISC and RISC architectures are also done. The research mainly focuses on the decision between these architectures – which one would best educate students.

After decision is made, which is to focus on MIPS architecture, further research regarding MIPS architecture is done. To understand CPU architecture, the knowledge on these theories is important. This includes instruction set architecture, CPU functional units, and CPU data path. All these have been outlined in the literature review chapter.

The sources of research include from books, websites, conference papers, and also journals. The relevancy between the selected sources and the project's objectives is also taken into account to ensure the credibility of this project. The understanding from participation in Computer System Architecture classes and labs has also contributed to the research study.

#### 3.3 Instruction Set Design

In this stage, instruction set architecture is designed. The ISA defines the whole identity of the processor itself. Since the processor is only used for educational purposes, which is to show to the students the concept of how processors work, it would have a very limited instruction set. Thus, the choice of instructions to be included has been made according to research that shows the most commonly used instruction in a program.

The design begins with the format of the instruction set. The instruction format defines the width of the instruction, opcode field, and also operand fields. Figure 5 below illustrates how the instructions format is designed.

| How many bits? | How many operands? How many bits? |

|----------------|-----------------------------------|

| Opcode field   | Operand field(s)                  |

| 4              | How many bits?                    |

**Figure 5: Instruction Format Design**

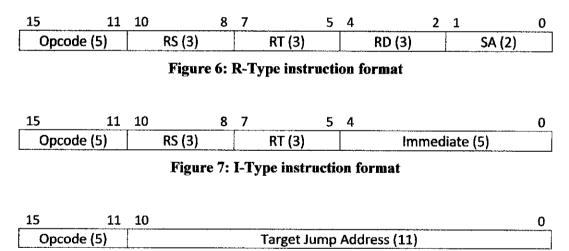

The selection of instructions to be included in the CPU is also done in this stage. Each of the selected operation is assigned with a unique opcode in order for the processor to differentiate between them. Their operands are then fitted accordingly, depending on the instruction. The instructions are divided into 3 categories – R-Type, I-Type, and J-Type, similar to MIPS architecture.

Below are the figures of the operands field design for all three types of instructions. Note that the instruction is designed to be 16 bits instead of 32 bits to reduce complexity. However, the concept of the educational processor remains similar to MIPS architecture.

As shown in the figures above, the instruction format is very similar to the instruction format of MIPS architecture. The difference is that in MIPS architecture, the instruction format is 32-bit instead of 16-bit. The number of bits in opcode and in the operand fields is reduced. The function field is present in MIPS architecture, but

not in this processor because we do not have as much number of instructions in this project. So, the function field is not needed. So, as a summary, the designed bits are:

- Opcode: 5 bits

- Registers (RS, RT, RD): 3 bits

- Shift Amount (SA): 2 bits

- Immediate (Imm): 5 bits

- Jump Address (JumpAddr): 11 bits

# 3.4 Tools Required

The tools that are required in this project can be divided into two parts, which is software and hardware. For the software, the tools required are:

• CCS C Compiler v4.106

This is used to program the microcontroller that will be used for control logic in the CPU.

• PICKit v2.61

This program is used to write the written program in MPLAB IDE v8.70 into the microcontroller.

• ActivePerl v5.12

ActivePerl is needed to compile the program written in Perl language.

Microsoft Visual Studio 2010

This program is needed for creating the user interface that will interact with the educational processor.

• Quartus v10.1

This software will be used mostly for simulation.

• CadSoft Eagle Professional v5.6.0 Eagle is used to design PCB boards.

The hardware needed in this project can easily be obtained in the Electrical & Electronics Store at Block 22. All hardware needed is listed below:

- Microprocessor

- TTL gates (includes ALU, registers, RAM, multiplexers, and others)

- PCB boards

# 3.5 Instructions List

This educational processor is capable of executing 16 types of instructions. The instructions are listed below, together with its corresponding opcode, operands, and how it operates.

| Name                   | Mnemonic | Туре | Operation                                                             | Opcode |

|------------------------|----------|------|-----------------------------------------------------------------------|--------|

| Add                    | add      | R    | add \$rd, \$rs, \$rt<br>R[rd]=R[rs]+R[rt]                             | 00001  |

| Add Immediate          | addi     | Ι    | addi \$rt, \$rs, Imm<br>R[rt]=R[rs]+ZeroExtImm                        | 00010  |

| Subtract               | sub      | R    | sub \$rd, \$rs, \$rt<br><b>R[rd]=R[rs]-R[rt]</b>                      | 00011  |

| And                    | and      | R    | and \$rd, \$rs, \$rt<br><b>R[rd]=R[rs]&amp;R[rt]</b>                  | 00100  |

| And Immediate          | andi     | Ι    | andi \$rt, \$rs, Imm<br>R[rt]=R[rs]&ZeroExtImm                        | 00101  |

| Or                     | or       | R    | or \$rd, \$rs, \$rt<br>R[rd]=R[rs] R[rt]                              | 00110  |

| Or Immediate           | ori      | Ι    | ori \$rt, \$rs, Imm<br>R[rt]=R[rs] ZeroExtImm                         | 00111  |

| Xor                    | xor      | R    | xor \$rd, \$rs, \$rt<br>R[rd]=R[rs]^R[rt]                             | 01000  |

| Xor Immediate          | xori     | I    | xori \$rt, \$rs, Imm<br>R[rt]=R[rs] <sup>^</sup> ZeroExtImm           | 01001  |

| Shift Left<br>Logical  | sll      | R    | sll \$rd, \$rs, shamt<br><b>R[rd]=R[rs]&lt;<shamt< b=""></shamt<></b> | 01010  |

| Shift Right<br>Logical | srl      | R    | srl \$rd, \$rs, shamt<br>R[rd]=R[rs]>>shamt                           | 01011  |

| Store Word             | sw       | Ι    | sw \$rt, \$rs, Imm<br>M[R[rs]+ZeroExtImm]=R[rt]                       | 01100  |

| Load Word              | lw       | Ι    | lw \$rt, \$rs, Imm<br>R[rt]=M[R[rs]+ZeroExtImm]                       | 01101  |

| Branch On<br>Equal     | beq      | I    | beq \$rs, \$rt, BranchAddr<br>if(R[rs]==R[rt])<br>PC=PC+4+BranchAddr  | 01110  |

| Branch On Not<br>Equal | bne      | I    | bne \$rs, \$rt, BranchAddr<br>if(R[rs]!=R[rt])<br>PC=PC+4+BranchAddr  | 01111  |

| Jump                   | j        | J    | j JumpAddr<br>PC=JumpAddr                                             | 10000  |

**Table 1: Instructions List**

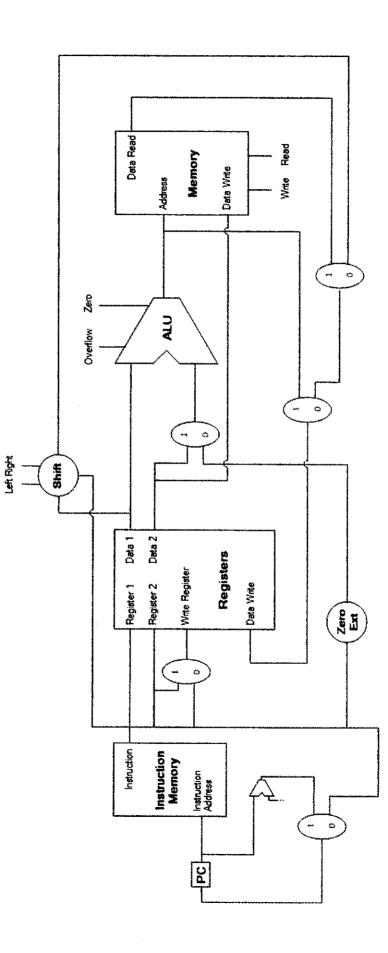

# 3.6 Datapath

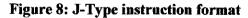

The datapath of this EduCPU is designed so that it can perform the instructions listed before. The whole datapath of this educational processor is shown in Appendix B.

#### 3.7 Graphical User Interface

A program is written using Perl and Visual Basic 2010. This software is able to compile assembly language that is inputted by user and compile it into machine language. It is equipped with error-checking codes to prevent errors during transmission. The program is also able to transmit the machine codes into the educational processor hardware and retrieve back the relevant data from the educational processor. Besides transmitting the machine code to the actual hardware, the program is able to simulate written assembly code, and display the flow of data. More details about this program are covered in Chapter 4.

## 3.8 **Project Duration**

In order to effectively monitor the progress of this project, a Gantt chart has been constructed. The Gantt chart is included in Appendix A.

# CHAPTER 4 RESULTS AND DISCUSSION

# 4.1 Graphical User Interface

A program designed to run in Windows is programmed using Microsoft Visual Studio 2010 and also Perl programming language. This program is called EduCPU. The Visual Basic source code is attached in Appendix F. It is designed to compile from assembly language input by user to the machine code that follows the instruction format designed. EduCPU's features are:

- Compiles assembly language code into machine language code

- Simulates the written assembly code

- Displays values in registers

- Changes values in registers

- Displays values in memory

- Displays data that flows in the datapath

EduCPU consists of 5 main windows. First is the main view. This is where the user needs to put the assembly code. Figure 9 shows the main view window.

|                    | .a.    | EduCPU View    | Serial Port Settings                                                          |

|--------------------|--------|----------------|-------------------------------------------------------------------------------|

|                    |        | Registers View | COM Port -                                                                    |

|                    |        |                | Baud Rate 🗸                                                                   |

|                    |        | Memory View    | Data Bits 🔹 👻                                                                 |

|                    |        | Help           | Parity 👻                                                                      |

| Machine code:      |        |                | Software Flow Control                                                         |

|                    |        | Compile        |                                                                               |

|                    |        | Current Line   | yFerm ites Waltes                                                             |

|                    | 3<br>5 | 0              | - Registers: 197                                                              |

| . Street and state | بالم   | Total Lines: 0 | у Динти арылған.<br>1972 жылған салуна қазасындағы саластта аласына таластта. |

Figure 9: EduCPU Main View

15

The program is equipped with error-checking codes. This means, if the user enters a wrong command, wrong syntax, or invalid register/immediate values, the compiler will tell the user there has been an error in the code.

When the user puts the assembly code in the designated field and presses 'Compile', the program will check the code for any errors. If there are errors, the text box at the right side will display the error and the 'Transmit' button is disabled. See below for example.

| Assembly code:                                             |                |                                           |  |

|------------------------------------------------------------|----------------|-------------------------------------------|--|

| add \$7, \$21, \$31 / / add \$5, \$1                       | EduCPU View    | Serial Port Settings                      |  |

| addf \$4, \$5, \$1                                         | Registers View | COM Port 👻                                |  |

|                                                            |                | Baud Rate 🗸                               |  |

|                                                            | Memory View    | Data Bits 🔹                               |  |

| ۰.<br>۱                                                    | Help           | Parity 👻                                  |  |

| Machine code:<br>0000110101111111100 -<br>0500100100010100 |                | Software Flow Control                     |  |

|                                                            | Compile        |                                           |  |

|                                                            | Current Line   | in an an an ann an an an an an an an an a |  |

Figure 10: Example of code with errors

In Figure 10, the user puts assembly code with some errors listed below:

- Value of RS and RT at line 1 is too large. We only have 8 registers, so the maximum value should be \$7.

- At line 2, the command 'add' should have 3 operands. The user only puts 2 operands, thus generating the error code.

- At line 3, there is no such command 'addf'.

If the user puts code with no syntax error, the bottom box will display "Code OK. Proceed with transmission". The 'Transmit' button will be enabled and the user can now proceed with the simulation as shown in Figure 11.

| Assembly code:                                   |   |                |                            |           |             |

|--------------------------------------------------|---|----------------|----------------------------|-----------|-------------|

| addi \$0, \$0, 31<br>addi \$1, \$1, 20           | * | EduCPU View    | Serial Port Settings       |           |             |

| add \$2, \$1, \$0                                |   | Registers View | COM Port                   | *         | Port closed |

| sw \$2, \$1, 5                                   |   |                | Baud Rate                  | -         |             |

|                                                  |   | Memory View    | Data Bits                  | -         |             |

|                                                  | - | Help           | Parity                     | *         |             |

| Machine code:                                    |   |                | Software Flow Control      |           |             |

| 0001000000011111<br>0001000100110100<br>00001001 | ^ | Compile        | Software How Control       |           |             |

| 0110000101000101                                 |   | Current Line   | Code OK. Proceed with tran | smission. | Transmit    |

|                                                  | - | Total Lines: 4 |                            |           |             |

Figure 11: Code without any syntax error

Before proceeding with the simulation by pressing 'Transmit' button, user should first click 'EduCPU View' to view the datapath, 'Registers View' to view the values in registers, and 'Memory View' to view the values in memory. The 3 windows are shown in Figure 12, Figure 13, and Figure 14 respectively.

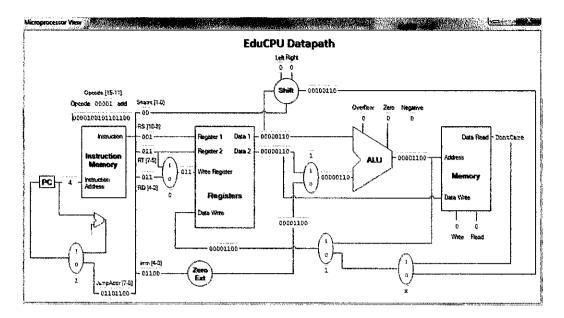

Figure 12: EduCPU Datapath View 17

| Register View  |           |

|----------------|-----------|

| EduCPU F       | Registers |

| Register 000   | 0000000   |

| Register 001   | 00000000  |

| Register 010   | 00000000  |

| Register 011   | 00000000  |

| Register 100   | 00000000  |

| Register 101   | 0000000   |

| Register 110   | 0000000   |

| Register 111   | 00000000  |

| Change<br>Valu |           |

Figure 13: Register View

| Edu                             | CPU Memor                | y |

|---------------------------------|--------------------------|---|

| 0                               | 00000000                 |   |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 00000000                 |   |

| 2                               | 00000000                 |   |

| 3                               | 000000000                |   |

| 5                               | 00000000                 |   |

| 6                               | 00000000                 |   |

| 7                               | 00000000                 |   |

| 8                               | 00000000                 |   |

| 9                               | 00000000                 |   |

| 10                              | 00000000                 |   |

| 11<br>12                        | 00000000                 |   |

| 13                              | 00000000                 |   |

| 14                              | 00000000                 |   |

| 15                              | 00000000                 |   |

| 16                              | 00000000                 |   |

| 17                              | 00000000                 |   |

| -                               |                          |   |

|                                 | Refresh Memory<br>Values |   |

Figure 14: Memory View

We can directly change the values in the registers during simulation using the Register View window. After changing the values, press the 'Change Register Values' button to save the changes.

As guide for users, they can click the 'Help' button to display the list of instructions and the correct syntax on how to use them. Note that the instructions are very similar to MIPS instructions. After clicking the 'Help' button, the window as shown in Figure 15 should pop out.

| Name                | Mnemonic | ?ype | Operation                                                                 | Opcode |

|---------------------|----------|------|---------------------------------------------------------------------------|--------|

| Add                 | add      | R    | add Srd, Srs, Srt<br>R[fd]=R[fs]+R[ft]                                    | 00001  |

| Add Immediate       | addi     | ł    | addi Srt, Srs, Imm<br>R[n]=R[rs]+ZeroExtimm                               | 00010  |

| Subtract            | sub      | R    | sub 5rd, 5rs, 5rt<br>R[rd]=R[rs]-R[rt]                                    | 00011  |

| And                 | and      | R    | and Srd, Srs, Srt<br>R[rd]=R[rs]&R[rt]                                    | 00100  |

| And Immediate       | andi     | ł    | andi Srt, Srs, Inn<br>R[s]=R[s]&ZeroExtimm                                | 00101  |

| Or                  | or       | R    | or 5rd, 3rs, Srt<br>R[rd]=R]rs][R[rt]                                     | 00110  |

| Or Immediate        | ori      | 1    | ori Srt, Srs, Im.<br>R[n]=R[rs][ZeroExtimm                                | 00111  |

| Xor                 | KOT      | R    | Nor Srd, Srs, Srt<br>R[rd]=R[rs] R[rt]                                    | 01000  |

| Xor (mmediate       | nori     | 1    | Nori Srt, Srs, Imm<br>R[rt]=R[rs]'ZeroExtimm                              | 01001  |

| Shift Left Logical  | sil      | R    | sll Srd, Srs, shant<br>R[rd]=R[rs]< <shamt< td=""><td>01010</td></shamt<> | 01010  |

| Shift Right Logica  | sti      | R    | srl ard, års, shant<br>R(rd)=R[rs]>>shamt                                 | 01011  |

| Store Word          | sw       | ł    | sw \$rt, \$rs, Inm<br>M[R[rs]+ZeroExtimm]=R[rt]                           | 01100  |

| Load Word           | łw       | 1    | lw \$22, \$28, lan<br>R[n]=M[R[rs]+ZeroExtimm]                            | 01101  |

| Branch On Equal     | beq      | ì    | beq srs, srt, BranchAddr<br>if(R[rs]==R[rt]) PC=PC+4+BranchAddr           | 01110  |

| Branch On Not Equal | bne      | 1    | bne srs, pro, BranchAddr<br>H(R[rs]I=R[rt]) PC=PC-4-BranchAddr            | 01111  |

| lump                | 3        | J    | j JumpAddr<br>PC=lumpAddr                                                 | 10000  |

Figure 15: Help Window

# 4.2 Compiling

As can be seen in Figure 11 in previous pages, the assembly code is automatically compiled into machine code. The exact process can be seen through examples in section 4.3.

# 4.2.1 R-Type

| add \$2, \$1 | , \$0 |  |

|--------------|-------|--|

R-Type instructions' detailed information is shown in Chapter 3.5. For the above instruction, the 'add' instruction is translated into 00001 (the opcode). Then, the register RS which is \$1 is translated into its binary equivalent, which is 001. Register RT, \$0 is translated into 000. Register RS, \$2, is translated to 010. Finally, since no shift operation is involved, the shift amount (2 bits) is set to 00.

Note that all registers are designed to be 3 bits. So, all register values are translated into 3 bits. This process generates the following machine code:

| and the second |                                       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| 0000100100001000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |

| here and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · · |  |

## 4.2.2 I-Type

| addi | \$2, | 20 |  |

|------|------|----|--|

|      |      |    |  |

I-Type instructions require 3 operands. For 'addi' instruction, the opcode is 00010. Then, register RS, \$2 is translated into 010. Register RT, \$1 is translated into 001. Finally, the immediate value, 20 is translated into 10100. Immediate value is designed to be 5 bits. So, this generates the following machine code:

## 0001001000110100

j 3

J-Type instructions require only 1 operand, which is JumpAddr (Jump Address). The opcode for instruction 'j' is 10000. Then, the JumpAddr, which is valued at 3, is translated into 00000000011. This process generates the following machine code:

#### 100000000000011

## 4.3 Simulation: Test Code 1 – Adding values

addi \$0, \$0, 31 addi \$1, \$1, 20 add \$2, \$1, \$0 sw \$2, \$1, 5

This test code will basically add value 31 to register 0, add value 20 to register 1, and then add the values in register 0 and register 1 into register 2. Value in register 2 will then be stored into memory location 25. We can track which data goes where exactly by observing the Datapath View, Register View, and Memory View. The compiled test code can be seen in Figure 11.

After pressing 'Transmit' button once, we can see the Current Line in Main View changes to 1. The values in Datapath View and Register View are also updated as seen in Figure 16 and Figure 17. We can see how data flows into the CPU and also real time register values.

Figure 16: Test Code 1, Line 1 Datapath View

| Register View    |           |

|------------------|-----------|

| EduCPU F         | Registers |

| Register 000     | þ0011111  |

| Register 001     | 00000000  |

| Register 010     | 00000000  |

| Register 011     | 00000000  |

| Register 100     | 0000000   |

| Register 101     | 00000000  |

| Register 110     | 0000000   |

| Register 111     | 0000000   |

| Change  <br>Valu |           |

Figure 17: Test Code 1, Line 1 Register View

After line 1 is simulated (we can see current line in Datapath View, at PC (program counter) value), register 0 [000] is loaded with value 31 [00011111]. This happens because value in register 0 is given by summation of current value in register 0 (which is currently 0) and immediate value of 31. By pressing 'Transmit'

button again, line 2 is simulated. Line 2 is similar to line 1 - they both use 'addi' command. After pressing 'Transmit' button for the third time, line 3 is simulated, as shown in Figure 18 and Figure 19.

Figure 18: Test Code 1, Line 3 Datapath View

| EduCPU Registers |          |  |  |  |

|------------------|----------|--|--|--|

| Register 000     | 00011111 |  |  |  |

| Register 001     | 00010100 |  |  |  |

| Register 010     | 00110011 |  |  |  |

| Register 011     | 00000000 |  |  |  |

| Register 100     | 00000000 |  |  |  |

| Register 101     | 00000000 |  |  |  |

| Register 110     | 00000000 |  |  |  |

| Register 111     | 00000000 |  |  |  |

Figure 19: Test Code 1, Line 3 Register View

After simulating line 3, we can see the updated values in Register View. Register 1 [001] is loaded with value 20 [00010100] during simulation of line 2. Register 2 [010] now has value 51 [00110011], which is the summation of values in register 0 and register 1. We can see the in Datapath View around the Registers, Data 1 comes from register [001], and Data 2 comes from register [000]. Both these data flows into the ALU, and the result of [00110011] comes out from the ALU. The data is written back into register [010], which is register 2. Now, we simulate line 4 of the code.

| EduCPU Memory |                |       |

|---------------|----------------|-------|

| ""            |                | Ury   |

| 18            | 00000000       | · · · |

| 19            | 00000000       |       |

| 20            | 00000000       | 8777  |

| 21            | 00000000       |       |

| 22            | 00000000       |       |

| 23            | 00000000       | ÷ .   |

| 24            | 00000000       |       |

| 25            | 00110011       |       |

| 26            | 00000000       |       |

| 27            | 00000000       |       |

| .28           | 00000000       |       |

| 29            | 00000000       |       |

| 30            | 00000000       |       |

| 31<br>32      | 00000000       | . '   |

| - 32          | 00000000       |       |

| 34            | 00000000       |       |

| 35            | 00000000       |       |

|               | 0000000        | ₹.    |

| N 11          |                | ·     |

|               | Refresh Memory |       |

|               | Values         | • • • |

Figure 20: Test Code 1, Line 4 Memory View

According to the command executed, which is [sw \$2, \$1, 5], the value in register 2 [010] will be stored into memory value register 1 [001] + 5. Since the value in register 1 is 20 [00010100], when added with 5, the result is 25. We can see the updated memory values by pressing 'Refresh Memory Values' button. So, the value in register 2, which is 51 [00110011] is stored in memory location 25 as shown in Figure 20 above. Now the code has completed the simulation. The 'Transmit' button in Main View is now automatically disabled again.

| addi \$0, \$0, 3  |  |

|-------------------|--|

| addi \$1, \$1, 6  |  |

| addi \$2, \$2, 1  |  |

| add \$3, \$1, \$3 |  |

| sub \$0, \$0, \$2 |  |

| bne \$0, \$4, \$4 |  |

# 4.4 Simulation: Test Code 2 – Multiplying values

In this test code, we are going to do a  $6 \times 3$  multiplication. The answer will be saved into register 3. The method of doing this is we are going to add the value 6 with itself 3 times.

In the first two lines, we are just putting the numbers to be multiplied in the registers. Value 3 [00000011] is saved into register 0 and value 6 [00000110] is saved into register 1. In third line, value 1 [00000001] is saved into register 2. The purpose is so that we can subtract one from the counter in each loop.

In the fourth line, the data in register 1 is added to the data in register 3 and stored into register 3. This action is shown in Figure 21 and Figure 22.

Figure 21: Reg 3 = Reg 1 + Reg 3

| Register View |           |

|---------------|-----------|

| EduCPU F      | Registers |

| Register 000  | b0000011  |

| Register 001  | 00000110  |

| Register 010  | 0000001   |

| Register 011  | 00000110  |

| Register 100  | 00000000  |

| Register 101  | 00000000  |

| Register 110  | 00000000  |

| Register 111  | 00000000  |

| Change<br>Vak |           |

Figure 22: Registers view after line 4 is transmitted

After the value 6 is added once, the value in register 0 is subtracted by one. The value in register 0 represents the loop counter. Once it reaches 0, the program will no longer add the value 6 into register 3. Figure 23 shows the registers view after line 5 has been transmitted:

| legister View |           |

|---------------|-----------|

| EduCPU I      | Registers |

| Register 000  | 00000010  |

| Register 001  | 00000110  |

| Register 010  | 00000001  |

| Register 011  | 00000110  |

| Register 100  | 00000000  |

| Register 101  | 00000000  |

| Register 110  | 00000000  |

| Register 111  | 00000000  |

| Change<br>Val |           |

Figure 23: Registers view after line 5 is transmitted

As we can see in Figure 23, the value in register 0 is decreased by one. The last line checks if the value in register 0 is equal to value in register 4 or not. If it is not equal, the program will go back to line 4 of the code. Now, the value in register 0 is 2 [00000010] and the value in register 4 is 0 [00000000]. It is not equal (Zero flag not raised to 1), means the program will go back to line 4. Figure 24 shows the datapath view after transmitting the last line. Note that the zero flag is zero:

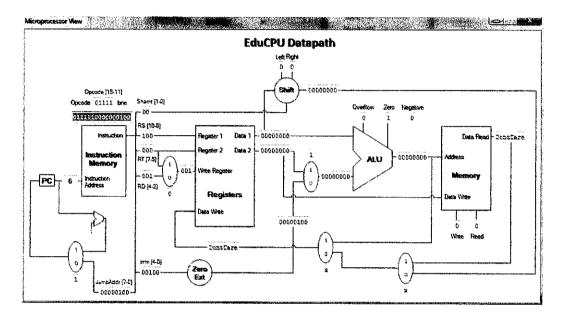

Figure 24: Datapath view after transmitting line 6

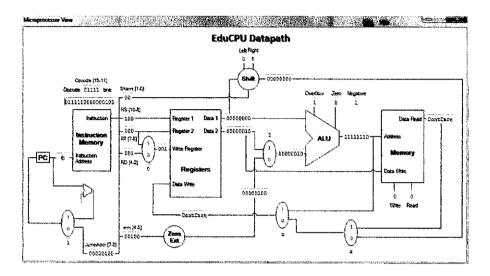

The program now goes back to line 4. The main view, datapath view, and registers view is shown in Figure 25, Figure 26, and Figure 27 respectively.

| Assembly code:                                            |         |                |                                                                                                                 |                    |          |

|-----------------------------------------------------------|---------|----------------|-----------------------------------------------------------------------------------------------------------------|--------------------|----------|

| addi \$0, \$0, 3<br>addi \$1, \$1, 6                      | × .     | EduCPU View    | Serial Port Settin                                                                                              | gs                 |          |

| addi \$2, \$1, 2<br>addi \$2, \$2, 1<br>add \$3, \$1, \$3 |         | Registers View | COM Port                                                                                                        |                    |          |

| sub \$0, \$0, \$2<br>bne \$0, \$4, \$4                    |         | Memory View    | Baud Rate                                                                                                       | •                  |          |

| Duc +0, +1, +1                                            |         |                | Data Bits                                                                                                       | ▼.                 |          |

|                                                           | . 🔨     | Help           | Parity                                                                                                          | •                  |          |

| Machine code:                                             |         | ·              | Software Flow (                                                                                                 | ···· ·             |          |

| 0001000000000011                                          |         | []             | Software now (                                                                                                  | OTITO)             | •        |

| 0001000100100110                                          | :       | Compile        |                                                                                                                 |                    |          |

| 0001001001000001                                          |         |                |                                                                                                                 | ÷                  |          |

| 0000100101101100                                          | i.<br>Q |                | in a second s |                    |          |

| 0001100001000000                                          | 5-<br>- | Current Line   | CTTS-040 #005445.8                                                                                              | 1973 ang 1977 39 5 | Ě        |

| 01111100000000100                                         | -       |                |                                                                                                                 |                    | Transmit |

Figure 25: Main view after transmitting line 4 for second time

Figure 26: Datapath view after transmitting line 4 for second time

| Register View   |                  |

|-----------------|------------------|

| EduCPU F        | Registers        |

| Register 000    | <b>þ</b> 0000010 |

| Register 001    | 00000110         |

| Register 010    | 00000001         |

| Register 011    | 00001100         |

| Register 100    | 00000000         |

| Register 101    | 0000000          |

| Register 110    | 00000000         |

| Register 111    | 00000000         |

| Change  <br>Vak |                  |

Figure 27: Registers view after transmitting line 4 for second time

We can see the value in register 3 is now 12 [00001100]. Value in register 0 will be decreased by one again, and then 'bne' instruction will check if value in register 0 is equal to value in register 4. It is still not equal because at this point of time, the value in register 0 is 1 [00000001] and value in register 4 is 0 [0000000]. The program will go back to line 4 again for transmission.

In line 4, the value 6 will be added again to register 3, making the value in register 6 to be 18 [00010010]. In line 5, the register 0 will contain the value 0 [00000000] because the previous data, which was 1, is decreased again by one. In line 6, 'bne' instruction will check again if value in register 0 is equal to the value in register 4. If they are equal, the zero flag will be raised. Now we can see that they are equal, denoted by the zero flag raised to 1. This is shown in Figure 28.

Figure 28: Datapath view after transmitting the last line of the code

| Register View    |                  |

|------------------|------------------|

| EduCPU I         | Registers        |

| Register 000     | <b>0</b> 0000000 |

| Register 001     | 00000110         |

| Register 010     | 00000001         |

| Register 011     | 00010010         |

| Register 100     | 00000000         |

| Register 101     | 00000000         |

| Register 110     | 00000000         |

| Register 111     | 00000000         |

| Change  <br>Valu |                  |

Figure 29: Registers view after transmitting the last line of the code

Note that the program is complete at this point. We have the value in register 0 to be 0 [00000000], register 1 to be 6 [00000110], register 2 to be 1 [00000001] and register 3 to be 18 [00010010] (our wanted final answer). The register values are shown in Figure 29. The 'Transmit' button is also disabled now, indicating that the program has reached the end, as shown in Figure 30.

| Assembly code:                                   |    |                |                            |           |                              |

|--------------------------------------------------|----|----------------|----------------------------|-----------|------------------------------|

| addi \$0, \$0, 3<br>addi \$1, \$1, 6             | ^  | EduCPU View    | Serial Port Settings       |           |                              |

| addi \$2, \$2, 1<br>add \$3, \$1, \$3            |    | Registers View | COM Port                   | *         | Port closed                  |

| sub \$0, \$0, \$2<br>bne \$0, \$4, \$4           |    | Memory View    | Baud Rate                  | *         | Photosophic solid concerning |

| and 401 441 44                                   |    | manory mon     | Data Bits                  | *         |                              |

|                                                  | Ψ. | Help           | Panty                      | -         |                              |

| Machine code:                                    |    |                | Software Flow Control      |           |                              |

| 00010000000000011<br>0001000100100100<br>0001001 | *  | Compile        | Soltware How Control       |           |                              |

| 0000100101101100                                 |    | Current Line   | Code OK. Proceed with tran | smission. |                              |

| 0111110000000100                                 |    | 6              |                            |           | Transmit                     |

|                                                  | -  | Total Lines: 6 |                            |           |                              |

Figure 30: Main view after transmitting the last line of the code

# 4.5 Transmitting machine code through serial communication

The machine code compiled by the graphical user interface can be transmitted to the actual hardware through serial communication as shown in Figure 31 below.

Figure 31: Connection between PC and hardware

Since there will be a delay during transmission, the user has to wait approximately 2 seconds before the data transmission can complete successfully. To make sure that the simulation software is synchronized with the hardware result, the simulation result is also delayed by approximately 2 seconds if a port is opened. If no port is opened, the simulation will show results instantaneously.

In order to transmit using correct port, the hardware needs to be connected to a serial port of the computer using a serial cable. Then, the correct port must be selected using the graphical user interface as shown in Figure 32 below.

| Assembly code:                                   |             |                |                |               |         |                 |

|--------------------------------------------------|-------------|----------------|----------------|---------------|---------|-----------------|

| addi \$0, \$0, 31<br>addi \$1, \$1, 20           | *           | EduCPU View    | Senal Port S   | ettings       |         |                 |

| add \$2, \$1, \$0                                |             | Registers View | COM Port       | COM1          | Ŧ       | COM1            |

| sw \$2, \$1, 5                                   |             |                | Baud Rate      | 9600          | Ŧ       | opened          |

|                                                  | Memory View |                | Data Bits      | 8             | *       | Close Port      |

|                                                  | -           | Help           | Panty          | None          | *       |                 |

| Machine code:                                    |             |                | Software Fl    | Cantoni       | None    |                 |

| 0001000000011111<br>0001000100110100<br>00001001 | ^           | Compile        | Soltware Fi    | Jw Control    | None    |                 |

| 0110000101000101                                 |             | Current Line   | Code OK. Proce | ed with trans | m 35 00 |                 |

|                                                  |             | 0              |                |               |         | Transmit!       |

|                                                  | -           | Total Lines: 4 |                |               |         | Constant Sec. 1 |

Figure 32: Choosing the correct serial port

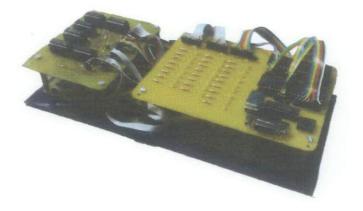

# 4.6 Hardware

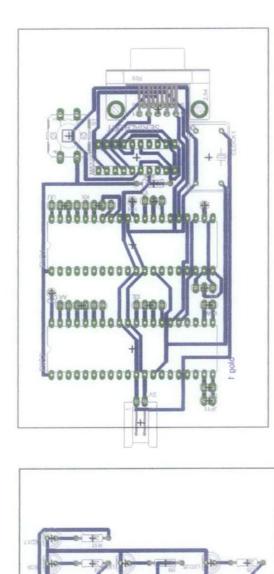

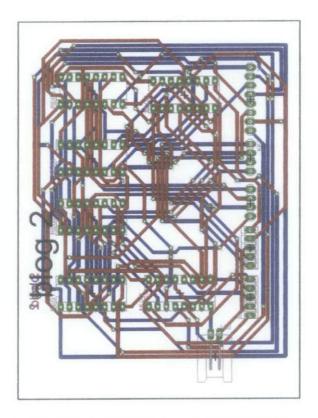

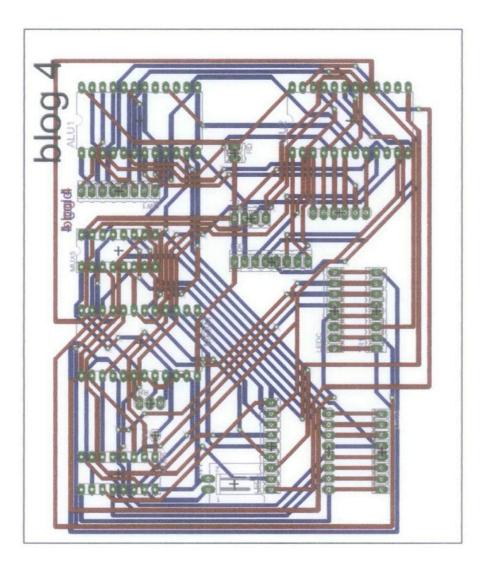

The circuit design has been finished according to the datapath design shown in Appendix B. The circuit design is done using CadSoft Eagle Professional v5.6.0. It is shown in Appendix C. However, the actual implementation is that the circuit is divided into 5 smaller parts for easier fabrication. The divided PCB parts are shown in Appendix D.

Data is stored in register files. 4 register files are used in the designed circuit. This is because the educational processor is designed with 8 8-bit registers. Each register file only stores 4 4-bit register, so we need 4 register files in order to fulfill the requirement of the design. Arithmetic logic unit (ALU) is used to compute certain instructions such as add, sub, or, xor, and many more. 2 ALUs are used because each ALU can only process 4 bits of data. Since the whole processor is designed for 8-bit data, we need 2 ALUs to complete the instructions given.

Depending on the instruction, ALU, registers, and memory will need to receive data from different parts of the circuit. The multiplexers are used to control this data flow. 3-state buffers are used to disconnect certain data whenever it is not needed, so that the data will not interfere with data coming from another part of the circuit. Memory is used to store data temporarily. The memory is able to store a total of 2048 8-bit data.

Two microcontrollers will be used to send the control logics to all the other parts of the circuit. They will receive instructions from a connected computer through serial communication. The software will send the instruction bits to the microcontroller serially, and then the microcontrollers will send the control logics to each component on the circuit in order to execute the instructions properly. The data flowing in the circuit will be shown by LEDs on the circuit for easy reference.

The actual Educational Processor hardware with 16-bit instruction and 8-bit data has been constructed and is shown in Figure 33.

Figure 33: Hardware of Educational Processor

The hardware will perform the same functions as the simulation software, with some differences. The differences are:

- The hardware is unable to process 'srl' and 'sll' instructions due to the absence of parallel shift register.

- Users will not be able to directly change register values using the EduCPU software. Values need to be set using 'addi' instruction.

- The data displayed on the hardware will not be as detailed as in the simulation software. The data displayed will only be at:

- ALU output / Memory address input

- Memory output / Memory input

- Data written back into register

Despite the differences, users will still be able to see what data flows inside the hardware by using multi meter. The LEDs are placed at only significant parts of the circuit for easier implementation.

Upon receiving serial data from the computer, the microcontrollers will interpret the received data and send corresponding control logic signals to the ICs in order to execute the instruction given properly. 2 microcontrollers are used to send logic signals, since the pins needed to control everything could not be covered by only one microcontroller.

If the user does not use any 'srl' or 'sll' instructions or change the values in the register directly, the data displayed at the hardware should be exactly the same with the data shown in the simulation software.

### 4.7 Discussion

The EduCPU software should be significantly helpful for students who are taking Computer System Architecture course in UTP. The hardware will function just the same as the simulation software, so it is very useful for students who prefer hands-on learning compared to just using the software. The hardware can be improved some more by adding parallel shift register IC. Due to several constraints such as IC supplies and time constraint, the parallel shift register could not be added to this processor. Other than that, the hardware is working perfectly as intended.

# CHAPTER 5

# **CONCLUSION & RECOMMENDATIONS**

### 5.1 Conclusion

The objective of this project is to develop a simple processor using TTL logic gates for educational purpose. This educational processor will be assisted by software that will communicate with the educational processor through serial communication.

The software can also work on its own without the hardware. It can provide simulation of the codes inputted by the user, and show exactly how MIPS-based processors work. This will definitely help students in learning how processors work, especially in Computer System Architecture course.

### 5.2 Recommendations

For future work, there are definitely a lot of improvements that can be done to improve the educational processor. Such improvements include:

- The number of instructions can be increased to more than 16 instructions, allowing for more complex programs to be run on the processor.

- Full working CPU capable of running a simple operating system can be constructed. If this is completed, this project can educate students in areas more than just Computer System Architecture, but also in the Operating System, Assembler & Compiler Design and more areas.

### REFERENCES

- [1] Albert P. Malvino & Jerald A Brown, 3rd edition, "Digital Computer Electronics", "SAP Processor".

- [2] Weik, Martin H. (1961), "A Third Survey of Domestic Electronic Digital Computing Systems".

- [3] Alan Clements (2006), 4th edition, "Principle of Computer Hardware".

- [4] Gary Shute (2007), "MIPS Instruction Coding" http://www.d.umn.edu/~gshute/spimsal/talref.html.

- [5] J. Hennessy, N. Jouppi, S. Przybylski, C. Rowen, T. Gross, F. Baskett, and J. Gill (1982), "MIPS: A Microprocessor Architecture".

- [6] Hwang, Enoch (2006), "Digital Logic and Microprocessor Design with VHDL". Thomson.

- [7] D 'Arcy Becker, Meg Dwyer (1998), "The Impact of Student Verbal/Visual Learning Style Preference on Implementing Groupware in the Classroom".

# APPENDIX A – PROJECT GANTT CHART

|                            |   |   |   |   |   |   | FINAL YE | FINAL YEAR PROJECT 1 | CT 1 |              |    |    |    |    |

|----------------------------|---|---|---|---|---|---|----------|----------------------|------|--------------|----|----|----|----|

| Activities                 |   |   |   |   |   |   | WEEK     | WEEK NUMBER          | 8    |              |    |    |    |    |

|                            | 1 | 2 | 3 | 4 | S | 9 | 7        | 00                   | 6    | 10           | 11 | 12 | 13 | 14 |

| Topic selection            |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Research about topic       |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Complete literature review |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Instruction set design     |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| User interface programming |   |   |   |   |   |   |          |                      |      | State of the |    |    |    |    |

| Data path design           |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Circuit schematics design  |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Simulation and debugging   |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Fabrication                |   |   |   |   |   |   |          |                      |      |              |    |    |    |    |

| Activities               |   |   |   |   |   |   | FINAL YE<br>WEE | FINAL YEAR PROJECT 2<br>WEEK NUMBER | R R |    |    |    |    |    |

|--------------------------|---|---|---|---|---|---|-----------------|-------------------------------------|-----|----|----|----|----|----|

|                          | 1 | 2 | 3 | 4 | S | 9 | 7               | 00                                  | 6   | 10 | 11 | 12 | 13 | 14 |

| Task identification      |   |   |   |   |   |   |                 |                                     |     |    |    |    |    |    |

| Software programming     |   |   |   |   |   |   |                 |                                     |     |    |    |    |    |    |

| Hardware fabrication     |   |   |   |   |   |   |                 |                                     |     |    |    |    |    |    |

| Progress report          |   |   |   |   |   | • |                 |                                     |     |    |    |    |    |    |

| Software bug fixing      |   |   |   |   |   |   |                 |                                     |     |    |    |    |    |    |

| Hardware troubleshooting |   |   |   |   |   |   |                 |                                     |     |    |    |    |    |    |

| Draft Report             |   |   |   |   |   |   |                 |                                     |     |    |    |    | 0  |    |

| Final Report             |   |   |   |   |   |   |                 |                                     |     |    |    |    |    | 0  |

APPENDIX D - SPLIT PCB CIRCUIT DESIGN

ULED BOARD