## **EDUCATIONAL PROCESSOR**

By

## HAFIZUL HASNI BIN MANAB

## FINAL PROJECT REPORT

Submitted to the Electrical & Electronics Engineering Programme in Partial Fulfillment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2010 by Hafizul Hasni Bin Manab, 2010

## **CERTIFICATION OF APPROVAL**

## EDUCATIONAL PROCESSOR

by

Hafizul Hasni Bin Manab

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved:

(Mr. Patrick Sebastian) Project Supervisor

## UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

June 2010

## **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Hafizul Hasni Bin Manab

## ABSTRACT

This report discusses the overview of the chosen project, which is an Educational Processor. The objective of this project is to develop a simple processor with TTL logic for educational purpose. This processor will be used as a learning tool for Computer System Architecture class. To complete this project, the scope of study will cover the computer system architecture and Central Processing Unit (CPU). The CPU datapath design and hardware circuit design is based on the MIPS single-cycle processor. The methodologies that will be involved in this project are design and validation phase, constructing the hardware and then interfacing phase through serial communication between CPU and a graphic user interface using microcontroller. The prototype would be used as a learning tool in Computer System Architecture class and to assist student in understanding the computer architecture.

## **ACKNOWLEDGEMENTS**

Special thanks to project supervisor Mr. Patrick Sebastian, Lab Technicians Ms. Siti Fatimah, Ms. Siti Hawa and Mr. Isnani who help me a lot in finishing this project.

Not to forget, greatest appreciation to my family who have supported throughout the development of this project as well as friends who have given a lot of helps.

# **TABLE OF CONTENTS**

| ABSTRACTiv                                        |

|---------------------------------------------------|

| ACKNOWLEDGMENTv                                   |

| LIST OF TABLESviii                                |

| LIST OF FIGURESix                                 |

| LIST OF ABBREVIATIONSx                            |

| CHAPTER 1 INTRODUCTION                            |

| 1.1 Background of Study1                          |

| 1.2 Problem Statement1                            |

| 1.3 Objective and Scope of Study2                 |

| CHAPTER 2 LITERATURE REVIEW                       |

| 2.1 Procedure Identification                      |

| 2.2 Instruction Sets Architecture                 |

| 2.2.1 Complex Instruction Sets Computing4         |

| 2.2.2 Reduced Instruction Sets Computing5         |

| 2.2.3 Instruction usage                           |

| 2.2.4 RISC instruction format7                    |

| 2.2.5 Addressing modes                            |

| 2.3 CPU Functional Units9                         |

| 2.3.1 Program Counter (PC)9                       |

| 2.3.2 Program/Instructions Memory                 |

| 2.3.3 Instruction Register                        |

| 2.3.4 Register File (General Purpose Registers)10 |

| 2.3.5 Arithmetic and Logic Unit10                 |

| 2.3.6 Data Memory10                               |

| 2.3.7 Control Logic                               |

| 2.3.8 Address Bus and Data Bus11                  |

| 2.4 Brief introduction to MIPS processor11        |

| CHAPTER 3 METHODOLOGY14                           |

| 3.1 Project Flowchart14                           |

| 3.1.1 Research Study15                            |

| 3.1.2 Instruction set design15                    |

| 3.1.3 Datapath design16                           |

|           | 3.1.4 Circuit schematic design                        | .17  |

|-----------|-------------------------------------------------------|------|

|           | 3.1.5 Simulation                                      | .17  |

|           | 3.1.6 Prototype construction and module/unit test     | . 18 |

|           | 3.1.7 Combine modules (CPU functional units) and test | . 18 |

| CHAPTER 4 | RESULT AND DISCUSSION                                 | .19  |

|           | 4.1 Design phase results                              | .19  |

|           | 4.1.1 Instructions designed                           | . 19 |

|           | 4.1.2 Instruction set formats                         | .20  |

|           | 4.1.3 Datapath design result                          | .22  |

|           | 4.1.4 Circuit schematic design                        | .26  |

|           | 4.1.5 CPU characteristic                              | .26  |

|           | 4.1.5.1 Programming the processor                     | .26  |

|           | 4.1.5.2 Processor control                             | .26  |

|           | 4.1.5.3 Arithmetic and Logic Unit                     | .27  |

|           | 4.1.5.4 Registers and data RAM                        | .27  |

|           | 4.1.5.5 Summary of CPU operation                      | .27  |

|           | 4.1.5.6 PCB Implementation                            | .27  |

|           | 4.2 CPU Functional Unit Control Signals               | .28  |

|           | 4.3 CPU Hardware Fabrication                          | .30  |

|           | 4.4 Graphic User Interface                            | .31  |

|           | 4.5 CPU-GUI Interfacing                               | .32  |

|           | 4.6 Testing Procedure and Validation Result           | .33  |

| CHAPTER 5 | CONCLUSION AND RECOMMENDATION                         | .50  |

|           | 5.1 Conclusion                                        | . 50 |

|           | 5.2 Recommendation                                    | .50  |

| REFERENCE | S                                                     | .51  |

| APPENDICE | S                                                     | . 52 |

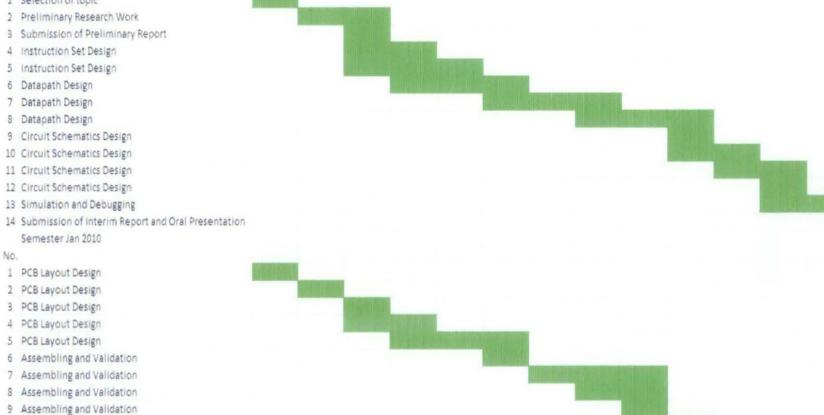

|           | Appendix A PROJECT GA NTT CHART                       | .53  |

|           | Appendix B CIRCUIT SCHEMATICS                         | .55  |

|           | Appendix C SIMULATION RESULTS                         | .65  |

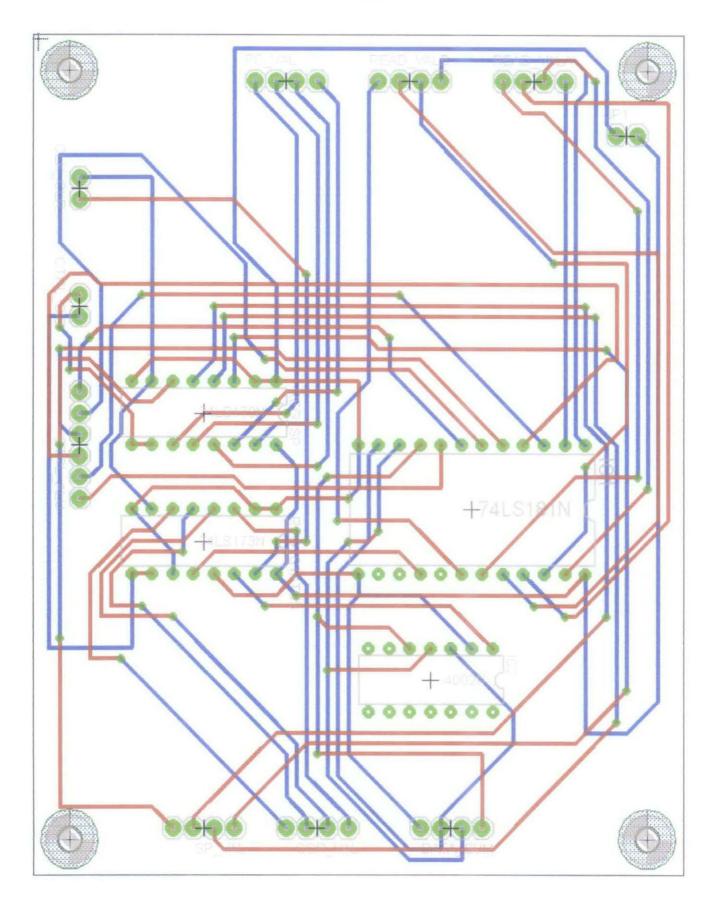

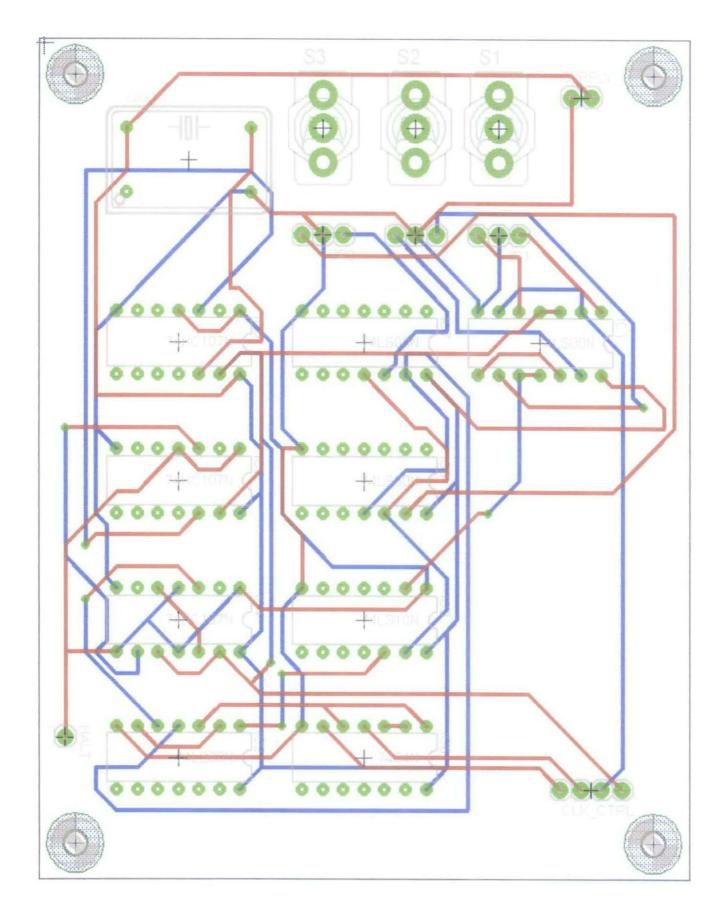

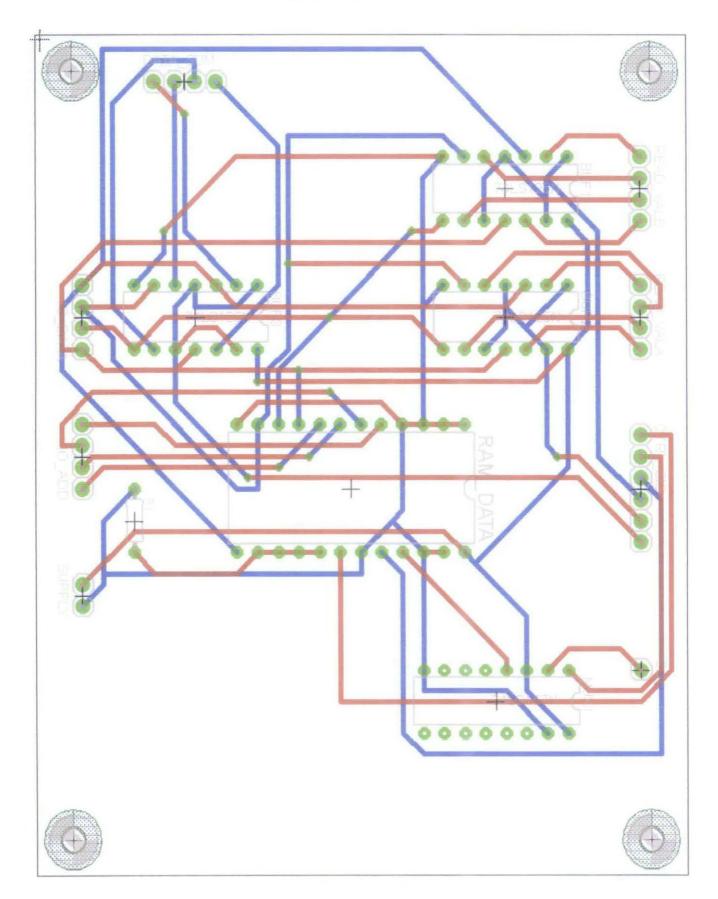

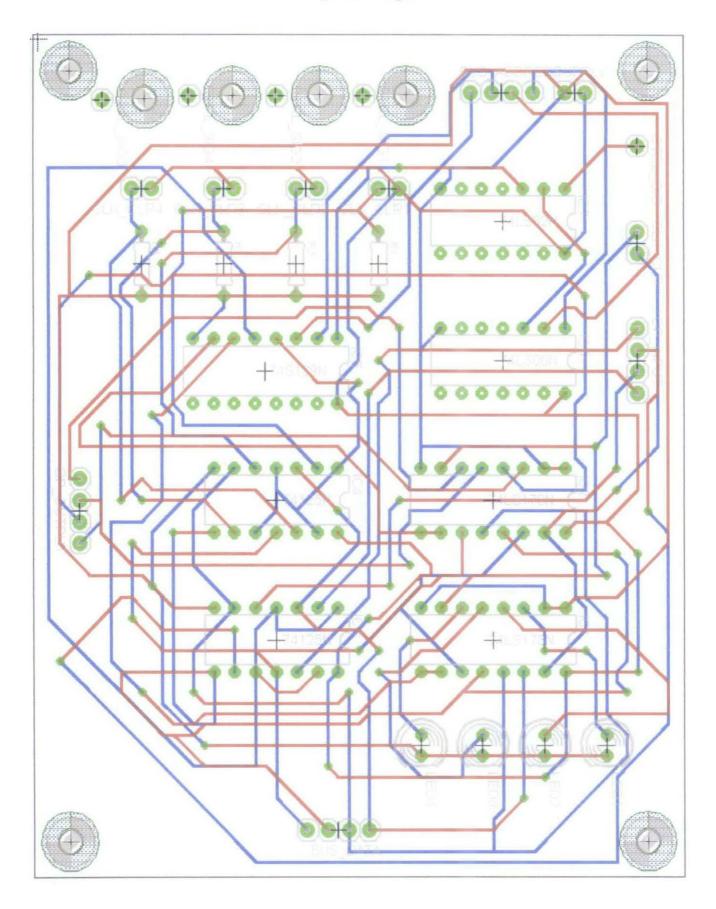

|           | Appendix D PCB LAYOUTS                                | .67  |

|           | Appendix E SOURCE CODE FOR CONTROL LOGIC              | .76  |

# LIST OF TABLES

| Table 1 Comparison between RISC and CISC processor | 5  |

|----------------------------------------------------|----|

| Table 2 Frequency of instruction usage             | 7  |

| Table 3 MIPS pipeline architecture                 | 12 |

| Table 4 Control signal                             |    |

| Table 5 First Test program                         |    |

| Table 6 GUI's serial communication configuration   |    |

| Table 7 First test program validation result       | 40 |

| Table 8 Second test program                        | 41 |

| Table 9 Second test program validation result      |    |

| Table 10 Third test program                        | 43 |

| Table 11 Third test program validation result      | 44 |

| Table 12 Fourth program pseudo code                | 45 |

| Table 13 Fourth test program instruction decode    |    |

| Table 14 Fourth test program validation result     | 47 |

| Table 15 Fifth test program                        | 48 |

| Table 16 Fifth test program validation result      |    |

## **LIST OF FIGURES**

| Figure 1 RISC Berkeley's instruction format            | 7  |

|--------------------------------------------------------|----|

| Figure 2 MIPS instruction formats                      | 13 |

| Figure 3 Project flowchart                             | 14 |

| Figure 4 Instruction format design                     | 15 |

| Figure 5 Operand fields design for R-type instructions |    |

| Figure 6 R-type instruction format                     |    |

| Figure 7 I-type instruction format                     | 21 |

| Figure 8 J-type instruction format                     |    |

| Figure 9 R-type instruction datapath                   | 22 |

| Figure 10 I-type instruction datapath                  | 23 |

| Figure 11 J-type instructions datapath                 |    |

| Figure 12 Combined datapath                            |    |

| Figure 13 CPU fabricated                               |    |

| Figure 14 CPU graphic user interface                   |    |

| Figure 15 Full system Educational Processor            |    |

| Figure 16 GUI's serial communication configuration     |    |

| Figure 17 Address switches and RD/WR switch            | 35 |

| Figure 18 Writing a CPU Instruction                    | 36 |

| Figure 19 Sending a CPU Instruction                    |    |

| Figure 20 Requesting hardware result                   |    |

| Figure 21 First test program final result              | 40 |

| Figure 22 Second test program final result             | 42 |

| Figure 23 Third test program final result              |    |

| Figure 24 Fourth test program final result             | 47 |

| Figure 25 Fifth test program final result              | 49 |

# LIST OF ABBREVIATIONS

| RISC   | Reduced Instruction Set Computing      |

|--------|----------------------------------------|

| CISC   | Complex instruction set computing      |

| CPU    | Central Processing Unit                |

| RAM    | Random access memory                   |

| EPROM  | Erasable Programmable Read-only memory |

| PC     | Program Counter                        |

| CSA    | Computer System Architecture           |

| TTL    | Transistor-transistor Logic            |

| OPCODE | Operation Code                         |

| РСВ    | Printed Circuit Board                  |

| ASM    | Assembly Code                          |

| GUI    | Graphic User Interface                 |

# CHAPTER 1 INTRODUCTION

This chapter discusses the introduction to this project. It covers the background of study that discuss the background knowledge involve in this project. The problem statement and objectives that lead to implementation of this project are also discussed.

#### 1.1 Background of Study

This project is about a development of a simple processor for learning purpose, which will be used in Computer System Architecture class. The main objective is to provide an opportunity for the student to examine at the gate level on how a processor executes an instruction. This educational processor will be a great learning tool for computer system student to learn computer system architecture. Therefore, the knowledge required in this project is application knowledge of digital electronics as well as computer system architecture. This project also required knowledge in microcontroller since this processor would be interfaced to the computer by using microcontroller via serial communication. After that, all the information and operation involved during execution of an instruction by the processor will be shown in a graphic user interface.

#### 1.2 Problem Statement

The processor is an essential part of a computer system. The development of the processor has involved over the years. In 1945, a mathematician John Von Neumann outlined the design of most modern CPUs [3]. Most of the processor designs now are very sophisticated and complex. The Electrical and Electronics Engineering student in UTP who are majoring in Computer System have the opportunity to learn about computer system through Computer System Architecture course. The current Computer System Architecture course exposes the student to the course with lecture as well as hands on lab assignment.

Nevertheless, there is no main focus on any specific computer architecture. Most of the time, the overall CPU datapath design that they are exposed to be just the high-level functional unit block that explains the CPU datapath.

Therefore, this project would give an opportunity the Computer System Architecture student to explore and examine at the gate level of CPU datapath, which means the student can observe how each logic device interact with each other to complete a CPU instruction.

#### 1.3 Objective and Scope of Study

The main objectives of this project are:

- To develop a simple processor as a learning tool in computer system class

- To construct the PCB and validate the prototype

- To develop a graphic user interface to program the designed CPU

The scope of work for this project covers the planning and design phase, developing the prototype phase, validating phase and the last is future improvement phase. In the planning and design phase, the scope of work will be focus on processor instruction set architecture and datapath. After that, it will followed by prototype developing phase where the data path hardware is implemented using the TTL logic implemented on PCB. In the validating phase, the datapath hardware will be interfaced to the computer with a graphic user interface by using microcontroller.

# CHAPTER 2 LITERATURE REVIEW

This chapter discusses the theory and paperwork review related to this project. Details on the CPU architecture and datapath design would also be discussed here.

#### 2.1 Procedure Identification

There are two ways of introducing the processor. One is to explain how a computer works of its internal information flow by describing the way in which information is transmitted between registers and the internal units and showing how an instruction is decoded and interpreted. The other approach is to introduce the native language, or machine code, of a computer and demonstrate what computer instructions can do [1].

## 2.2 Instruction Sets Architecture

Beginning with the hardware and looking at very primitive operations hides the "big picture". So, beginning with the explanation of an instruction set architecture would give reader the whole picture of a processor and therefore the detail hardware level of how an instruction is translated and executed could be easily understand.

An instruction set architecture (ISA) is an abstract model of a computer that describes what it does, rather than how it does it (functional definition). So, it can be said that the instruction set architecture and the instructions available in the processor determine the processor capabilities and performance [1].

The instruction set architecture varies from machine to machine. Instructions are classified by format and the number of operands they take. The three basics instruction types are data movement which copies data from one location to another, data processing which operates on data, and flow control which modifies the order in which instructions are executed.

Instruction formats can take zero, one, two or three operands. It depends on how much bit is used to represent the whole instructions. The instruction sets architecture can be distinguished by two classes which are the Complex Instruction Set Computing (CISC) and the Reduced Instruction Set Computing (RISC).

## 2.2.1 Complex Instruction Sets Computing

The CISC employs complex instruction which usually their instruction width (in bits) could vary depending on the type of instruction (data movement, data processing and flow control). For example there would be an instruction that consists of only the opcode (instruction identifier in bits) where it does not require any operation on the operand e.g.: Return from Subroutine (RTS).

Beside the variety of instruction width, each instruction could possibly be very complex in a way that it could perform operation with complex addressing. Complex addressing requires extra decoding and operation cycle. This is achieved usually through the usage of microcoding.

With variety of instruction width and complexity, it would take variable total of clock cycles to execute each instruction. It is because each instruction's opcode would be decoded firstly in the earlier cycle. The rest of the cycle would depend on the type of the instruction, which would make each instruction take at least two clock cycles to be executed.

## 2.2.2 Reduced Instruction Sets Computing

One of the important characteristic of a RISC is that having the singleinstruction format in contrast to the variable-width (length) instruction of CISC. This reduces the complexity of the decoding logic itself and thus could be used to easily educate new student in learning computer architecture.

Typically a RISC instruction format would consist of Opcode + Registers addresses. RISC is designed to contain only the register-to-register operation while for the memory access operation, RISC introduce a special instruction which is Load/Store. Thus, addressing modes in RISC processor are not as sophisticated as CISCs'.

RISC processors aim to execute on average one instruction per clock cycle. This goal imposes a limit on the maximum complexity of instruction and so to the hardware design of a RISC processor.

The *table 1* below summarizes the differences between RISC and CISC processor.

| <b></b>           | CISC                                         | RISC                                                                                   |

|-------------------|----------------------------------------------|----------------------------------------------------------------------------------------|

| Instruction width | Variable instruction<br>width                | Fix instruction width                                                                  |

| Instruction cycle | Multiple clock-cycle                         | Single clock-cycle                                                                     |

| Addressing modes  | Complex addressing<br>mode for memory access | Register-to-register data<br>transfer with special<br>instruction for memory<br>access |

Table 1 Comparison between RISC and CISC processor

## 2.2.3 Instruction usage

From the introduction of the microprocessor in the mid 1970s to the mid 1980s there was an almost unbroken trend toward more and more complex architectures [1]. With the advancement in the chip fabrication process, it allows designers to add more to the microprocessor's central core, which leads to cumbersome architectures and inefficient instruction sets but has tremendous commercial advantage for the end user. Intel's 8086 illustrates this trend particularly well, because Intel took their original 16-bit processor and added more features in each successive generation [1].

Although processors were advancing in terms architectural sophistication in the late 1970s, a high price was being paid for this progress in terms of efficiency [1]. Complex instructions required complex decoders and a lot of circuitry to implement while there was no guarantee that these instructions would be used in actual programs.

Computer scientist carried out extensive research over a decade or more in the late 1970s into the way in which computers execute programs [1]. Theirs studies demonstrated that there is no uniform frequency in which different type of instructions are executed. Some types of instructions are executed far more frequently than others.

Fairclough divided machine-level instructions into eight groups according to type and compiled the statistics described by Table 2. The mean value represents the result averaged over both program types and computer architecture.

6

## Table 2 Frequency of instruction usage

| Instruction Group                           | Mean Value (%) |

|---------------------------------------------|----------------|

| Data movement                               | 45.28          |

| Program modification (branch, call, return) | 28.73          |

| Arithmetic                                  | 10.75          |

| Compare                                     | 5.92           |

| Logical                                     | 3.91           |

| Shift                                       | 2.93           |

| Bit manipulation                            | 2.05           |

| Input/output and miscellaneous              | 0.44           |

## 2.2.4 RISC instruction format

One of the characteristics of RISC architectures is that it has a single instruction format. By providing a single instruction format, the decoding of an instruction into its component fields can be performed by a minimum level of decoding logic. A RISC's instruction length should be sufficient to accommodate the operation code field (opcode) and one or more operand fields [1]. Consequently, a RISC processor may not utilize memory space as efficiently as a conventional CISC microprocessor.

Figure 1 describes the format of a Berkeley RISC instruction, one of the first RISC processor that came from the University of California at Berkeley.

|      |       | _                 |           |       | 32          | bits     |    |                            | _                             |                     |

|------|-------|-------------------|-----------|-------|-------------|----------|----|----------------------------|-------------------------------|---------------------|

| 31   | 25    | 24                | 23        | 19    | 18          | 14       | 13 | 12                         | 5                             | 4                   |

|      |       | 4 le.             |           |       | <b>F A</b>  | ан<br>11 | 0  | 0000000                    | 0                             | \$4 \$3 \$2 \$1 \$0 |

| OD-C | 00e - | SCC               | Destinati | on    | Source 1    |          | 1  | i 12 i 11 i 10 i 9 i 8 i 7 | i <sub>6</sub> i <sub>5</sub> | i4 i3 i2 i1 i0      |

|      |       |                   |           |       |             |          | IM | So                         | Irce 2                        | 2                   |

| 7 bi | ts    | <b>↓</b><br>1 bit | 5 bits    | ••••• | ↓<br>5 bits | •        | -  | 9 bits                     |                               | 5 bits              |

Figure 1 RISC Berkeley's instruction format

The op-code field is the Operation code field that indicates the code for each instruction. Each instruction has its own unique Op-code. Scc field whether the condition code bits are updated after the execution of an instruction. Destination and Source 1 fields determine the address of register of which the result would be written into and the first source for an instruction's operand, respectively. The IM field determines the source for another instruction's operand. If it is 0, the source is the 5-bit address of the registers while if it is 1, the source is the 13-bit immediate number.

Because of 5-bits are allocated to each operand field, it follows that this RISC can access up to  $2^5 = 32$  internal registers at a time.

## 2.2.5 Addressing modes

Addressing mode is the method by which the location of an operand is specific within an instruction. Some of addressing modes most commonly used are describe as follows.

- 1. *Immediate addressing*. Operand is given in the instruction itself. Usually the second source of instruction's operand is supplied as part of the instruction.

- 2. *Address registers indirect addressing*. Operand is taken from, or result placed in, a pointer register. RISC processors allow any registers to act as a pointer.

- 3. *Base addressing*. Operand is in memory and its location is computed by adding of offset to the content of a specified base register. In RISC processor, this type of addressing mode is used by the Load and Store instruction to access RAM. The computed result would be asserted to the address of the RAM, and then the data would be stored into that location or the data is loaded into the destination register from that location.

- 4. *PC-relative addressing*. Same as base addressing, but with the register always being the program counter.

### 2.3 CPU Functional Units

Before looking into the details of how a CPU works, it is important to understand the relationship between the CPU, the memory and the program. The program contains list of instructions to be executed by the processor, for example the applications and software that available nowadays. The memory temporarily stores the list of instruction of the program and also the data of the program during CPU execution. The CPU read one-by-one list of instruction of program from the memory and perform the required execution on the data and probably store back the data in the memory.

In this project, the focus is on how this list of instructions in fetched from the memory, decoding the instructions producing the appropriate control signal, perform instruction-specific execution on the data and probably store the result of execution back into the memory. This process is shown in the project by the combinational logic circuits that make up CPU internal units which do specific job to complete one instruction. CPU internal units include are as follows:

## 2.3.1 Program Counter (PC)

Program counter contain the next instruction address to be executed. This address will be input the program RAM to access a specific line of instructions. Normally, PC would be increased after every instruction executed to point to the next address except if flow control instructions is executed which modify the bits contain in the PC.

#### 2.3.2 Program/Instructions Memory

Program memory contains the list of instruction to be executed. In Von Neumann architecture machine, program memory and data memory use the common RAM, while in Harvard architecture machine, program memory and data memory use separate RAMs.

## 2.3.3 Instruction Register

Instruction register contains the current instruction. It stores the current register temporarily and connects to various other logic devices such as control logic, and register files. When the next instruction is executed, it will overwrite the content of this instruction register.

#### 2.3.4 Register File (General Purpose Registers)

In RISC machine, register files are the important characteristic. It serves as the general purpose register to store temporary data that is executed by specific instruction. Register files are pretty similar to the RAM except that it doesn't have as much capacity as RAM and thus reduce the cost. Typically, registers are faster than RAM that makes execution of register-register instruction could be faster.

#### 2.3.5 Arithmetic and Logic Unit

ALU is the unit that does the manipulation to the data such as addition, subtraction, logical AND, logical OR and many more.

#### 2.3.6 Data Memory

Data memory is the storage device that store data from the program executed. It could be the constants, variables, address etc. Normally, data that are stores here are not a frequently used data as accessing the memory is slow thus make the program execution slower.

## 2.3.7 Control Logic

Control logic is among most important modules that make up a processor. It controls the sequence and datapath flow of an instruction. When an instruction is executed, it fetch and decode the opcode of that instruction and output the control logic signals to the appropriate modules such as register files, ALU and memory.

### 2.3.8 Address Bus and Data Bus

Bus is used to simplify the movement of data from point to point in a computer. Bus is analogous to a highway and the devices are analogous to junctions that connect to this highway. By having both address bus and data bus, it is possible to reduce the number of wires that interconnect within a computer but, it introduces a complexity. In a bused system, only one communication from point to point could happen at a time. Thus a careful synchronization needs to be taken care of and each bus access time has to be long enough for the safe reception in a communication.

## 2.4 Brief introduction to MIPS processor

MIPS processor is designed in 1984 by researchers at Stanford University. MIPS is part of RISC processor family.

Like the other processor in RISC family, MIPS employs load-store architecture. This means that there are two instructions for accessing memory, a Load instruction to load data from memory, and a Store instruction to write data into memory. It also means that none of the instruction can access memory directly. To do operation on data, the data has to be loaded into registers and the operation is performed on the data in the register. As most of the instruction operations are between registers, they allows faster execution and simpler circuit design.

MIPS processor executes instruction in a single clock cycle because of the nature of a RISC processor which is single instruction format. This fact allows the MIPS instructions to be split into stages for implementing pipelining. The stages are:

- IF Instruction fetch. Fetch the next instruction from memory using the address in Program Counter register and stores the instruction in Instruction Register.

- ID Instruction decode. Decode the instruction in the Instruction Register, calculate the next Program Counter, and read any operand required from the register files.

- 3. EX Execution stage. Perform arithmetic and logic operation.

- 4. **MA** Memory access. Perform any memory access required by the current instruction.

- WB Register write back. For any instruction with destination register specified, it writes back the result into the destination register.

By splitting instructions into different stages, it results in 5-clock cycle execution. But, with pipeline implementation, this technique would attempt to execute instructions approximately in one clock-cycle. Table 3 below shows the pipeline implementation in MIPS processor.

| CYCLE | IF  | ID  | EX  | MA  | WB  |

|-------|-----|-----|-----|-----|-----|

| 1     | i   |     |     |     |     |

| 2     | i+1 | i   |     |     |     |

| 3     | i+2 | i+1 | i   |     |     |

| 4     | i+3 | i+2 | i+1 | i   |     |

| 5     | i+4 | i+3 | i+2 | i+1 | i   |

| 6     | i+5 | i+4 | i+3 | i+2 | i+1 |

| 7     | i+6 | i+5 | i+4 | i+3 | i+2 |

Examining the table above, it can be clearly seen that from the fifth cycle, the first instruction is completed. Then, at the next cycle, the i+1 instruction (next instruction) is completed. This goes on the same towards further cycle. Although it takes five cycles to complete an instruction, but approximately the instructions are executed in one cycle. This is explained before, from the fifth cycle onwards, each instruction execution is completed.

The words "approximately" from the second last statement do carry an important meaning. Theoretically, the single-cycle approximation could be achieved based on the explanation before. But in reality, there are some dependencies of an instruction to another instruction. It means that some instruction stage could not be executed before it gets the valid data from instruction before. This hazard introduces "waiting delay", which makes the single-cycle approximation could not be achieved.

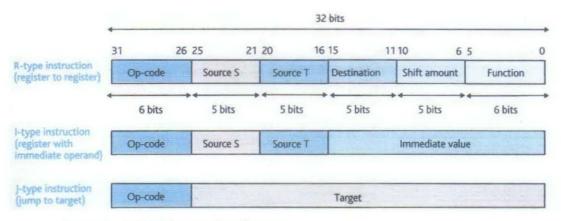

The MIPS instruction has three basic formats. Figure 2 below illustrates the of the MIPS instructions.

Figure 2 MIPS instruction formats

R-type instruction is a register-to-register format for all data processing instructions. I-type instruction is immediate format for either data processing instructions with a literal or load/store instructions with an offset. While J-type instruction is the format for branch/jump instruction with a 26-bit literal that is concatenated with the six most-significant bits of the program counter to create 32-bit address.

# CHAPTER 3 METHODOLOGY

This chapter discusses how the project is carried out. It includes the method of research, tools and software involved.

#### **PCB** fabrication Start Ţ **Prototype Construction Research study** 1 Fail Ц Instruction set design **Functional** Ţ unit test Datapath design Pass 11 **Combine all units Circuit schematics design** Ţ Л Fail Fail Programming Simulation in and validation Quartus Pass Pass **Project completed Design completed**

## 3.1 Project Flowchart

Figure 3 Project flowchart

#### 3.1.1 Research Study

In research study phase, the theory behind the CPU design and CPU architecture is studied. This includes the study on the CISC and RISC architecture design of a CPU. The research mainly focuses on the decision between these architectures that would best educate student.

After decision is made, the research continues on the details of RISC architecture. To understand the CPU architecture, the knowledge on these theories is important, which include instruction set architecture, CPU functional units and CPU data path. These theories are explained in the Literature Review chapter before.

The sources of research include from the books, websites, and journals. The author's participation in Computer System Architecture classes has also contributed to the research study.

## 3.1.2 Instruction set design

In this stage, instruction sets architecture is designed. This defines the whole identity of the processor itself. Since the processor would have a very limited instruction set, thus the choice of instructions have been made according to research that shows the most commonly used instruction in a program.

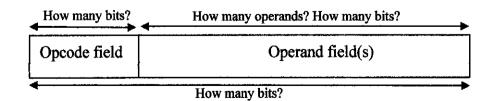

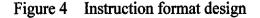

Design starts with the format of the instruction design. The instruction format defines the width of the instruction, op-code field and operand fields. Figure 4 below illustrates how the instructions format is design.

Concurrently, the selection of instructions to be included in the CPU is done. As explained before, the selection is done based on the most commonly used instructions in a program. Each of the selected instruction is then assigned with specific operation code (opcode). Their operands are then fitted accordingly. This means that each instruction would have different operands type as well as number of operands to be fitted with the designed instruction format. Figure below illustrates how the operand field for R-type instruction is fitted.

Figure 5 Operand fields design for R-type instructions

## 3.1.3 Datapath design

In this stage, the datapath of each chosen instructions are design. This is the last stage of CPU design. Datapath determines the connectivity between each CPU's functional units with each other. It translates an instruction into the hardware that does the execution to complete the instruction. The path for data movement from the start at the instruction fetch from memory towards the end, data write back into memory, is constructed. Hence, it is called "datapath".

To design a datapath, the formats of instructions are examined. For this project, there are 3 types of instruction formats that categorized all the instructions. This is discussed later in the next chapter. The purpose of identifying the formats of instructions is because instructions with the same format would have the same datapath.

Next is examining CPU functional units operations during the execution of a certain instruction format. For example, what does the Program Counter do? Does it increment to next instruction or it fetch address for branch instruction? Does register files do read operation only or both read and write operation? Does ALU is executing on the data or it does nothing? Does data memory access is needed or not? All of these factors determine the datapath of an instruction.

Knowing the operation of each CPU functional units, datapath for each instruction format is then designed. The final step would be combining those datapath for each format together to form the whole CPU datapath. The datapath designed for this project would be discussed in the next chapter, which is result and discussion chapter.

## 3.1.4 Circuit schematic design

In this stage, the datapath designed earlier is translated into combinational logics circuit. Each CPU functional unit logic circuit is constructed.

The schematic is designed using the Quartus software. Verilog HDL codes are written to simulate TTL devices such as registers, multiplexers and so on. Then, the CPU datapath logic circuit is constructed from these block diagrams of TTL devices emulations.

The purpose of designing the schematic using the Quartus is to allow simulation of the CPU. In fact, this schematic could be directly downloaded into an FPGA.

#### 3.1.5 Simulation

In this stage, simulation of the designed schematic is done. The purpose of simulation is as the first stage of error debugging.

Using this simulation, it provides the timing waveform of signals. These signals are examined whether it behaves as it should be in the datapath designed earlier. This fact prevents major debugging to the circuit later, because if there is any modification to the datapath required, it could be done in software rather than hardware which are tedious and costly.

## 3.1.6 Prototype construction and module/unit test

In this stage, the prototype is developed according to the schematic designed before. Development are done phase by phase according to CPU functional unit (PC, register files, etc).

After developing each CPU functional unit, it is put into a test. The test is done by invoking all possible inputs to the unit and verifies the output signals produce. The error is expected to be just the wrong connections, pins not connected or the TTL devices not functioning, if any.

## 3.1.7 Combine modules (CPU functional units) and test

After completing the entire module, the modules are combined together producing the whole processor. It is then put into a test again. The test procedure is done by loading a program into the processor and then executes.

In the design, the clock circuit is built in such a way that it can produce a single clock-cycle at a time. Thus, the program could be executed instruction by instruction.

For each instruction, the signals from each device each checked to ensure that all are functioning accordingly. After completing a program, the test is repeated again by loading the same program. This is to ensure the consistency of the circuit behavior.

# CHAPTER 4 RESULT AND DISCUSSION

This chapter discusses the result from the design phase and the simulation phase as well as the construction phase. The problem arise along those phases would also be discussed here.

## 4.1 Design phase results

## 4.1.1 Instructions designed

Instruction sets that are designed are as follows:

Data movement instruction:

| LDR rd, rs  | - | load data from memory location pointed by register $rs$ into register $rd$ . |

|-------------|---|------------------------------------------------------------------------------|

| STR rd,rs   | - | store data from register $rd$ to memory location pointed by register $rs$ .  |

| MOV rd,rs   | - | move (copy) data from register rs into register rd.                          |

| MOVI rd,Imm | - | move immediate (literal) value data into register rd.                        |

#### Data processing instruction:

| ADD rd,rs   | - Add content of register <i>rs</i> to content of register <i>rd</i> and store the result into register <i>rd</i> .             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| ADDI rd,Imm | - Add immediate (literal) value data to content of register <i>rd</i> and store result into register <i>rd</i> .                |

| SUB rd,rs   | - Subtract content of register <i>rs</i> from content of register <i>rd</i> and store result into register <i>rd</i> .          |

| SUBI rd,Imm | - Subtract immediate value data from content of register <i>rd</i> and store result into register <i>rd</i> .                   |

| CMP rd,rs   | - Compare content of register <i>rd</i> and content of register <i>rs</i> and set the condition code register (status register) |

CMPI rd,IMM - Compare content of register *rd* with immediate value and set the condition code register (status register).

Flow control instruction:

| BNE rt,Imm | - Check the CCR for zero flag, if not set, change PC to point next address pointed by content of register <i>rt</i> + immediate data. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| BLT rt,Imm | - Check the CCR for negative flag, if set change PC to point next address pointed by content of register <i>rt</i> + immediate data.  |

| JMP rt,Imm | - Unconditional jump (subroutine/function call) to address pointed by content of register <i>rt</i> + immediate data.                 |

| RTS        | - Return from subroutine. Restore the pc with next address from stack pointer.                                                        |

| END        | - Halt or stop the cpu operation. Terminate the program/end of line.                                                                  |

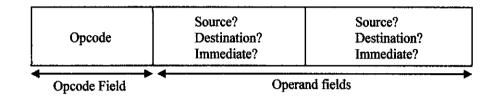

## 4.1.2 Instruction set formats

Instruction set architecture designed is using 8-bit word. Four most significant bits are the Operation code (opcode) field while the rest four-bits are the Operand field. The instructions could be divided into three formats according to MIPS processor which include:

1. R-type instructions (register-to-register instruction)

| 7 4    | 3                                         | 2 | 1 |                   | 0 |

|--------|-------------------------------------------|---|---|-------------------|---|

| OPCODE | Source 1 register<br>Destination register |   |   | Source 2 register |   |

Figure 6 R-type instruction format

## 2. I-type instructions (immediate operand)

| 7      | 43 |                                           | 2 | 1 |                    | 0 |

|--------|----|-------------------------------------------|---|---|--------------------|---|

| OPCODE |    | Source 1 register<br>Destination register |   |   | immediate data     |   |

|        |    | E                                         | • |   | - 4 <sup>1</sup> C |   |

Figure 7 I-type instruction format

## 3. J-type instructions (branch/jump instruction)

| 7      | 4 | 3                          | 2 | 1 | (                | ) |

|--------|---|----------------------------|---|---|------------------|---|

| OPCODE |   | target/pointer<br>register |   |   | immediate offset |   |

Figure 8 J-type instruction format

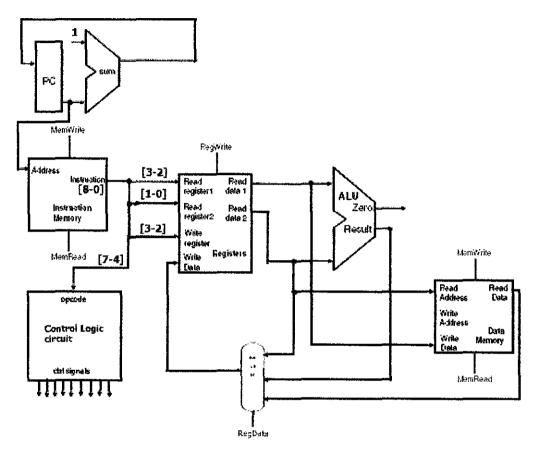

## 4.1.3 Datapath design result

Datapath is designed based on the three formats above explained in the chapter 3. The first datapath is for the R-type instructions. The result is as follows:

Figure 9 R-type instruction datapath

This datapath is the same for all instructions as follows:

- ADD

- SUB

- MOV

- CMP

- LDR

- STR

As shown in figure 9, the PC is incremented by 1 only. This is because these instructions do not affect the program sequence. Bit 7-4 is asserted to the control logic opcode address to produce appropriate control signals. Bits 3-2 is asserted for address Read register 1 and also address write register. This provides the first operand

for the instruction as well as the destination register to be written into. Bit 1-0 is asserted for Read register 2 providing the second operand for the instruction. The multiplexer is there to select source for data to be written into destination register. This is because instruction like MOV instruction does not require ALU operation, instruction like ADD instruction requires ALU operation and LDR instruction that take the data from the data memory.

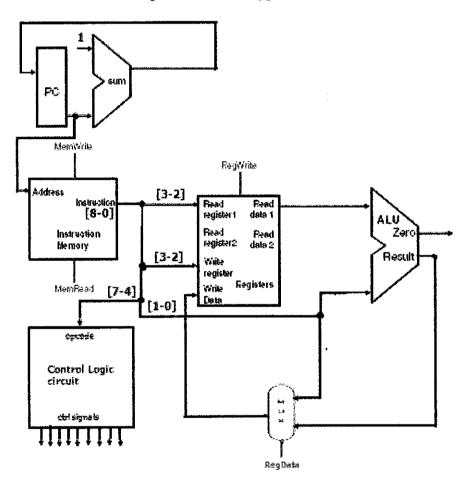

The second datapath is for the I-type instruction. The result is as follows:

Figure 10 I-type instruction datapath

This datapath is the same for all instructions as follows:

- ADDi

- SUBi

- MOVi

- CMPi

As shown in figure 10, the PC is also incremented by 1 only. This is because these instructions do not affect the program sequence. Bit 7-4 is asserted to the control logic opcode address to produce appropriate control signals. Bits 3-2 is asserted for address Read register 1 and also address write register. This provides the first operand for the instruction as well as the destination register to be written into. The difference between R-type datapath and I-type datapath is the bit 1-0 the two bits source for second operand of the instruction. The multiplexer is there to select source for data to be written into destination register. This is because instruction like MOV instruction does not require ALU operation while instruction like ADD instruction requires ALU operation. Another difference from the R-type instruction is that these instructions do not involve data memory access.

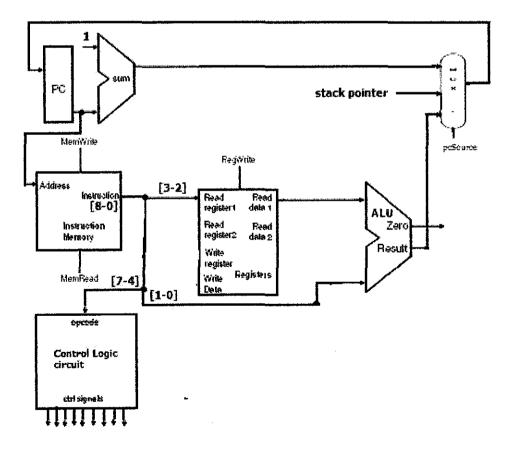

The third datapath is for the J-type instruction. The result is as follows:

Figure 11 J-type instructions datapath

This datapath is the same for all instructions as follows:

- BNE

- BLT

- JMP

- RTS

This format of instruction differs from the two formats before because it modifies the program sequence. PC is updated with either from three sources which are increment by 1, stack pointer data, or ALU results. PC updates from source increment by 1 if the branch condition is not met, thus resulting no branch operation is executed. PC updates from source stack pointer data for RTS instruction. This instruction restores PC with the content of the return address when the JMP instruction is executed before. PC updates from source ALU results if the branch conditions is met, thus resulting in branch operation. The address for the branch subroutine is given by the operand 1 plus with the two bits immediate data.

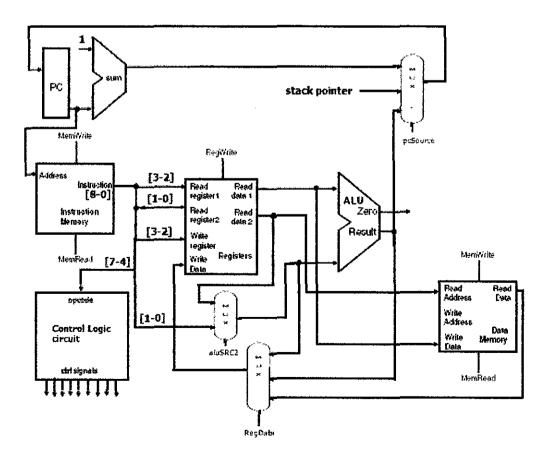

The combined datapath is then constructed. The result is as follows:

Figure 12 Combined datapath

As shown in the figure 12, all the datapath designed are then combined together. To execute certain instruction in a certain instruction format group, control signals would have to play this role. It controls the CPU functional units so that only the affected functional units are "activated".

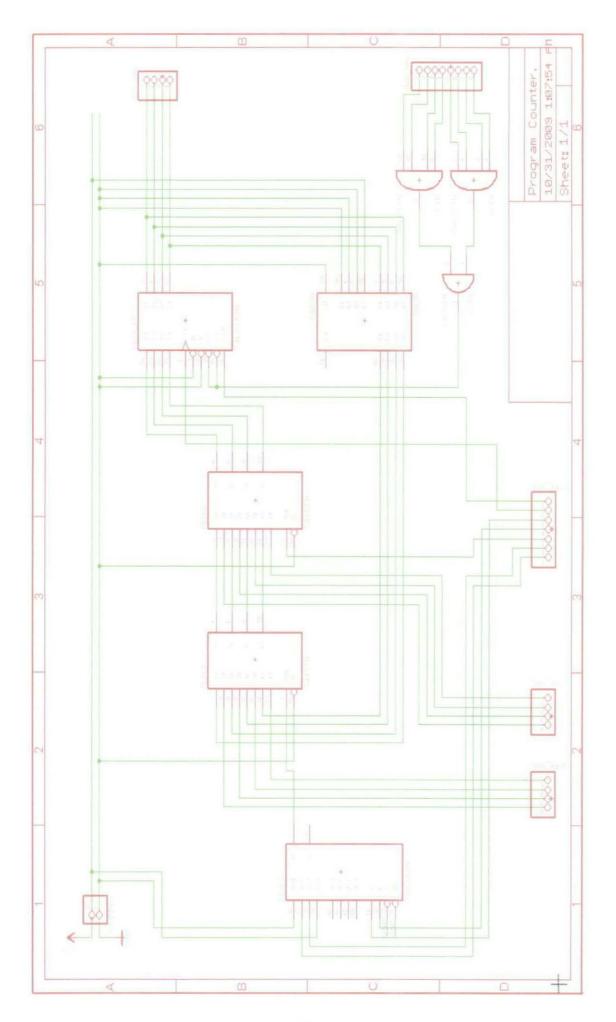

## 4.1.4 Circuit schematic design

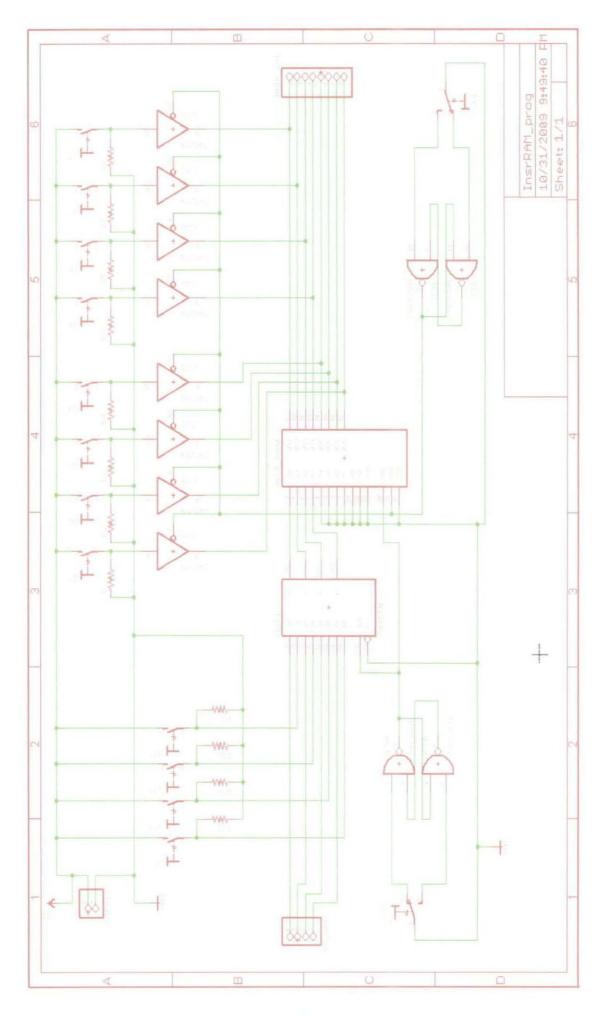

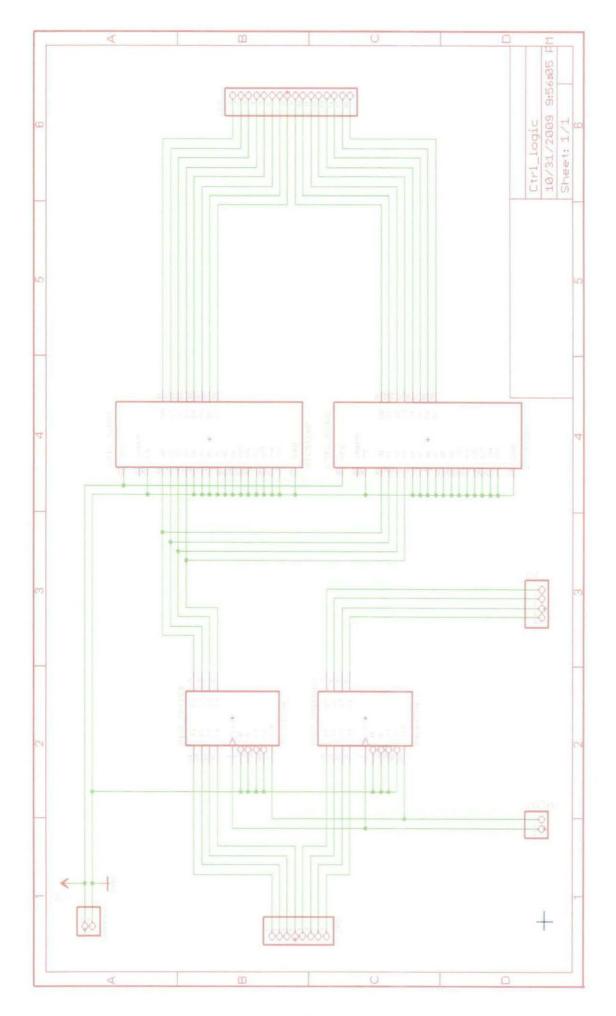

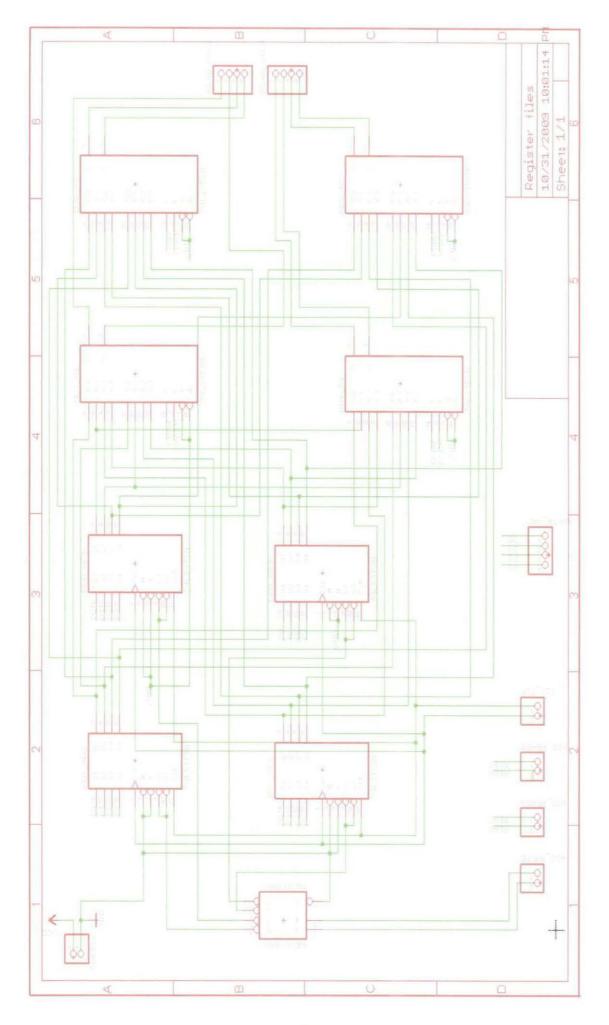

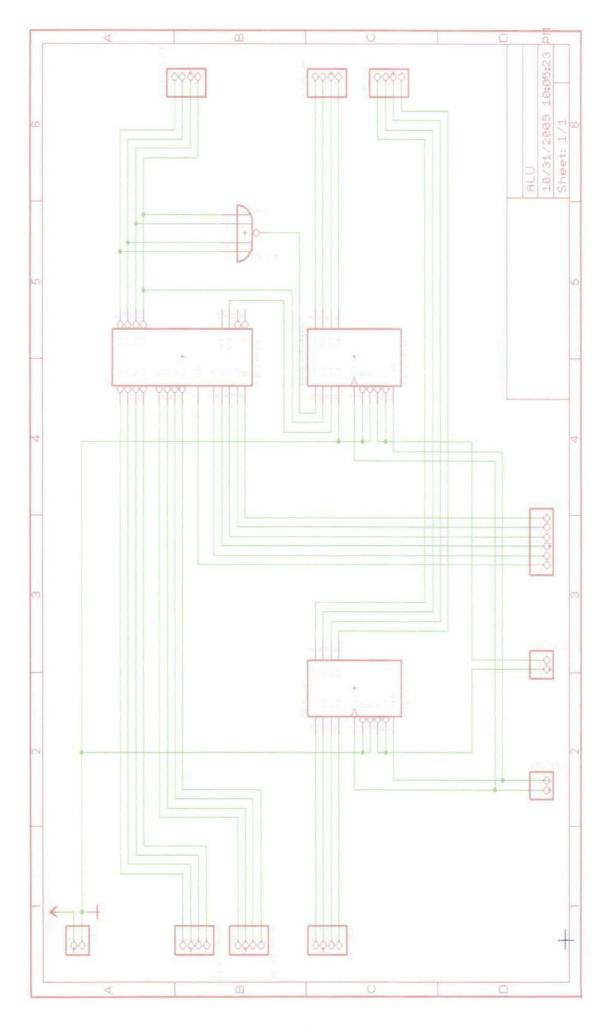

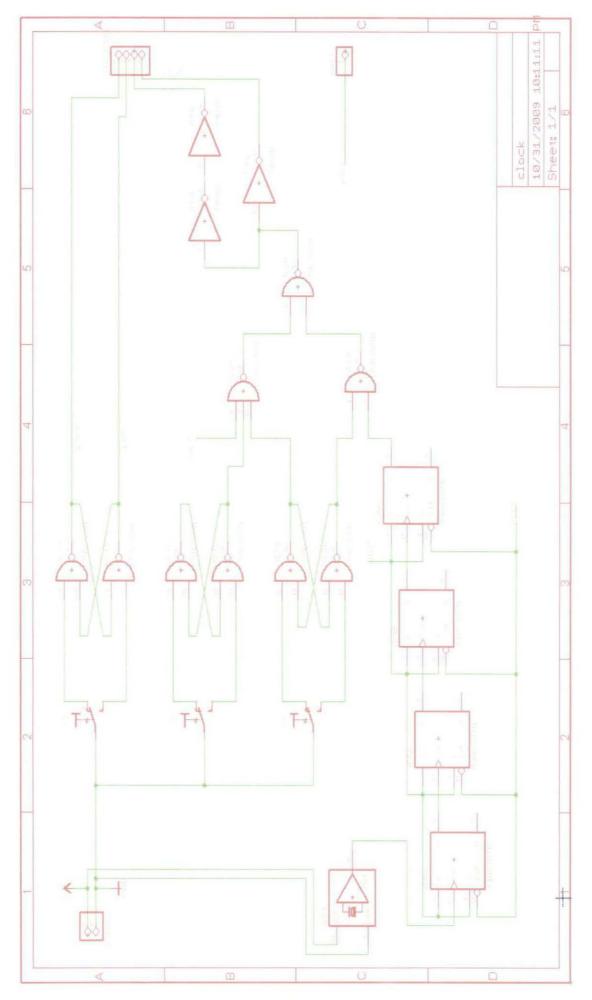

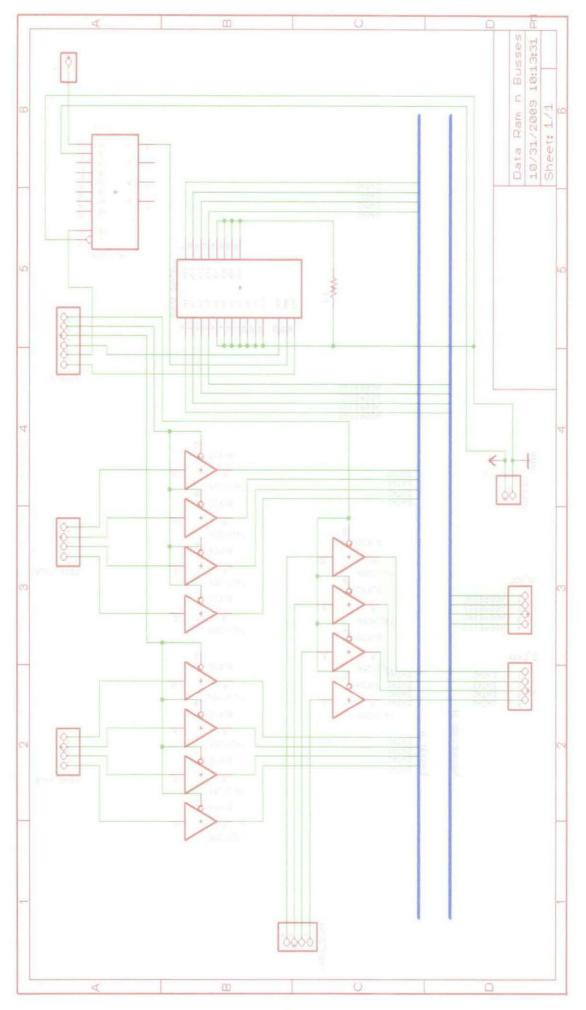

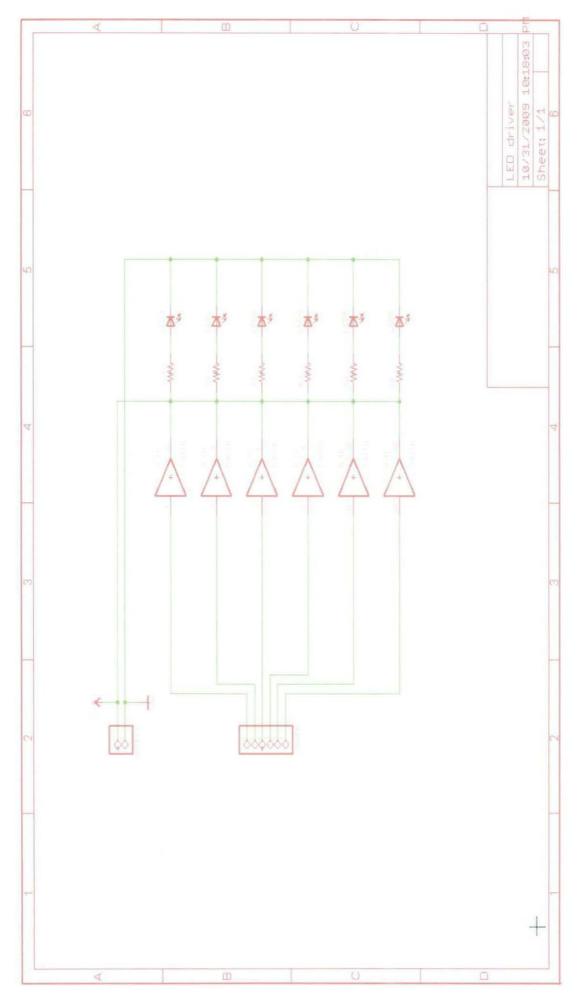

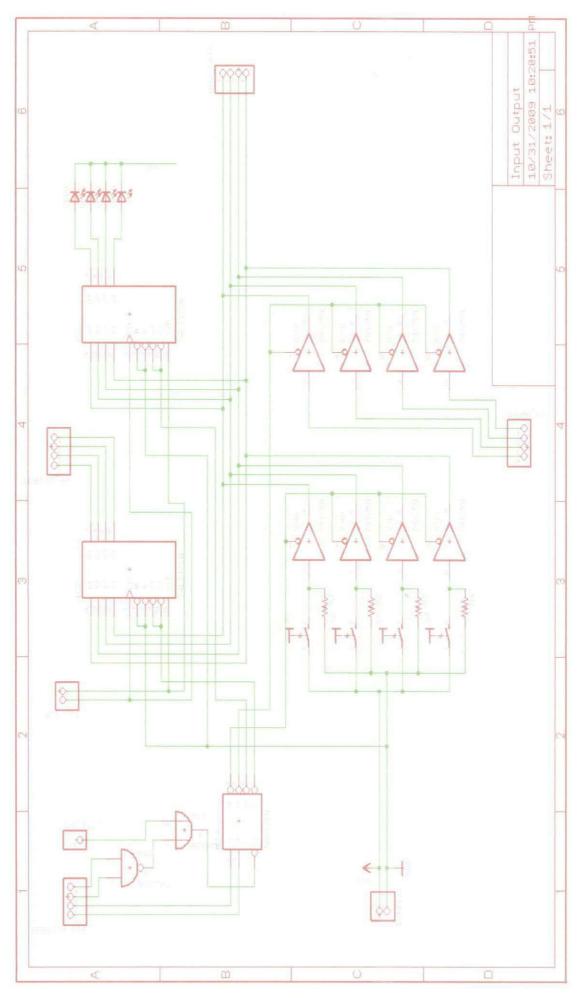

The designed schematics are provided in the appendix. Those schematics include:

- Program Counter circuit schematic

- Instruction RAM and programming circuit schematic

- Control Logic circuit schematic

- Registers file circuit schematic

- ALU unit circuit schematic

- Clock circuit schematic

- Data RAM and busses circuit schematic

- LED driver circuit schematic

- Input output circuit schematic

## 4.1.5 CPU characteristic

#### 4.1.5.1 Programming the processor

As the Instruction sets include the jump (JMP) instruction, two separate RAM is used; one for the instruction memory and the other one for data memory. To program the processor, the program will be written into the instruction memory manually by using the switch to write data into the memory.

## 4.1.5.2 Processor control

To allow the greater flexibility of the processor, microcontroller is used to store control signals instead of using control matrix to drive the control signal to each functional units. This also can reduce defect probability as using lots of gate in the control matrix.

#### 4.1.5.3 Arithmetic and Logic Unit

Based on the reference book [1], there is only ADDER IC that is used in the processor. This adder can be modified to perform subtraction too. But then, this limit the capability of the whole processor. Thus, the author has used 74181 chip to replace the former one. This allows the greater option of instructions to be included in the processor. The appropriate flag generation has also been designed for the instruction that require the comparison between two operands.

#### 4.1.5.4 Registers and data RAM

Four general purpose registers is used in the processor. This allows the flexibility of such instruction as ADD and SUBTRACT. 2Kx8 RAM has been selected to be used for storing the data of the instruction's result.

#### 4.1.5.5 Summary of CPU operation

All of the instruction will be executed in single-cycle. Half cycle of the operation is used to decode the instruction and send the control signal, data processing would also happen during this time. Another half cycle is for register writeback operation.

#### 4.1.5.6 PCB Implementation

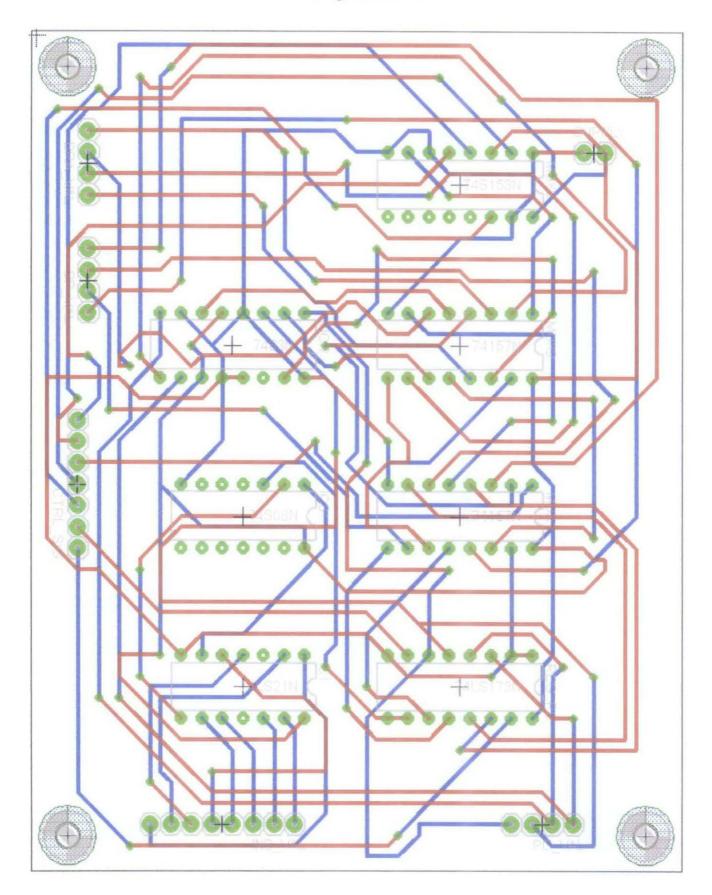

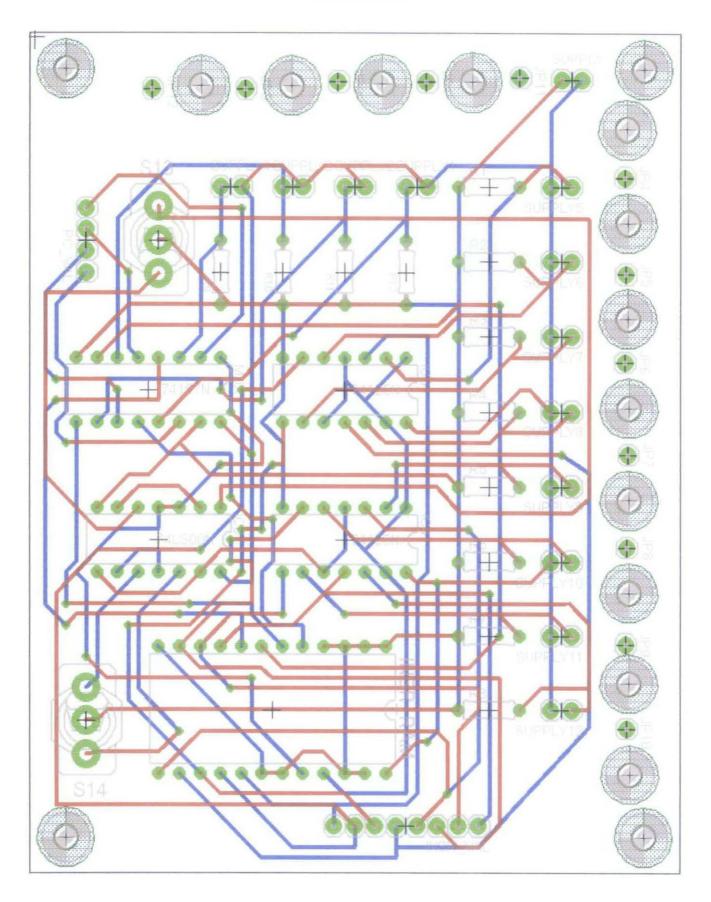

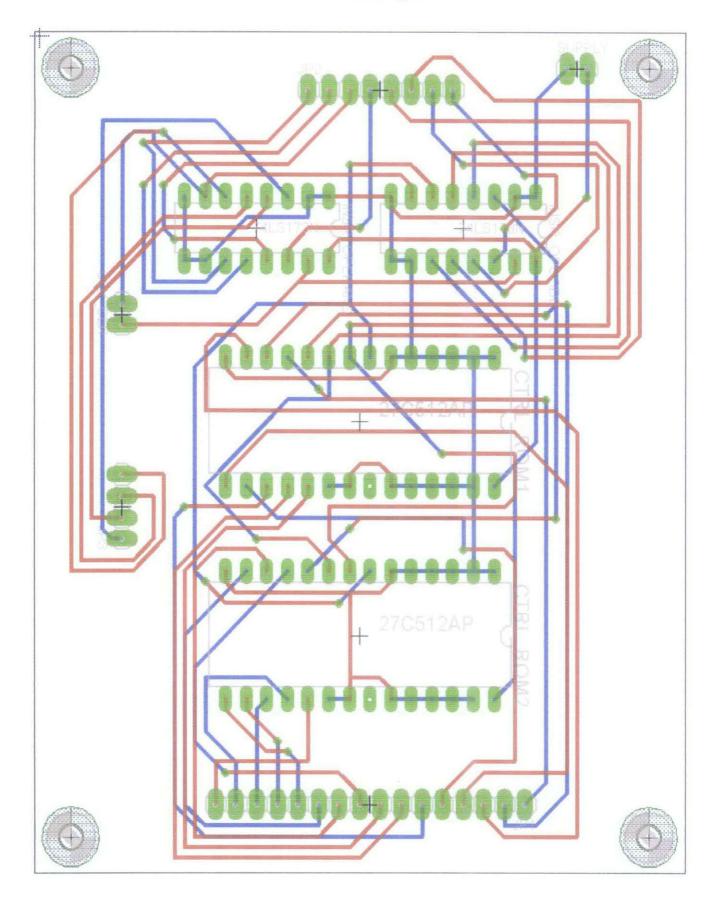

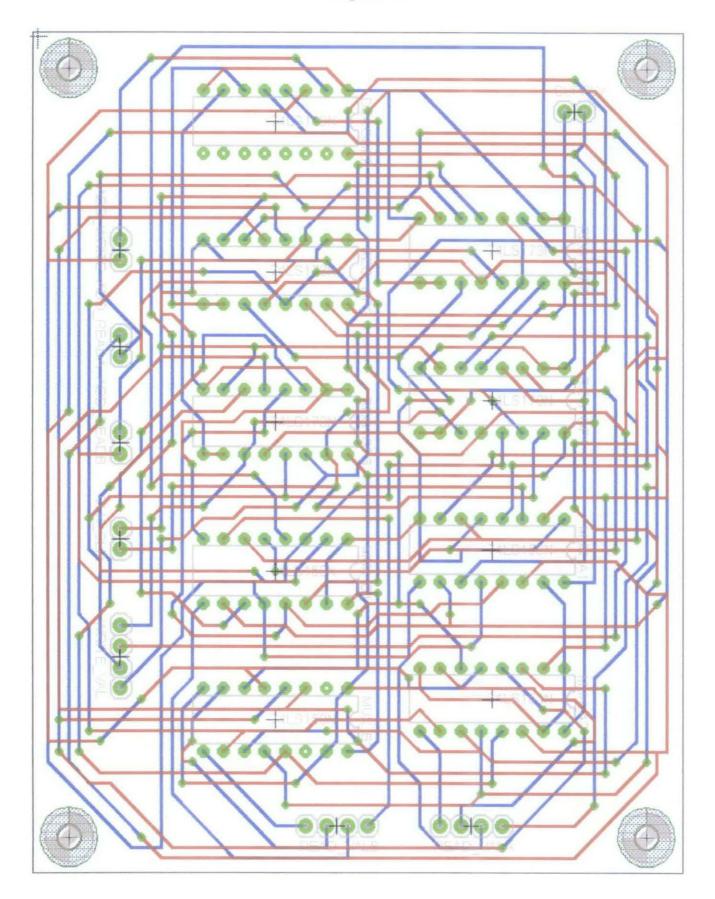

After the design of the CPU is simulated using the quartus software, the next step is to implement it into PCB. To design the PCB, the schematics for all CPU's functional units is drew using EagleCAD software. After that, the schematics are netlisted to board files. Here the actual PCB board layout is designed before it will be printed as shown in Appendix D.

## 4.2 CPU Functional Unit Control Signals

The control logic signal is configured to all CPU functional units for each instruction. The control signal will control what action the CPU functional units should takes. Table below describe the control signal of the respective CPU functional units.

| A        | 0 | )pC | od  | e |   | Pro | ogr | am  |   |   |   |   | AJ | LU |   |   |   |   | D٤ | nta 1 | RA       | M |   | Ι | M | Μ | fu |

|----------|---|-----|-----|---|---|-----|-----|-----|---|---|---|---|----|----|---|---|---|---|----|-------|----------|---|---|---|---|---|----|

| s        |   |     |     |   |   | Co  | oun | ter |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   | u | 2 | ĸ  |

| m        |   |     |     | 1 |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   | 0 | x | 2 | 2  |

|          |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   | 1 |   |    |

| $\vdash$ | 7 | 6   | 5   | 4 | 1 | 2   | 3   | 4   | 5 | 6 | 7 | 8 | 9  | 1  | 1 | 1 | 1 | 1 | 1  |       | 1        | 1 | 1 | 2 | 2 | 2 | 2  |

|          |   | -   | _   | _ |   |     |     |     |   |   |   | - |    | 0  | 1 | 2 | 3 | 4 | 5  | 6     | 7        | 8 | 9 | 0 | 1 | 2 | 3  |

|          | С | C   | С   | C | В | В   | В   | В   | B | B | В | В | С  | С  | С | C | D | D | D  | D     | D        | D | D | D | Е | Ε | Ē  |

|          | 3 | 2   | 1   | 0 | 0 | 1   | 2   | 3   | 4 | 5 | 6 | 7 | 4  | 5  | 6 | 7 | 0 | 1 | 2  | 3     | 4        | 5 | 6 | 7 | 0 | 1 | 2  |

| L        | 0 | 0   | 0   | 0 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 1  | 0  | 0 | 1 | 1 | 1 | 1  | 1     | 0        | 1 | 0 | 0 | 1 | 1 | 1  |

| D<br>R   |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| s        | 0 | 0   | 0   | 1 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 1  | 0  | 0 | 1 | 1 | 1 | 0  | 1     | 0        | 0 | 0 | 0 | 1 | 1 | 0  |

| Т        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   | -  |       |          |   |   |   |   |   | -  |

| R        |   |     |     |   |   |     |     | -   |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| М        | 0 | 0   | 1   | 0 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 1  | 0  | 0 | 1 | 1 | 1 | 1  | 1     | 1        | 0 | 0 | 0 | 1 | 0 | 0  |

| 0        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| V<br>M   | 0 | 0   | 1   | 1 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 1  | 0  | 0 |   | 1 | 0 | 1  | 1     | 1        | 1 | 1 | 0 | 0 | 1 | 0  |

| 0        | Ň | v   | L   | 1 | 1 | Ū   | Ň   | 1   | V | Ň | Ŷ | Ň |    | v  | v | 1 | 1 | v | 1  | 7     | 1        | 1 | 1 |   | v | 1 | Ŭ  |

| vī       |   |     | . 1 |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| A        | 0 | 1   | 0   | 0 | 1 | 0   | 0   | 1   | Ō | 0 | 0 | 0 | 1  | 0  | 0 | 1 | 1 | 1 | 1  | 1     | 1        | 1 | 1 | 0 | 1 | 1 | 0  |

| D        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| D        | 0 | 1   | 0   | 1 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 0 | 1  | 0  | 0 | 1 |   | , | 1- | 1     | 1        |   | _ | 0 | • |   |    |

| A<br>D   | Ů | 1   | U   | 1 | 1 | U   | V   | 1   | U | Ů | 0 | v | 1  | 0  | U | 1 | 1 | 1 | 1  | 1     | 1        | 1 | 1 | U | 0 | 1 | 0  |

| DI       |   | i   |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| S        | 0 | 1   | 1   | 0 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 1 | 0  | 1  | 1 | 0 | 1 | 1 | 1  | 1     | ì        | 1 | 1 | 0 | 1 | 1 | 0  |

| U        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| B        |   |     |     |   |   |     |     |     |   |   | ~ |   |    |    |   |   |   |   |    |       | <u> </u> |   | Ļ |   |   | Ļ |    |

| S<br>U   | 0 | 1   | 1   | 1 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | V | 0  | L  | 1 | 0 | U | 1 | ł  | 1     | 1        | 1 | 1 | 0 | 0 | 1 | 0  |

| BI       |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   | - |   |   |    |       |          |   |   |   |   |   |    |

| С        | 1 | 0   | 0   | 0 | 1 | 0   | 0   | 1   | 0 | 0 | 0 | 1 | 0  | 1  | 1 | 0 | 1 | 1 | 1  | 1     | 1        | 1 | 1 | 0 | 1 | 0 | 0  |

| м        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

| P        |   |     |     |   |   |     |     |     |   |   |   |   |    |    |   |   |   |   |    |       |          |   |   |   |   |   |    |

## Table 4 Control signal

| С  | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| м  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| PI |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| В  | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| N  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Е  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| В  | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| L  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Т  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ' |   |   |   |   |   |   |   |   |   |   |

| J  | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| М  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| P  |   |   |   |   |   |   |   |   |   |   |   |   |   | i |   |   |   |   |   |   |   |   |   |   |   |   |   |

| R  | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

| Т  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| S  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Е  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| N  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| D  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

## 4.3 CPU Hardware Fabrication

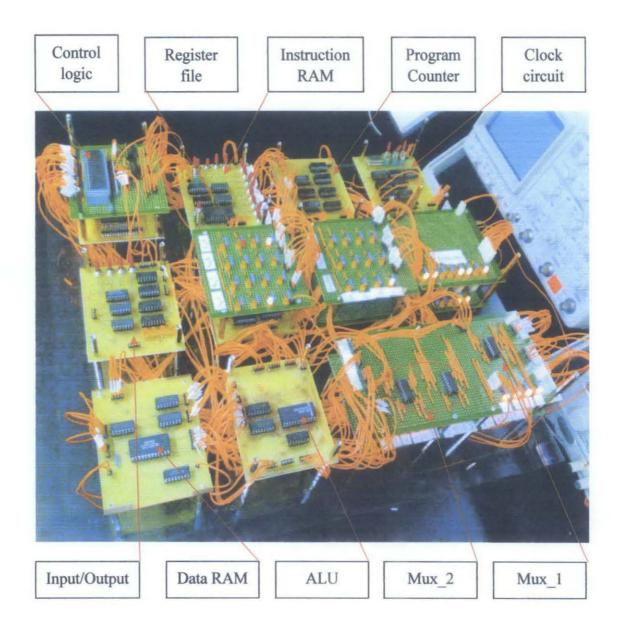

The results of the CPU fabrication phase are the overall circuit built using the TTL logic on Printed Circuit Board (PCB). Figure below illustrates the fabrication phase.

Figure 13 CPU fabricated

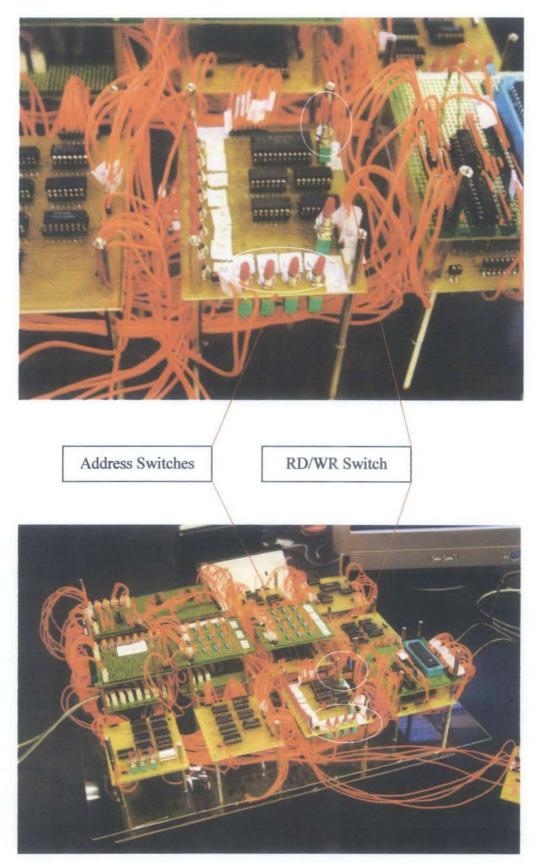

## 4.4 Graphic User Interface

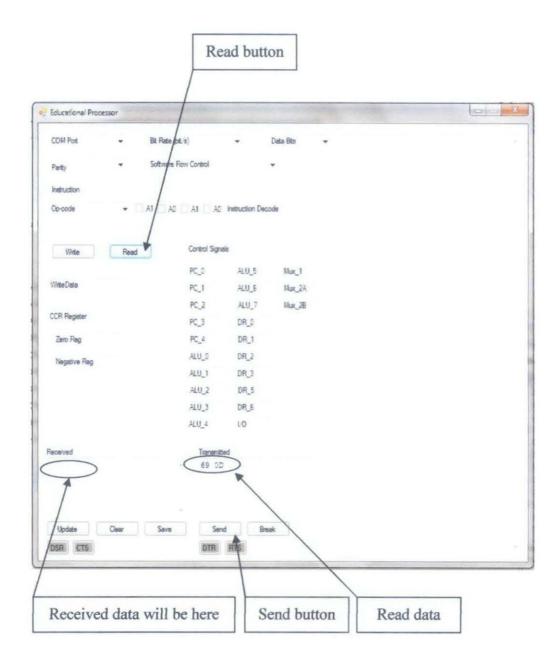

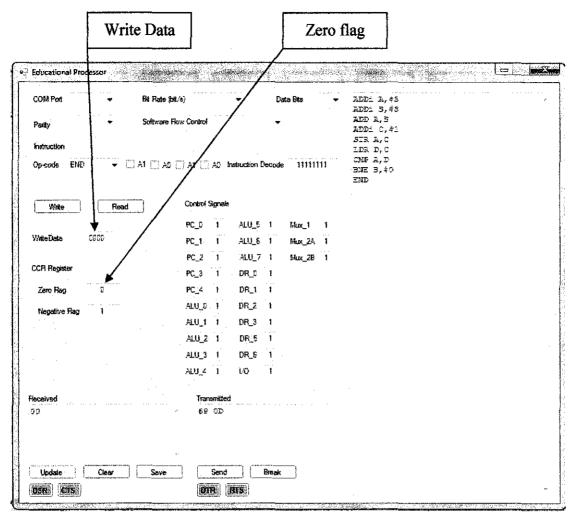

The result of the graphic user interface is a Windows application that was programmed using Visual Basic to send 8-bit instruction one by one to the CPU. User needs to program the CPU by writing the instructions from this GUI and then the instructions will be written to the CPU's instruction RAM. Figure below shows the programmed graphic user interface.

| COM Port      |       | Bit Rate (bit/s)      | -              | Data Bits  |     |  |

|---------------|-------|-----------------------|----------------|------------|-----|--|

|               |       |                       |                | a set over | . 1 |  |

| Parity        | *     | Software Flow Control |                | *          |     |  |

| Instruction   |       |                       |                |            |     |  |

| Op-code       | *     | AT AD AT AD           | Instruction De | ecode      |     |  |

|               |       |                       |                |            |     |  |

| Wite          | Read  | Control Sign          | als            |            |     |  |

|               |       | PC_D                  | ALU_5          | Max_1      |     |  |

| WiteData      |       | PC_1                  | ALU_6          | Mux_2A     |     |  |

|               |       | PC_2                  | ALU_7          | Mux_2B     |     |  |

| CCR Register  |       | PC_3                  | DR_0           |            |     |  |

| Zero Flag     |       | PC_4                  | DR_1           |            |     |  |

| Negative Flag |       | ALU_0                 | DR_2           |            |     |  |

|               |       | ALU_1                 | DR_3           |            |     |  |

|               |       | ALU_2                 | DR_5           |            |     |  |

|               |       | ALU_3                 | DR_6           |            |     |  |

|               |       | ALU_4                 | 10             |            |     |  |

| leceived      |       | Transmitt             | ed             |            |     |  |

|               |       |                       |                |            |     |  |

|               |       |                       |                |            |     |  |

|               |       | -                     |                |            |     |  |

| Update        | Clear | Save Sen              | d B            | heak       |     |  |

Figure 14 CPU graphic user interface

## 4.5 CPU-GUI Interfacing

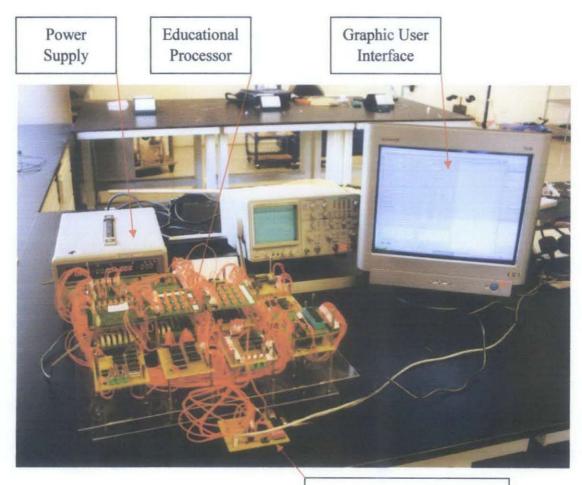

The result for processor and computer interfacing is the serial communication between microcontroller and serial port of the computer. All instructions are sent from the GUI to the CPU through this serial communication. Figure below illustrates the full system of the designed educational processor.

Microcontroller-PC Serial Communication Terminal

#### 4.6 Testing Procedure and Validation Result

For validation of the designed processor, the hardware is tested by running some test programs and the results are observed by comparing the outputs with the expected result.

Five simple test programs are used to test all the instruction including data movement, data processing (ADDi,SUBi) and flow control (BRANCH).

| Address | Instruction | Op-code | Operand1 | Operand2 |

|---------|-------------|---------|----------|----------|

| 0001    | ADDi A,#3   | 0101    | 00       | 11       |

| 0010    | SUBi A,#1   | 0111    | 00       | 01       |

| 0011    | CMPi A,#0   | 1001    | 00       | 00       |

| 0100    | BNE B,#2    | 1010    | 01       | 10       |

| 0101    | END         | 1111    |          |          |

Table 5 First Test program

This program will test the BNE instruction that does the looping until Register A content is subtracted until 0. To run the test program, below are the testing procedures.

1. The Educational Processor GUI application is opened and the GUI's serial communication setting are configured set as below:

| Table 6 | GUI's serial | communication | configuration |

|---------|--------------|---------------|---------------|

|---------|--------------|---------------|---------------|

| COM Port              | COM4 |

|-----------------------|------|

| Bit Rate (bit/s)      | 9600 |

| Data Bit              | 8    |

| Parity                | None |

| Software Flow Control | None |

| COM Port             | Parity                |                  | Rate<br>t/s) | Software<br>Control<br>Flow | Data Bit |

|----------------------|-----------------------|------------------|--------------|-----------------------------|----------|

| Educational Processo |                       |                  | /            | /                           |          |

| COM Port             | Bit Pale (bit/s)      | ./               | Data Bits    | -                           |          |

| Party                | Software Flow Control | K                | ÷            |                             |          |

| Instruction          |                       |                  |              |                             |          |

| Op-code -            | AT TAD TAT AD         | Instruction Deci | ode          |                             |          |

|                      |                       |                  |              |                             |          |

| Write Read           | Control Sign          | als              |              |                             |          |

|                      | PC_D                  | ALU_5            | Must_1       |                             |          |

| WriteElata           | PC_1                  | ALU_E            | Mux_2A       |                             |          |

| CCR Register         | PC_2                  | ALU_7            | MLH_2B       |                             |          |

|                      | PC_3                  | DR_0             |              |                             |          |

| Zero Flag            | PC_4                  | DR_1             |              |                             |          |

| Negative Flag        | ALU_D                 | DR_2             |              |                             |          |

|                      | ALU_1                 | DR_3             |              |                             |          |

|                      | ALU_Z                 | DR_5             |              |                             |          |

|                      | ALU_3                 | DR_6             |              |                             |          |

|                      | ALU_4                 | 10               |              |                             |          |

| Received             | Transmitt             | led              |              |                             |          |

|                      | ×                     |                  |              |                             |          |

|                      |                       |                  |              |                             |          |

|                      |                       |                  |              |                             |          |

| Natural Contractor   | 6                     |                  |              |                             |          |

| Update Clear         | Save Sen              | ld Brea          | sk           |                             |          |

Figure 16 GUI's serial communication configuration

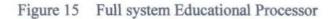

2. To write the first instruction in the instruction RAM, the first address is assigned manually from the hardware by changing the state of address switches as below.

Figure 17 Address switches and RD/WR switch

3. After the address of the first instruction is ready, which is equal to 0001, the first op-code and the respective operands are selected as shown below. The

instruction that is to be written is shown in the Instruction textbox which is equal to 01010011. Now the first instruction is ready to be sent.

| Op-code field           | First operand         | Secor         | nd operand | Instruction<br>Decode |   |

|-------------------------|-----------------------|---------------|------------|-----------------------|---|

|                         | /                     |               | /          |                       |   |

| 🥶 Educational Processor |                       |               | /          |                       | × |

| CON Port -              | Bit Pate (bit/s)      | Data          | Ben -1     |                       |   |

|                         |                       | 2.010         | /          |                       |   |

| Parity                  | Software Flow Control | *             | /          |                       |   |

| Instruction             | * *                   |               | *          |                       |   |

| Op-code +               | AI AD AI AD Contra    | uction Decode |            |                       |   |

|                         |                       |               |            |                       |   |

|                         |                       |               |            |                       |   |

| Write Read              | Control Signals       |               |            |                       |   |

|                         | PC_0 .4               | LU_5 N        | kux_1      |                       |   |

| WriteData               | PC_1                  | LU_6 N        | lax_2A     |                       |   |

| CCD Desister            | PC_2 )                | 4LU_7 N       | lux_2B     |                       |   |

| CCR Register            | PC_3 D                | R_0           |            |                       |   |

| Zero Flag               | PC_4 I                | DR_1          |            |                       |   |

| Negative Flag           | ALU_0 C               | 0R_2          |            |                       |   |

|                         | ALU_1 C               | )R_3          |            |                       |   |

|                         | ALU_2                 | )R_5          |            |                       |   |

|                         | ALU_3 C               | R_6           |            |                       |   |

|                         | ALU_4                 | 0             |            |                       |   |

| Received                | Transmitted           |               |            |                       |   |

| 1000100                 | 1100.001000           |               |            |                       |   |

|                         |                       |               |            |                       |   |

|                         |                       |               |            |                       |   |

|                         |                       |               |            |                       |   |

| Update Clear            | Save Send             | Break         |            |                       |   |

| DSR CTS                 | DTR                   | 8             |            |                       |   |

Figure 18 Writing a CPU Instruction

4. To send the first instruction, the "Write" button is clicked and the instruction is transferred to the "Transmitted textbox". Here the instruction is prepared in order to be transmitted to the CPU hardware through microcontroller via 8-bit serial communication. Figure below illustrates this step. To transmit the content in the "Transmitted textbox", "Send" button is clicked. The instruction is framed with 6F and 0D which is refer to character "o" as output and carriage return respectively. The microcontroller will receive three characters which are 6F, instruction and also 0D, and then the microcontroller will give an 8-bit output as instruction to the hardware. At the same time, the appropriate control signals are shown to ensure that the op-code of the instruction will decoded to the right control signal.

| COM Pot       Bit Rate (bit./s)       Data Bits         Partly       Software Row Control       *         Instruction       Op-code       ADI       AI       AD       Instruction Decode       DIDIDD11         Write       Read       Control Signals       *       *       Nex_1       0         WriteData       PC_0       1       ALU_5       0       Max_1       0         WriteData       PC_1       0       ALU_5       1       Max_2A       1         CCR Register       PC_3       1       DR_0       1       Zero Riag       PC_4       0       DR_1       1         Negative Riag       ALU_0       0       DR_2       1       ALU_1       0       DR_3       1                                                                                                            |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| COM Port     Bit Rate (bt./s)     Data Bits       Perty     Software Row Control     -       Instruction     -     -       Op-code     ADDI     -       A1     A0     A1       Vite     Read     Control Signals       PC_0     1     ALU_5     0       NiteData     PC_1     0       ALU_5     1     Mux_1     0       ViteData     PC_2     0     ALU_5     1       CCR Register     PC_3     1     DR_0     1       Zero Rag     PC_4     0     DR_1     1       Negative Rag     ALU_0     0     DR_2     1                                                                                                                                                                                                                                                                       |   |

| Party       Software Row Control         Instruction         Op-code       ADDI         A1       A0         PC_0       1         ALU_5       0         Mux_28       0         CCR       PC_4         A1       D         A1       D         A1       D         D       DR_1         A1 |   |

| Pary         Instruction         Op-code       ADDI         A1       A0         A1       A0         Instruction       Decode         Decode       ADDI         Write       Read         Control Signels         PC_0       1         ALU_5       0         MiteData       PC_1         PC_2       0         ALU_5       1         Mux_2A       1         PC_2       0         ALU_7       1         Mux_2B       0         CCR Register       PC_3         PC_4       0         DR_0       1         Zero Reg       PC_4         ALU_0       0         DR_2       1                                                                                                                                                                                                                   |   |

| Op-code       ADU       A1       AD       A1       AD       Instruction Decode       D1010011         Write       Read       Control Signels       PC_0       1       ALU_5       0       Mux_1       0         WriteData       PC_1       0       ALU_5       1       Mux_2A       1         CCR Register       PC_3       1       DR_0       1         Zero Reg       PC_4       0       DR_1       1         Negative Flag       ALU_0       0       DR_2       1                                                                                                                                                                                                                                                                                                                  |   |

| Wite         Read         Control Signels           PC_0         1         ALU_5         0         Mux_1         0           WriteDate         PC_1         0         ALU_5         1         Mux_2A         1           PC_2         0         ALU_7         1         Mux_2B         0           CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Flag         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                 |   |

| PC_0         1         ALU_5         0         Mux_1         0           WhiteData         PC_1         0         ALU_6         1         Mux_2A         1           PC_2         0         ALU_7         1         Mux_2B         0           CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Flag         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                                                                     |   |

| PC_0         1         ALU_5         0         Mux_1         0           WhiteData         PC_1         0         ALU_6         1         Mux_2A         1           PC_2         0         ALU_7         1         Mux_2B         0           CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Flag         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                                                                     |   |

| WriteData         PC_1         0         ALU_6         1         Mux_2A         1           PC_2         0         ALU_7         1         Mux_2B         0           CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Flag         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| PC_1         U         ALU_5         I         Mux_2x         I           PC_2         0         ALU_7         1         Mux_28         0           CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Reg         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| CCR Register         PC_3         1         DR_0         1           Zero Reg         PC_4         0         DR_1         1           Negative Reg         ALU_0         0         DR_2         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |