#### DESIGN AND SIMULATE PULSE GENERATOR CIRCUIT

By

## FAZRUL SYAHRIN BIN SHAHADAN

### FINAL PROJECT REPORT

Submitted to the Electrical & Electronics Engineering Programme in Partial Fulfillment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2007 by Fazrul Syahrin bin Shahadan, 2007

# **CERTIFICATION OF APPROVAL**

### **DESIGN AND SIMULATE PULSE GENERATOR CIRCUIT**

by

Fazrul Syahrin bin Shahadan

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved:

Mohl Moran

A.P Dr. Mohammad bin Awan Project Supervisor

# UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

December 2007

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

\_ conflict.

Fazrul Syahrin Shahadan

### ABSTRACT

The main purpose of the project is to design and simulate pulse generator impulse based for Ultra Wide Band (UWB) applications. The UWB technology is defined by the Federal Communications Commission's (FCC), the signal must have bandwidth of greater than 500MHz. The structure of the pulse generator is based on Complementary Metal Oxide Semiconductor (CMOS) and the topology of the circuit is adaptation of CR-(RC)<sup>n</sup> pulse shaping network. The pulse generator circuit consists of variable length rectangle pulse generator, which mingles up cascaded inverter and N-voltage controlled with a CMOS quasi-Gaussian pulse-shaping filter. In this project, the author successfully designed and simulated the pulse generator. The simulation is done using Virtuoso Analog Design Environment (Cadence) which is able for integrated design circuit and used AMI 0.6um transistor technology. The circuit takes 100MHz pulse as the input. Through the simulation, the author has proved to generate pulse with 660MHz passed frequency. This shows that the topology chosen is able to generate pulse for high frequency purposes.

#### ACKNWOLEDGEMENTS

I would like to take this opportunity to thank god Almighty for his grace and endless bounty and my supervisor Associate Professor Dr Mohammad Awan for his help and support throughout the course of this project. I appreciate the opportunity he has given to me to work on the project with which I gained new experience in many areas.

I would also like to thank to Mr Said, PHD student who help me a lot and guidance especially for tutoring the Spectre cadence simulation software. Also not forget Mr Asnan Seman who gives support from the beginning of the project and all my friends

Last but not least, my parents who have assist me financially to ensure the completion of the project.

Thank you very much

Fazrul Syahrin Shahadan

# TABLE OF CONTENTS

| CHAPTER 1:INTRODUCTION1                           |

|---------------------------------------------------|

| 1.1 BACKGROUND OF STUDY1                          |

| 1.2 PROBLEM IDENTIFICATION                        |

| 1.3 OBJECTIVES                                    |

| CHAPTER 2: LITERATURE REVIEW4                     |

| 2.1 INTRODUCTION4                                 |

| 2.1.1 The Gaussian Pulse4                         |

| 2.1.2 The Gaussian Mono-cycle Pulse5              |

| 2.2 LOGIC CIRCUIT CHARACTERIZATION                |

| 2.2.1 Noise Margin                                |

| 2.2.2 Propagation Delay7                          |

| 2.2.3 Power Dissipation7                          |

| 2.2.4 Fan-In and Fan-Out7                         |

| CHAPTER 3:METHODOLOGY8                            |

| 3.1 DESIGN FLOW8                                  |

| 3.1.1 Literature Study9                           |

| 3.1.2 Research and Design Consideration           |

| 3.1.3 Tools and Equipment Needed                  |

|                                                   |

| CHAPTER 4: GAUSSIAN PULSE GENERATOR               |

| CHAPTER 4: GAUSSIAN PULSE GENERATOR               |

|                                                   |

| 4.1 INTRODUCTION                                  |

| 4.1 INTRODUCTION104.2 RECTANGLE PULSE GENERATOR13 |

| CHAPTER 5: SIMULATION RESULTS AND DISCUSSION  |

|-----------------------------------------------|

| 5.1 INTRODUCTION                              |

| 5.2 SIMULATION SETTING21                      |

| 5.3 SIMULATION RESULT AND DISCUSSION23        |

| CHAPTER 6: CONCLUSION AND RECOMMENDATIONS     |

| 6.1 CONCLUSION                                |

| 6.2 RECOMMENDATIONS                           |

| 6.2.1 Design with Different Topology          |

| 6.2.2 Design Applications Improvement         |

| REFERENCES                                    |

| PPENDICES                                     |

| APPENDIX A: PMOS transistor process parameter |

| APPENDIX B: NMOS transistor process parameter |

# LIST OF FIGURES

| Figure 1: Overall concept of pulse generator design                         | 2  |

|-----------------------------------------------------------------------------|----|

| Figure 2: Gaussian Pulse and Frequency Spectrum                             | 5  |

| Figure 3: Gaussian Monocycle Pulse and Frequency Spectrum                   | 5  |

| Figure 4: Flow of pulse generator design                                    | 8  |

| Figure 5: UWB spectrum mask                                                 | 11 |

| Figure 6: Overall block diagram of UWB transmitter                          | 11 |

| Figure 7: Overall block diagram of pulse generator                          | 11 |

| Figure 8: Pulse shaping variations method                                   | 12 |

| Figure 9: The CMOS inverter circuit diagram                                 | 15 |

| Figure 10: Example of CMOS inverter chain                                   | 16 |

| Figure 11: Circuit for variable delay buffer using starved inverter         |    |

| Figure 12 : Rectangle pulse circuit diagram                                 | 19 |

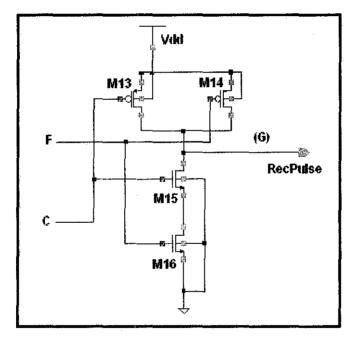

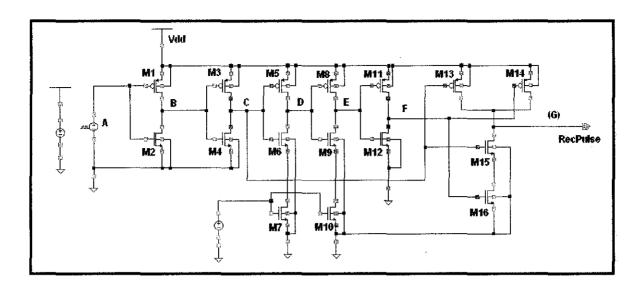

| Figure 13: Quasi Gaussian Shaping Filter circuit                            | 20 |

| Figure 14: Gaussian pulse in theoretically                                  | 20 |

| Figure 15: Model library setup for loading the CMOS technology used         | 22 |

| Figure 16: Transient simulation setting                                     | 22 |

| Figure 17: Delay calculation for Rectangle Pulse circuit                    | 23 |

| Figure 18: Various parameters, which can be obtained by calculator tools    | 24 |

| Figure 19: Timing diagram of the pulse generator                            | 25 |

| Figure 20: Rectangle pulse output result achieved 500MHz pass frequency     | 25 |

| Figure 21: The pulse generator output result achieved 660MHz pass frequency | 26 |

| Figure 22 : Rectangle pulse circuit diagram                                 | 28 |

| Figure 23: Quasi Gaussian Shaping Filter circuit                            |    |

.

# LIST OF TABLES

| Table 1: The substitution of waveform labeling               | 24 |

|--------------------------------------------------------------|----|

| Table 2: Aspect ratio value of the PMOS and NMOS transistors | 27 |

# LIST OF ABBREVIATIONS

: Complementary Metal Oxide Semiconductor CMOS : Ultra Wide Band UWB NM : Noise Margin : Wireless Local Area Network WLAN FCC : Federal Communications Commission's SRD : Step Recovery Diode SiGe : Silicon Germanium : Radio Frequency Identification RFID : Wireless Personal Area Network WPAN VTC : Voltage Transfer Characteristic : Pulse Repetition Frequency PRF

# **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Background of Study

The advantage of CMOS process in fabricating integrated circuits makes it the popular choice for digital circuit design. This is due to the low power consumption and costless fabrication involve.

Since the CMOS was invented in 1963 by Frank Wanlass at Fairchild Semiconductor, the inventor realized that the CMOS shrank standby power by six times of magnitude over equivalent bipolar or PMOS logic gates [1]. Then more inventions were created in various type of fields or applications such as electronics, computer system, imaging and wireless technology. The invented of wireless transceiver for Bluetooth and IEEE 802.11 WLANs is the example of applications of CMOS [2]. The performance of CMOS circuit at high frequency is comparable to those using bipolar devices due to CMOS aggressive scaling [2]. Ultra Wideband is one of the applications or technologies that can be applied for a wireless system

Ultra Wideband (UWB) communication is different from all other communication techniques due to employing short time pulses and wide bandwidth to communicate between transmitter and receiver. The UWB signal required bandwidth greater than 500MHz, which has been defined by the Federal Communication Commission (FCC).

UWB has a potential for low transmit power design, high performance in multipath channels and ability to work with low signal to noise ratio. The adaptation of CMOS architecture gives simpler transceiver. The transmission of low power pulse eliminates the need for a power amplifier in UWB transmitter. Besides, the carrier less for UWB transmission, design do not need mixers and local oscillators to translate the carrier frequency to the required frequency band and consequently there is no need for carrier recovery stage at the receiver end. Because of that, CMOS design transmitter is noticeable less complicated and cheaper to design.

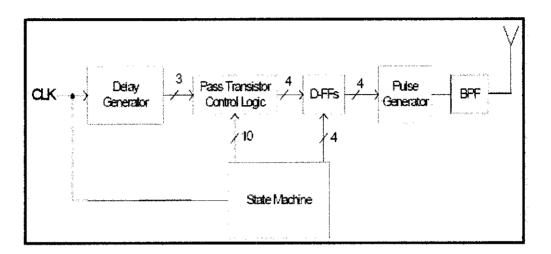

Figure 1: Overall concept of pulse generator design

Figure 1 shows the overall concept of pulse generator that used by [4]. Various CMOS design topology of generating pulse generator presented by [4, 7, 16] and different approaches of design and adopted. Before CMOS pulse generator design was introduced, there are other approaches for generating pulse generator such as step recovery diode (SRD) [17], avalanche transistor [19] and others. The criterion of low power design make CMOS design topology is more popular for VLSI design approach. Among the designs, pulse sources step recovery diode (SRD) is the most popular. Its employ graded doping when the doping level of the semi conductive materials is reduced as the PN junction is approached. This produces an abrupt turn-off by allowing a very fast release of stored charge when switching from forward to reverse bias. Thus it supports high repetition (up to several hundreds of MHz) and has been widely used in applications like high speed sampling circuitry. An input trigger source drives the SRD and generates a step. The step then passes through the short circuited transmission line

and gets reflected with 180 degree phase shift. The design of the broadband baluns was presented in many publications, but the circuits are rather complicated and take a space in the final design and introduced unwanted losses [4, 6, 7].

#### **1.2 Problem Identification**

The project title is "Design and Simulate Pulse Generator Circuit". Therefore, the student is requires to design and simulate a pulse generator using CMOS technology. The additional work is to design a pulse generator in high frequency at least 500MHz. The design process includes determining the circuit parameter such as transistor aspect ratio, design approaches etc. to obtain a pulse that can be generated at high frequency.

### **1.3 Objectives**

The objectives of this project are:

- 1. To design and simulate the pulse generator circuit that can transmit data at high frequency (0-900MHz) with the UWB technology application.

- 2. To apply knowledge and hands-on experiences that independently working to the project with the guidance of a supervisor.

- 3. To simulate and design circuit with Spectre software (Virtuoso Analog Design Environment and Virtuoso Analog layout Design).

### **CHAPTER 2**

## LITERATURE REVIEW

#### **2.1 Introduction**

The pulse generator transmitter is combination of processes such as modulating, generating (obtain the pulse signal), transmitting signal. The pulse generator circuit that has to be designed is based correlated to UWB technology. Understanding the basic knowledge of Gaussian pulse and the basic of CMOS is the essential to design the pulse generator. Since the focus of this project is on the development of a pulse generator for an impulse-based system, it is essential to describe the type of pulses. The types of pulses are Gaussian pulses and Gaussian Monocycle pulses [7], [17].

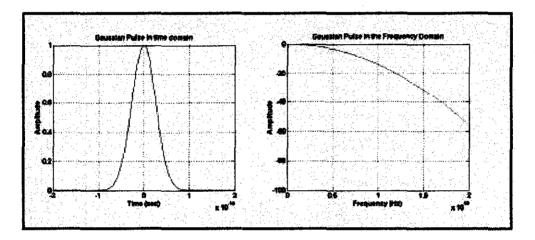

#### 2.1.1 The Gaussian Pulse

Before generating an ultra short pulse, the desired wave shape must be determined for the system. There is various pulse shape design as presented by [15]. The most popular pulse shape for UWB communication systems is the Gaussian pulse since it has the lowest side-lobe compared to a rectangular or sinusoidal pulse because of Gaussian pulse contained most energy in the spectrum.

A Gaussian pulse has the Gaussian shape as shown in Figure 2 and expressed as:

$$V(t, f_c, A) = Ae^{-2(\pi t f_c)^{-1}}$$

(1)

where A is the amplitude of the monocycle pulse, and  $f_c$  is the center frequency [5]. The real Gaussian pulse cannot be realized by equation (1), but can be approximated by CR-(RC)<sup>n</sup> pulse shaping network in the form of [9].

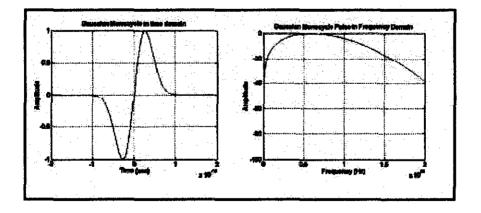

#### 2.1.2 The Gaussian Monocycle Pulse

Taking the derivative of the equation for the Gaussian pulse (2), we can obtain the equation for a Gaussian monocycle pulse.

$$V(t, f_{c}, A) = 2\sqrt{e}A \pi t f_{c} e^{-2(\pi t f_{c})^{2}}$$

(2)

The centre frequency of the monocycle pulse is usually defined as  $(\pi\tau)^{-1}$  Hz, where  $\tau$  is defined as the time between the maximum and minimum points of the monocycle pulse [5]. Figure 3 shows the Gaussian monocycle pulse and its frequency spectrum. There are various of pulse based introduced in [5, 7].

Figure 2: Gaussian Pulse and Frequency Spectrum

Figure 3: Gaussian Monocycle Pulse and Frequency Spectrum

#### 2.2 Logic Circuit Characterization

To design a pulse generator circuit, there are some parameters that need to be understood especially CMOS basic operation, logic circuit characterization, circuit structure and the other relationship parameter to the design [10]. The most important factor that drives CMOS design development is dissipated the lowest power compare to other digital IC technology and logic circuit families. Some reasons for displacing conventional technology to CMOS technology are summarized below.

- The power dissipation of CMOS is less than the BJT. This factor drives to pack more CMOS circuit on a chip compare to BJT technology.

- High input impedance of MOS allow designer to use charge storage for temporary storage of information in both logic and memory circuit.

- The technology is developing until 0.06um utilize channel as the features size of the CMOS circuit.

For the next sub section will be discussed the parameters that usually used to characterize the performance and operation of logic circuit family.

#### 2.2.1 Noise Margin

Noise margin is the amount by which a signal exceeds the minimum amount for proper operation. The analysis of static operation logic circuit characterize by Voltage Transfer Characteristic (VTC) to evaluate the noise margin. From the VTC we can obtain the  $V_{OH}$ ,  $V_{IH}$ ,  $V_{OL}$ , and  $V_{IL}$  and evaluate the performance. The robustness of a logic circuit family determines by its ability to reject noise and thus the noise margin NM<sub>H</sub> and NM<sub>L</sub> [9].

$$\mathbf{N}\mathbf{M}_{\mathrm{H}} = \mathbf{V}_{\mathrm{OH}} - \mathbf{V}_{\mathrm{IH}} \tag{3}$$

$$NM_{L} = V_{OL} - V_{IL} \qquad (4)$$

#### 2.2.2 Propagation Delay

Propagation delay, symbolized  $t_p$ , is the time required for a digital signal to travel from the input(s) of a logic gate to the output. Obviously the shorter propagation delay the higher speed of logic circuit family can operates. The propagation delay defines as;

$$\mathbf{t}_{\rm p} = 0.5 \left( \mathbf{t}_{\rm pLH} + \mathbf{t}_{\rm pHL} \right) \tag{5}$$

#### 2.2.3 Power Dissipation

Power dissipation is an important issue in digital circuit design. The reason of reducing the gate power is to maximizing the number of gates on a chip. Thus, a compact and power effectives chip can be produced. There are two types of power dissipation in a logic gate; static and dynamic dissipation. Static dissipation occur when the absence of switching action whereas dynamic dissipation happen the only if gate is switched. An inverter operates from a power supply  $V_{DD}$  and driving a load capacitance  $C_L$ , dissipates dynamic power  $P_D$ , as f, the frequency at which the inverter is being switched [10].

$$P_{\rm D} = V_{\rm DD} C_{\rm L} f \tag{6}$$

#### 2.2.4 Fan-In and fan-Out

Fan-in of a gate is number of the inputs. In the other hand, the fan-out is the maximum number of similar gates that a gate can drive while remaining within guaranteed specification [10]. The fan-out can reduce  $V_{OH}$  and  $NM_{H}$ . This will affect the level of noise in the design.

# CHAPTER 3 METHODOLOGY

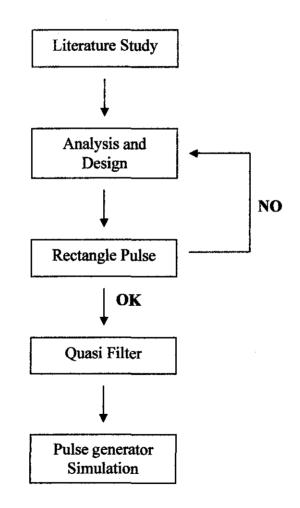

### 3.1 Design Flow

In order to design a pulse generator, the author to understand the basic concept of pulse generator it self and make use of all references related. Figure 4 shows the overall design flow for the pulse generator circuit.

Figure 4: Flow of pulse generator design

#### 3.1.1 Literature Study

Figure 3 shows the design flow for the pulse generator. In the flow chart, the author begins the design phase by doing the literature review. The references such as [5, 9, 10, 14] brief deeply the author the way of designing the pulse generator. Among the focus in activity is to find the suitable logic style and the existing circuit that can implemented for high frequency operation. Among the sources of reference, include:

- i. IEEE explore: A lot of references and technical articles that discuss about the pulse generator design generally. These references can be a guild line for designing pulse generator circuit.

- ii. UTP library: Most of the technical books are available here.

- iii. The Internet: Online resources also provided many references for the circuit design, parameters assumption, fundamental of UWB and others.

#### 3.1.2 Research and Design Consideration

A lot of sources that has been carried out for research on UWB technology and the pulse generator circuit design such as via internet and books that available at library. The pulse generator circuit is based on the CMOS technology. Thus, the author needs to study and understand the fundamental of CMOS circuit design. Reference from [10] refreshed the author a lot to understand the fundamental of designing of CMOS circuit design. Several references describe more details in design of pulse generator circuits with various type of topology and design approach. The most important thing is the design of the pulse generator circuit must fulfill the objective of the project; to design and simulate high frequency pulse generator circuit. Briefly, for this type of design, the modulated signal will be the input of the pulse generator. The designing process developed by using Spectre.

#### 3.1.3 Tools and Equipment Needed

The required software to design pulse generator circuit can be done by using P-spice or Spectre.

#### **CHAPTER 4**

#### **GAUSSIAN PULSE GENERATOR**

#### 4.1 Introduction

The Federal Communication and Commission (FCC) has classified the three bands range 0-960MHz, 3.1-10.6GHz and 22-29GHz [8]. From the previous designs, the first band will result better low power consumption, lower complexity of design and error and lower complexity. First, the desired wave shape must be determined either impulse based or multiple band pulse will be used for the design. The most popular pulse shape for UWB communication system is the Gaussian pulse due to the accurate location awareness and strong multi-path fading resistance compared to the other pulses. Figure 5 below shows the spectrum mask and occupying a bandwidth of at least 500 MHz or more than 20% of the center frequency, which defined by the FCC. For pulse generator design, it is a requirement of the designers to fulfill the FCC power spectrum mask [18]. The scope of the project is designing the pulse generator circuit which one of the essential part in UWB transmitter showed by Figure 6. As mentioned before, this is one of the designs topology of designing impulse based pulse generator as shown as Figure 7.

#### CHAPTER 5

# SIMULATION RESULTS AND DISCUSSION

#### 5.1 Introduction

As the objectives mentioned earlier, the project required the author to design and simulate pulse generator circuit. It was a successful achievement by the author as the completion of the project. The simulation done by using Virtuoso Analog Design (Spectre) with AMI0.16um CMOS transistor technology. The software is suitable for this project rather than PSPICE or Multisim because the project itself involve micro technology analogue IC design.

#### **5.2 Simulation Setting**

In Spectre window, analysis chosen is transient with simulation time 100ns and time step 0.05ns. In this simulation, there is no convergence problem as the time step is sufficiently small to calculate the initial bias point required by Virtuoso analogue Design Environment to complete the job. Figure 15 below shows the essential step which library model setup as its loading the CMOS technology that desired to use. The transient analysis setting setup gives the value of stopping time at 100ns as shows on Figure 16. For the simulation, the supply voltage is 1.8V and bias voltage supplied by the voltage of 1.4V. The value of time constants can be adjusted in three ways. There are varied the transistor sizing, increasing the number of inverters and adding voltage controlled delay element. All three methods have their own advantages and disadvantages. Transistor sizing is simple to design, but it may require huge transistors in the last section. The voltage-controlled delay element can offer flexibility at the cost of an extra control signal but the tuning range is not too high. All three approaches can be applied together in order to get a better result. Figure 17 below shows the delay calculation setting for the rectangle pulse circuit design.

| )        |             |                          |       | spectre0: I | Model  | Library | Setup                                  |   | Jan ya shiri a sa s |         |

|----------|-------------|--------------------------|-------|-------------|--------|---------|----------------------------------------|---|------------------------------------------------------|---------|

| OK       | Cancel      | Defaults                 | Apply |             |        |         |                                        |   | ÷.                                                   | H       |

| #Disab]  | le Model    | Library P                | ile   | 1           |        |         | 1994 - Carlon Barrison and an array of | 5 | Section                                              | Englike |

|          |             | binary/ncs<br>binary/ncs |       |             |        |         |                                        |   | 1                                                    | Disable |

|          |             |                          |       |             |        | ÷       |                                        |   |                                                      | եր      |

|          |             |                          |       |             |        |         |                                        |   |                                                      | Down    |

| lodel Li | ibrary File | n an<br>Taonaichte       |       |             | .*     |         | e 1.                                   |   | Section (opt.)                                       |         |

|          |             |                          |       |             |        |         |                                        |   |                                                      |         |

|          |             | Delete                   | Осына |             | i File | 1       |                                        |   |                                                      | Browse  |

Figure 15: Model library setup for loading the CMOS technology used

|              | ıs: Real<br>n Setu |                                       | yses  | Varia | bles Out | tputs Simuk |            |                   |         | r: spectr | e ∶t<br>, Help                 |

|--------------|--------------------|---------------------------------------|-------|-------|----------|-------------|------------|-------------------|---------|-----------|--------------------------------|

|              | Desi               | gn                                    |       |       |          |             | nalyses    |                   |         |           | ٠Ę                             |

| Library      | <b>EE4</b> 613     | ∃_ic_d€                               | esign | #     | Туре     | Argume      |            | · · · · · · · · · |         | Enable    | ר AC<br>TRAN ח<br>DC           |

| Cell<br>View | pulse_<br>schema   | _genera<br>atic                       | ator_ | 1     | tran     | 0           | 100n w     | ode.              |         | yes       | 300<br>1 1 1<br>1 7 1<br>X Y Z |

| D            | esign Va           | ariables                              |       |       | :        |             | Outputs    |                   |         |           | Ľ₽,                            |

| # Na         | ne                 | Value                                 |       | #     | Name/Si  | ignal/Expr  | Value      | Plo               | t Save  | March     | 34                             |

| <br>         |                    |                                       |       |       |          |             |            | н<br>11 М         |         |           | 18                             |

|              |                    | · · · · · · · · · · · · · · · · · · · |       |       |          | a tu tu     |            | · .<br>. ·        | 1       |           | 謬                              |

| · .          | , s. 1             |                                       | · .   | · .   |          | F           | lotting mo | de:               | Replace | <u> </u>  | $\mathbb{N}$                   |

Figure 16: Transient simulation setting

| Applications Actions                |                                             | Mon Sep 24, 11:12 AM 📢  |

|-------------------------------------|---------------------------------------------|-------------------------|

|                                     | Calculator                                  |                         |

| Window Tools Memories Cons          |                                             |                         |

| /home/cadence1/cadence/simulat      | lon/pulse_generator_defaultsetting          | ;/spectre/schematic/psf |

| Selection choices                   |                                             |                         |

| 🗹 clip graph selection              | ran an de ovende dans                       | TTAKE T                 |

| offO familyO waveO v                | t <b>e it</b> o                             |                         |

|                                     |                                             |                         |

| delay(\T("/net0105") 1.5 1 "rising" | 'VT("/net0137") 1.5 1 "rising" 0 0 n        | il nil )                |

| Append 🔻 🔽 🏢                        | delay                                       |                         |

|                                     |                                             |                         |

| Clear Undo Eval                     | Signal1 VT("/net0105")                      |                         |

| 1/x eex Cist Enter                  | Signal2 VT("/net0137")                      |                         |

| + 7 8 9                             | Threshold Value 1 1.5                       |                         |

| - 4 5 6                             |                                             |                         |

| x 1 2 3                             | Edge Number 1 1                             |                         |

| / 0 . +/-                           | Edge Type 1 rising                          |                         |

|                                     | Periodicity 1                               |                         |

|                                     | Threshold Value 2 1.5                       |                         |

|                                     | i si paga paga paga paga paga paga paga pag |                         |

|                                     |                                             |                         |

|                                     | <<< OK 0                                    | ancel Apply Defaults    |

|                                     |                                             |                         |

| <u></u>                             |                                             | Cadence                 |

|                                     |                                             | <b>ICAUCHICE</b>        |

Figure 17: Delay calculation for Rectangle Pulse circuit

#### **5.3 Simulation Result and Discussion**

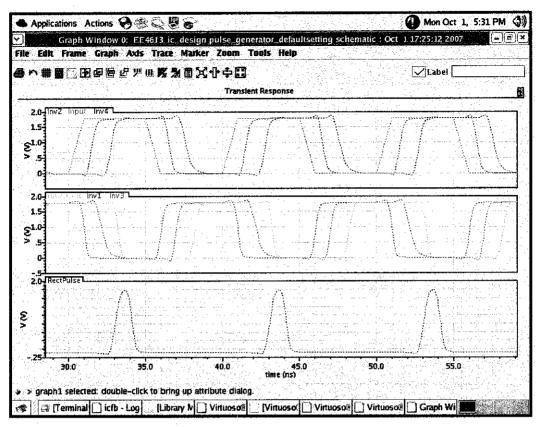

The input of the circuit is set to 100MHz pulse repetition frequency (PRF). The result obtained is approximately same as the theoretical Gaussian pulse. Figure 19 shows the timing diagram and rectangle pulse result. The waveform is obtained from the point represented by the alphabets (Table1), which is showed by Figure 12. To obtain the rectangle pulse, NAND operation is applied to the point C output and point F output as shown in Figure 18. This is the crucial stage where the delay operation time for each inverters and the N-voltage control need to determine first. NAND logic sequence required either one of the inputs to be 0 to obtain positive rectangle pulse. Figure 20 shows the rectangle pulse simulation generated pulse with 500MHz passed frequency.

| Waveform name          | Representation |

|------------------------|----------------|

| Input                  | Α              |

| Inverter 1             | B              |

| Inverter 2             | С              |

| Inverter3              | D              |

| Inverter 4             | E              |

| NAND Output            | F              |

| Rectangle Pulse Output | G              |

| Pulse Output           |                |

Table 1: The substitution of waveform labeling

Figure 18: NAND operation applied to obtain the rectangle pulse

Figure 19: Timing diagram of the pulse generator

Figure 20: Rectangle pulse output result achieved 500MHz pass frequency

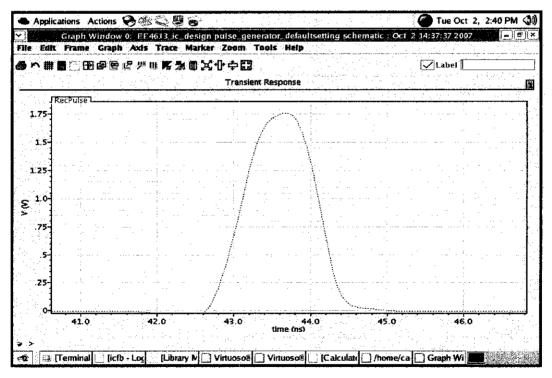

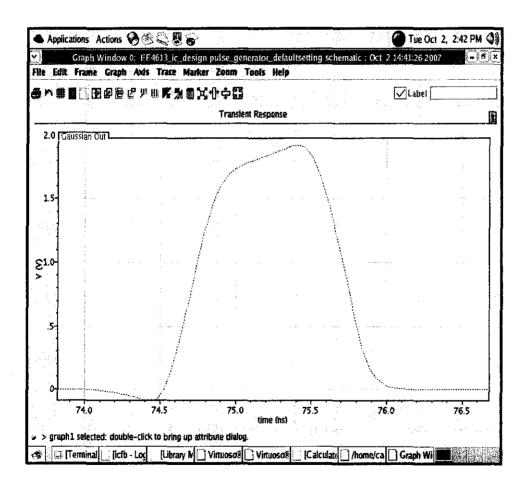

Figure 21 is the evidence for the output result, Gaussian pulse alike. It is better to have different time constants in this  $(RC)^n$  filter. The time constants can be increased by decreasing the (W/L) ratios of the transistors. Table 2 shows the aspect ratio transistor value for the design. By decreasing the width of the transistor will be increasing time constant. Furthermore, the gate and diffusion capacitances also decrease resulting in less load capacitances. In the CR-RC circuit described, there is a noticeable undershoot as the pulse attempts to return to the baseline. By using the pole-zero cancellation the peak shape can be improve and eliminates the overshoot. The result is an output pulse exhibiting a simple exponential decay to baseline with the desired differentiator time constant [9]. This circuit uses a zero to cancel a pole in the mathematical representation by complex variables [21]. M7 and M10 act to provide this adjustable resistance through bias control.

Figure 21: The pulse generator output result achieved 660MHz pass frequency

| AMI 0.6um Aspect Ratio Transistor Technology |           |            |  |  |  |

|----------------------------------------------|-----------|------------|--|--|--|

| Fransistor                                   | Width(um) | Length(nm) |  |  |  |

| M1                                           | 2.4       | 600        |  |  |  |

| M2                                           | 1.5       | 600        |  |  |  |

| M3                                           | 2.4       | 600        |  |  |  |

| M4                                           | 1.5 600   |            |  |  |  |

| M5                                           | 2.4       | 600        |  |  |  |

| M6                                           | 1.5       | 600        |  |  |  |

| M7                                           | 1.5       | 600        |  |  |  |

| M8                                           | 2.4       | 600        |  |  |  |

| M9                                           | 1.5       | 600        |  |  |  |

| M10                                          | 1.5       | 600        |  |  |  |

| M11                                          | 2.4       | 600        |  |  |  |

| M12                                          | 1.5       | 600        |  |  |  |

| M13                                          | 2.4       | 600        |  |  |  |

| M14                                          | 2.4       | 600        |  |  |  |

| M15                                          | 1.5       | 600        |  |  |  |

| M16                                          | 1.5       | 600        |  |  |  |

| M17                                          | 2.0       | 600        |  |  |  |

| M18                                          | 1.2       | 600        |  |  |  |

| M19                                          | 1.9       | 600        |  |  |  |

| M20                                          | 1.5       | 600        |  |  |  |

| M21                                          | 2.4       | 600        |  |  |  |

| M22                                          | 0.9       | 600        |  |  |  |

| M23                                          | 1.8       | 600        |  |  |  |

| M24                                          | 1.5       | 600        |  |  |  |

# Table 2: Aspect ratio value of the PMOS and NMOS transistors

~

Figure 22: Rectangle pulse generator circuit diagram

Figure 23: Quasi Gaussian filter circuit diagram

# CHAPTER 6 CONCLUSION AND RECOMMENDATIONS

#### **6.1** Conclusion

Throughout the project, the author has become aware of the challenges and complexity in designing integrated circuit for high frequency application. The whole project itself is a new learning process for the author. In particular, the following objectives set in the beginning have been achieved.

- i. To design pulse generator at least 500MHz and that can transmit data in high frequency.

- ii. To use CMOS logic style in the design. From the simulation, it is verified that the chosen logic style can be used for high frequency application.

- iii. To use Spectre cadence software in the circuit simulation. In this project, Spectre has been used extensively, from the modeling until simulation process.

Working on this project has been a constant challenge since the beginning. However, the experience gained and the insight learned is more than what is attained in classroom. Therefore, it is hope that the new found knowledge can be used to design other challenging circuits.

#### **6.2 Recommendations**

For two semesters, many things have been learned for completing the project. Even though the project has reached the objectives, there are some improvements to be made for better result. Some of the recommendations are specifically include;

#### 6.2.1 Design with Different Topology

From the references that have been used, there are various pulse generator circuit design with different approach. One interesting approach of designing the pulse generator is using the H-bridge circuit and off chip filter as reported by [20]. The features of H-bridge, which provide balanced positive and negative currents, are suitable for generating the antipodal UWB pulse. The circuit design is also implementing below 1GHz UWB system. Interesting study of various pulse comparisons includes power consumptions and antenna effect consideration in the design.

#### **6.2.2 Design Applications Improvement**

In this design, the author makes assumption of high frequency input for generating the pulse. The scope of the project required to generate the pulse generator. Thus, for the next improvement the author suggests to implement the pulse generator in the application design such as reported by [7, 2]. The applications of UWB are very interesting to explore and implementing it to the daily life such as WPAN and RFID technology. The world nowadays urged wireless connection and reduced the wired connection. The assumption is made due to the complexity of the modulation circuit design (creating the high frequency pulse from the low frequency)

#### REFERENCES

- [1] http://www.icknowledge.com/history/1960s.html [6 Dec 2007]

- [2] A. A. Abidi, "RF CMOS Comes of Age," Digest of Technical Papers, Symposium on VLSI Circuits, 2003, pp. 113-116, 12-14 June 2003

- [3] G. F. Ross, Transmission and Reception System for Generating and Receiving Base-band Duration Pulse Signals Without Distortion for Short Baseband Pulse Communication System, United States Patent, No. 3,728,632, April 1973.

- [4] K. Marsdan, H.J. Lee, D. S. Ha "Low power CMOS re-programmable Pulse Generator for UWB Systems" Int. Conf. on Ultra Wideband System and Technologies pp. 443, November 2003, Reston, Virginia.

- [5] J. Reed "Introduction to Ultra Wideband Communication System" Prentice Hall, April 2005.

- [6] Dr. J. Barret "Truly Balanced Step Recovery Diode Pulse Generator with Single Power Supply" Cork Institute of Technology, Ireland.

- [7] K. M. Marsden "A Study of a versatile Low Power CMOS Pulse Generator for Ultra Wideband Radios" Virginia Polytechnic Institute and State University, IEEE Thesis, December 2003

- [8] D.F. Filipovic "A Planar Broadband Balanced Doubler Using a Novel Balun Design" IEEE Microwave and Guided Letters. Vol.4 No 7, July 1994.

- [9] X. Zhang, S. Ghosh and M. Bayoumi, "A Low Power CMOS UWB Pulse Generator", The center for advance computer studies, University of Louisiana at Lafayatte, IEEE 2005

- [10] A. Sedra and K Smith, Microelectronic Circuit, 5<sup>th</sup> Edition, New York: Oxford 2003

- [11] A. P. Dancy and A. Chandrakasan "Ultra Low Power Control Circuit for PWM Converter" Massachusetts Institute of Technology, Cambridge, IEEE Press

- [12] <u>http://thalia.spec.gmu.edu/~pparis/classes/coll\_460\_4/node4.html</u> [6 Dec 2007]

- [13] N. R. Mahapatra, A. Tareen and S. V. Garimella "Comparison and Analysis of Delay Elements" University at Buffalo, IEEE Transaction

- [14] S. Krishnamohan, N. R. Mahapatra "An analysis of the Robustness of CMOS Delay Element" Department of Electrical and Computer Engineering Michigan State University, IEEE Transaction

- [15] E. Fairstein, "Linear Unipolar Pulse-Shaping Networks: Current Technology", IEEE Transaction on Nuclear Science, Vol, 37, No. 2, April 1990.

- [16] H. Kim and Y.Joo, "All-Digital Low-Power CMOS Pulse Generator," IEEE Electronics Letters Vol. 40, No 24, pp. 1534–1535, November 2004

- [17] Dr. J. Barret, "Truly Balance Step Recovery Diode Pulse Generator with Single Power Supply" Cork Institute of Technology, Ireland Adaptive wireless Systems Group

- [18] <u>www.fcc.gov</u> [6 Dec 2007]

- [19] J.M. Rabaey, "Digital integrated circuits: A design perspective," *Prentice-Hall Book Company*, 1st edition, ISBN #0-13-178609-1, Upper Saddle River, NJ, 1996.

- [20] <u>http://bwrc.eecs.berkeley.edu/Publications/2005/THESES/S.%20Wang/S.%20</u> <u>BoTing%20Wang%20Thesis.pdf Stanley Bo-Ting Wang, "Design of Ultra-</u> <u>Wideband RF Front-End"</u> [6 Dec 2007]

- [21] <u>http://www.ortec-online.com/electronics/amp/03\_4.htm</u> [6 Dec 2007]

# APPENDICES

#### Appendix A: PMOS transistor process parameter

```

B1=5E-6 & KETA=-5.769328E-3 &

A1=0 &

A2=1 &

RDSW=2.746814E3 & PRWG=2.34865E-3 &

PRWB=0.0172298 &

WR=1 &

WINT=2.586255E-7 &

LINT=7.205014E-8 &

XL=0 &

Øv=0 &

DWB=9.857534E-9 &

VOFF=-0.0837499 &

NFACTOR=1.2415529 &

CIT=0 &

CDSC=4.363744E-4 &

CDSCD=0 &

CDSCB=0 &

ETA0=0.11276 &

ETAB=-2.9484E-3 &

DSUB=0.3389402 &

POLM-4.9847806 &

PDIBLC1=2.481735E-5 &

PDIBLC2=0.01 &

PDIBLCB=0 &

DROUT=0.9975107 &

PSCBE1=3.497872E9 &

PSCBE2=4.974352E-9 &

-- amiOGP.m (ObjC Abbrev)--L44--38%------

Write file: /tmp/fr-BUB1C1/ncsu-cdk-1.5.1/models/spectre/nom/

```

PVAG=10.9914549 & DELTA=0.01 & MOBMOD=1 & PRT=0 & UTE=-1.5 & KT1=-0.11 & KT1L=0 & KT1L=0 & KT2=0.022 & UA1=4.31E-9 & UB1=-7.61E-18 & UC1=-5.6E-11 & AT=3.3E4 & ₩L=0 & WLN=1 & ₩**₩**≠0 & WWM=1 & **⊡**#1.=0 & LL=0 & LLN=1 & LW=0 & LWN=1 & LVL=0 & CAPMOD=2 & MPART=0.4 & CGD0=2.4E-10 & CGS0=2.4E-10 & CGSO=2.4E-1U & CGBO=0 & CJ=7.273568E-4 & PE=0.9665597 & MJ=0.4959837 & CJSV=3.114708E-10 & PESV=0.99 & -- ami06P.m (ObjC Abbrev)--L79--69%------Write file: /tmp/fr-BU81C1/ncsu-cdk-1.5.1/models/spectre/nom/]

WIL=0 & L=0 & LLN=1 & LV=8 & LWN=1 & LVL=0 & CAPMOD=2 & KPART=0.4 & CGD0≈2.4E-10 & CGS0=2.4E-10 & CGB0=**0** & CJ=7.273568E-4 & PB=0.9665597 & MJ=0.4959837 & CJSW=3.114708E-10 & PESW=0.99 & MJSW=0.2653654 & PVTH0=9.420541E-3 & PRDSW=-231.2571566 & PK2=1.396684E-3 & WKETA=1. 862966E-3 & LKETA=5. 728589E-3 ) Π

-- ami06P.m (0bjC Abbrev)--L101--Bot------Write file: /tmp/fr-BU81C1/ncsu-cdk-1.5.1/models/spectre/nom/

#### Appendix B: NMOS transistor process parameter

MNGEN SPICE BSIM3 VERSION 3.1 (HSPICE Level 49) PARAMETERS

\* Level 11 for Cadence Spectre

\* DATE: Jan 25/99

\* LOT: nBbn VAF: 03

\* Temperature\_parameters=Default

MODEL amioGN NMOS ( LEVEL=11 &

VERSION=3.1 &

TROM=27 &

TOX=1.41E-8 &

XJ=1.5E-7 &

NCH=1.7E17 &

VTH0=0.7086 &

K1=0.9354582 &

K2=-0.080431 &

K3=41.4403818 &

K3=41.4403818 &

K3=-14 &

VTH0=0.8

DVT1W=5.3E6 &

DVT1W=5.3E6 &

DVT2W=-0.032 &

DVT1W=5.3E6 &

DVT2W=-0.1399976 &

UD=2.50236=10 &

UD=1.181167E-18 &

UD=2.582756E-11 &

VSAT=1.300981E5 &

A0=0.5292985 &

A0=0.5292985 &

A0=0.0173166 &

A1=0 &

K1=0.0173166 &

A1=0 &

K1=0.0173166 &

A1=0 &

K1=0 &

K1=0.0173166 &

A1=0 &

K1=0.0173166 &

A1=0.017000

K1=0.017000

K1=0.01700

K1=0.017000

K1=0.017000

K1=0.01700

K1=0.01700

K1=0.017000

K1=0.01700

K1=0.01700

K1=0.

KETA=-0.0173166 & A1=0 & A2=1 & RDSW=2.268366E3 & PRWG=-1E-3 & PRWB-6. 320549E-5 & MR=1 & WINT=2.043512E-7 & LINT=3.034496E-8 & XL=0 & XW=0 & AV=0 & DWG=-1.446149E-8 & DWB=2.077539E-8 & V0FF=-0.1137226 & NFACTOR=1.2880596 & CIT=0 & CDSC=1.506004E-4 & CDSCD=0 & CDSCB=0 & CDSCB=0 & ETAU=3.815372E-4 & ETAB=-1.029178E-3 & DSUB=2.173055E-4 & PCLM=0.6171774 & PDIBLC1=0.185986 & PDIBLC2=3.473187E-3 & PDIBLCB=-1E-3 & DROUT=0.4037723 & PSCBE1=5.998012E9 & PSCBE1=5.998012E9 & PSCBE2=3.788068E-8 & PVAG=0.012927 & DELTA=0.01 & DELTA=0.01 & MOBMOD=1 & PET=0 & UTE =-1.5 & KT1=-0.11 & KT2≖U. U22 & UA1=4.31E-9 & UB1=-7.61E-18 & UC1=-5.6E-11 & AT=3.3E4 & ₩L=0 & MLN=1 & WW=0 & WWN=1 & WWL=0 & LL=0 & LLN=1 & L₩=**0 &** 上朝新=1 & LWL=0 & CAPMOD=2 & XPART=0.4 & CGB0=1.99E-10 & CGS0=1.99E-10 & CGB0=0 & CJ=4.233802E-4 & PB=0.9899238 & MJ=0.4495859 & CJSW=3.825632E-10 & PBSW=0.1082556 & MJSW=0.1083618 & PVTH0=0.0212852 & PRDSW=-16.1546703 & PK2=0.0253069 & WKETA=0.0188633 & LKETA=0.0204965 )