# PERFORMANCE COMPARISON REVIEW OF

# 8-3 COMPRESSOR ON FPGA

LEONG YUHAO

# ELECTRICAL AND ELECTRONICS ENGINEERING

# UNIVERSITI TEKNOLOGI PETRONAS

JANUARY 2017

## Performance Comparison Review of 8-3 Compressor on FPGA

by

Leong Yuhao

17919

Dissertation submitted in partial fulfilment of

the requirements for the

Bachelor of Engineering (Hons)

(Electrical and Electronics)

JANUARY 2017

Universiti Teknologi PETRONAS

Bandar Seri Iskandar

31750 Tronoh

Perak Darul Ridzuan

#### CERTIFICATION OF APPROVAL

# PERFORMANCE COMPARISON REVIEW OF 8-3 COMPRESSOR ON FIELD-PROGRAMMABLE GATE ARRAY (FPGA)

by

Leong Yuhao

17919

A project dissertation submitted to the

**Electrical and Electronics Engineering Programme**

Universiti Teknologi PETRONAS

in partial fulfilment of the requirement for the

BACHELOR OF ENGINEERING (Hons)

(ELECTRICAL AND ELECTRONICS)

Approved by,

(Lo Hai Hiung)

#### UNIVERSITI TEKNOLOGI PETRONAS

TRONOH, PERAK

January 2017

#### CERTIFICATION OF ORIGINALITY

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

LEONG YUHAO

## ABSTRACT

Compressors are commonly utilized in multipliers to cut down partial products in a parallel manner. Its main usage in this project is to go beyond the limit of fabrication technology to improve the computer performance. 2:1 compressors (half adder), 3:2 compressors (full adder), and 4:2 compressors should be well understood as it is the fundamental for building higher order compressors. In this paper, a 7-3, 8-3, 8-4, 9-3, and 9-4 researched compressors design either consisted of adder circuits or multiplexer circuits will be discussed and compared in terms of number of logic gates used, cell area and power delay product (PDP) in order to find the best method to implement the 8-3 compressor design.

#### ACKNOWLEDGEMENT

I am utilizing this utmost occasion to speak out my appreciation to all who has given me the comprehensive and continuous guidance throughout my Final Year Project period at Universiti Teknologi PETRONAS. This has given me a very praiseworthy moment which is hard to be found from anywhere else. I am grateful for their aspiring guidance, valuable constructive criticisms and kind advices during my project-doing period. The great experiences and skills shared by them give me a very new knowledge either from the aspect of organization or from the aspect of industrial world. To add-on, the practical project is beneficial for me in order to have better understandings on my role in Intel Penang.

A special thanks to my Final Year Project supervisor, Mr. Lo Hai Hiung for providing me a chance to be part of his project under his supervision. He gave me an interesting project titled "Performance Comparison Review of 8-3 Compressor on Filed-Programmable Gate Array (FPGA)" which covered working principles of compressor with the aids of Altera Quartus II Web Edition and Altera-ModelSim using Verilog Hardware Description Language and I feel honoured to be given this golden chance to learn new things. His willingness to share his experiences and prompt responses to my inquiries has tremendously given me a huge contribution in order for me to complete my final year project successfully.

Last but not least, an endeavour over a period is hard to be successful without the constructive advices, commitments, and supports from all my beloved friends, family, and my kind and helpful colleagues. Without their positive attitudes, moral supports, and friendly helps, I may not be able to complete my 8-months final year project to be such successful. Thanks for all the help! Be it little or huge, it definitely helped me a lot and I could not have done much without your cooperation!

# **TABLE OF CONTENTS**

| CERTIFICATE OF APPROVAL                      | II  |

|----------------------------------------------|-----|

| CERTIFICATE OF ORIGINALITY                   | III |

| ABSTRACT                                     | IV  |

| ACKNOWLEDGE                                  | V   |

| LIST OF ABBREVIATION                         | X   |

| CHAPTER 1: INTRODUCTION                      | 1   |

| 1.1 BACKGROUND                               | 1   |

| 1.2 PROBLEM STATEMENT                        |     |

| 1.3 OBJECTIVES                               |     |

| 1.4 SCOPES OF STUDY                          | 3   |

| CHAPTER 2: LITERATURE REVIEW                 | 4   |

| 2.1 LITERATURE REVIEWS                       | 4   |

| 2.2 9-4 COMPRESSORS                          | 5   |

| 2.3 8-4 COMPRESSORS                          | 6   |

| 2.4 7-3 COMPRESSORS                          | 8   |

| 2.5 8-3 COMPRESSORS                          | 8   |

| 2.6 7-2 COMPRESSORS                          | 10  |

| CHAPTER 3: METHODOLOGY                       | 12  |

| 3.1 RESEARCH METHODOLOGY                     |     |

| 3.2 RESEARCH ACTIVITIES                      |     |

| CHAPTER 4: RESULTS AND DISCUSSIONS           | 10  |

| 4.1 8-3 COMPRESSOR (FULL AND HALF ADDERS)    |     |

| 4.1 8-3 COMPRESSOR (FULL AND HALF ADDERS)    |     |

| 4.3 9-4 COMPRESSOR (FULL AND HALF ADDERS)    |     |

| 4.4 9-3 COMPRESSOR (FULL AND HALF ADDERS)    |     |

| 4.5 7-3 COMPRESSOR (FULL AND HALF ADDERS)    |     |

| 4.6 7-3 COMPRESSOR (MUX AND XOR LOGIC GATES) |     |

| 4.7 8-4 COMPRESSOR (MUX AND HALF ADDERS)     |     |

| 4.8 9-4 COMPRESSOR (MUX AND HALF ADDERS)     |     |

| 4.9 DISCUSSIONS                              |     |

| CHAPTER 5: CONCLUSION AND RECOMMENDATION     | 60  |

| 5.1 CONCLUSION                               |     |

| 5.2 RECOMMENDATIONS                          |     |

|                                              |     |

| REFERENCES                                   |     |

| APPENDIX                                     | 63  |

# **LIST OF FIGURES**

| Figure 1: Pictures showing Partial Product Generation and Final Product Computation |    |

|-------------------------------------------------------------------------------------|----|

| Figure 2: Implementation of 9-4 Compressor using Half and Full Adders [1]           | 6  |

| Figure 3: Implementation of 8-4 Compressor using Multiplexer [1]                    | 7  |

| Figure 4: The Overall Proposed Structure of m:3 Compressor [3]                      | 9  |

| Figure 5: 8:3 New Hybrid Wide Compressor [15]                                       | 9  |

| Figure 6: The Overall Proposed Structure of 7:2 Compressor [14]                     | 11 |

| Figure 7: Research Methodology Used in Project                                      |    |

| Figure 8: Research Activities Used in Project                                       |    |

| Figure 9: Minimum 8-3 Compressor Propagation Delay [12]                             |    |

| Figure 10: 8-3 Compressor Propagation Delay [12]                                    |    |

| Figure 11: RTL View of 8-3 Compressor Model [12]                                    |    |

| Figure 12: RTL View in Relationship with Input iSW[7] and Output oLEDG[1] [12]      |    |

| Figure 13: 8-3 Compressor Functional Simulation using ModelSim-Altera               |    |

| Figure 14: Error Result of 8-3 Compressor Functional Test bench on Console          |    |

| Figure 15: Overall 8-3 Compressor Model Timing Simulation                           |    |

| Figure 16: Timing Simulation for iSW[07] with bit 1s and output oLEDG[02]           |    |

| Figure 17: Minimum 8-4 Compressor Model Propagation Delay [1]                       |    |

| Figure 18: 8-4 Compressor Model Maximum Propagation Delay [1]                       |    |

| Figure 19: Overall RTL View of 8-4 Compressor Model [1]                             |    |

| Figure 20: RTL View in Relationship with Input iSW[0] and Output oLEDG[3] [1]       |    |

| Figure 21: 8-4 Compressor Functional Simulation using ModelSim-Altera               |    |

| Figure 22: Error Result of 8-4 Compressor Functional Test bench on Console          |    |

| Figure 23: Overall 8-4 Compressor Model Timing Simulation                           |    |

| Figure 24: Timing Simulation for Inputs iSW[07] with bit 1 and output oLEDG[03]     |    |

| Figure 25: Minimum 9-4 Compressor Model Propagation Delay [1]                       |    |

| Figure 26: 9-4 Compressor Model Maximum Propagation Delay [1]                       |    |

| Figure 27: Overall RTL View of 9-4 Compressor Model [1]                             |    |

| Figure 28: RTL View in Relationship with Input iSW[7] and Output oLEDG[3] [1]       |    |

| Figure 29: 9-4 Compressor Functional Simulation using ModelSim-Altera               |    |

| Figure 30: Error Result of 9-4 Compressor Functional Test bench on Console          |    |

| Figure 31: Overall 9-4 Compressor Model Timing Simulation                           |    |

| Figure 32: Timing Simulation for Inputs iSW[08] with bit 1s and output oLEDG[03]    |    |

| Figure 33: Minimum 9-3 Compressor Model Propagation Delay [12]                      |    |

| Figure 34: 9-3 Compressor Model Maximum Propagation Delay [12]                      |    |

| Figure 35: Overall RTL View of 9-3 Compressor Model [12]                            |    |

| Figure 36: RTL View in Relationship with Input iSW[7] and Output oLEDG[1] [12]      |    |

| Figure 37: 9-3 Compressor Functional Simulation using ModelSim-Altera               |    |

| Figure 38: Error Result of 9-3 Compressor Functional Test bench on Console          |    |

| Figure 39: Overall 9-3 Compressor Model Timing Simulation                           |    |

| Figure 40: Timing Simulation for Inputs iSW[08] with bit 1s and output oLEDG[03]    |    |

|                                                                                     |    |

| Figure 41: Minimum 7-3 Compressor Model Minimum Propagation Delay [10]              |    |

| Figure 42: 7-3 Compressor Model Maximum Propagation Delay [10]                      |    |

| Figure 43: Overall RTL View of 7-3 Compressor Model [10]                            |    |

| Figure 44: RTL View in Relationship with Input iSW[5] and Output oLEDG[1] [10]      |    |

| Figure 45: 7-3 Compressor Functional Simulation using ModelSim-Altera               |    |

| Figure 46: Error Result of 7-3 Compressor Functional Test bench on Console          | 38 |

| Figure 47: Overall 7-3 Compressor Model Timing Simulation                                           | . 39 |

|-----------------------------------------------------------------------------------------------------|------|

| Figure 48: Timing Simulation for Inputs iSW[5] with bit 1 and output oLEDG[1] with bit              |      |

| Figure 49: Minimum 7-3 Compressor Model Minimum Propagation Delay using MUX an XOR Logic Gates [10] | nd   |

| Figure 50: 7-3 Compressor Model Maximum Propagation Delay using MUX and XOR<br>Logic Gates [10]     |      |

| Figure 51: Overall RTL View of MUX-XOR Logic Gates 7-3 Compressor Model [10]                        |      |

| Figure 52: RTL View in Relationship with Input iSW[5] and Output oLEDG[1] [10]                      |      |

| Figure 53: 7-3 Compressor Functional Simulation using ModelSim-Altera                               |      |

| Figure 54: Error Result of 7-3 Compressor Functional Test bench on Console                          |      |

| Figure 55: Overall 7-3 MUX-XOR Compressor Model Timing Simulation                                   |      |

| Figure 56: Timing Simulation for Inputs iSW[5] with bit 1 and output oLEDG[1] with bit              |      |

| Figure 57: Minimum 8-4 Compressor Model Minimum Propagation Delay using MUX an Half Adders [1]      | nd   |

| Figure 58: 8-4 Compressor Model Maximum Propagation Delay using MUX and Half<br>Adders [1]          | . 45 |

| Figure 59: Overall RTL View of MUX and Half Adders' 8-4 Compressor Model [1]                        |      |

| Figure 60: RTL View in Relationship with Input iSW[2] and Output oLEDG[3] [1]                       | . 46 |

| Figure 61: 8-4 Compressor Functional Simulation using ModelSim-Altera                               | . 47 |

| Figure 62: Error Result of 8-4 Compressor Functional Test bench                                     | . 47 |

| Figure 63: Overall 8-4 MUX-Half Adder Compressor Model Timing Simulation                            | . 48 |

| Figure 64: Timing Simulation for Inputs iSW[2] with bit 1 and output oLEDG[3] with bit              |      |

| Figure 65: Minimum 9-4 Compressor Model Minimum Propagation Delay using MUX an                      |      |

| Half Adder [1]                                                                                      |      |

| Figure 66: 9-4 Compressor Model Maximum Propagation Delay using MUX and Half Ad                     | der  |

| [1]                                                                                                 |      |

| Figure 67: Overall RTL View of MUX-Half Adder 9-4 Compressor Model [1]                              |      |

| Figure 68: RTL View in Relationship with Input iSW[5] and Output oLEDG[3] [1]                       |      |

| Figure 69: 9-4 Compressor Functional Simulation using ModelSim-Altera                               | . 52 |

| Figure 70: Error Result of 9-4 Compressor Functional Test bench                                     |      |

| Figure 71: Overall 9-4 MUX-Half Adder Compressor Model Timing Simulation                            |      |

| Figure 72: Timing Simulation for Inputs iSW[5] with bit 1 and output oLEDG[3] with bit              |      |

| Figure 73: Figure showing Simplified Concept of using 8-3 Compressor                                | . 54 |

| Figure 74: 8-3 Compressor Model / Finite State Machine                                              | . 63 |

| Figure 75: 8-3 Compressor Functional Test bench                                                     | . 63 |

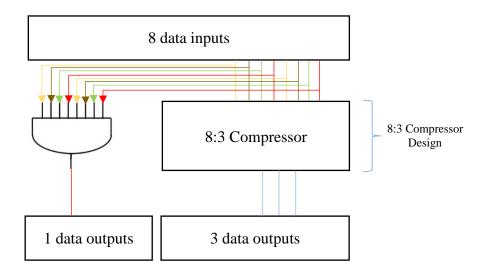

| Figure 76: 8-4 Compressor Model / Finite State Machine                                              |      |

| Figure 77: 8-4 Compressor Functional Test bench                                                     | . 64 |

| Figure 78: 9-4 Compressor Model / Finite State Machine                                              |      |

| Figure 79: 9-4 Compressor Functional Test bench                                                     |      |

| Figure 80: 9-3 Compressor Model / Finite State Machine                                              |      |

| Figure 81: 9-3 Compressor Functional Test bench                                                     | . 66 |

| Figure 82: 7-3 Compressor Model / Finite-State Machine                                              |      |

| Figure 83: 7-3 Compressor Functional Test bench                                                     |      |

| Figure 84: 7-3 Compressor Model / Finite-State Machine using MUX-XOR Logic Gates                    |      |

| Figure 85: MUX-XOR Logic Gates 7-3 Compressor Functional Test bench              | . 68 |

|----------------------------------------------------------------------------------|------|

| Figure 86: 8-4 Compressor Model / Finite-State Machine using MUX and Half Adders | . 69 |

| Figure 87: MUX and Half Adders 8-4 Compressor Functional Test bench              | . 69 |

| Figure 88: 9-4 Compressor Model / Finite-State Machine using MUX and Half Adders | . 70 |

| Figure 89: MUX and Half Adders 9-4 Compressor Functional Test bench              | . 70 |

|                                                                                  |      |

# **LIST OF TABLES**

| Table 1: Performance Comparison of 8-4 Compressor and 9-4 Compressor [1]              | 6 |

|---------------------------------------------------------------------------------------|---|

| Table 2: Performance Comparison of 8-4 Compressor [1]                                 | 7 |

| Table 3: Implementation Results with Final Ripple Adder [3]10                         | 0 |

| Table 4: Evaluation of Proposed 7:2 Compressor with respect to Conventional 7:2       |   |

| Compressor [14]12                                                                     |   |

| Table 5: Gantt chart for Final Year Project I 1                                       | 7 |

| Table 6: Gantt chart for Final Year Project II                                        | 8 |

| Table 7: Propagation Delay of input iSW[07] with Input 1s 22                          | 2 |

| Table 8: Propagation Delay of iSW[07] with Input 1s 20                                | 6 |

| Table 9: Propagation Delay of iSW[08] with Input 1s                                   | 1 |

| Table 10: Propagation Delay of iSW[08] with Input 1s                                  | 5 |

| Table 11: Propagation Delay of iSW[5] and oLEDG[1] with Input 1s                      | 9 |

| Table 12: Propagation Delay of iSW[5] and oLEDG[1] with Input 1s 43                   | 3 |

| Table 13: Propagation Delay of iSW[2] and oLEDG[3] with Input 1s 48                   | 8 |

| Table 14: Propagation Delay of iSW[5] and oLEDG[3] with Input 1s                      | 3 |

| Table 15: Summary of Overall Compressor Types in Relationship with Logic Gate Numbers |   |

| and Critical Path Propagation Delay                                                   | 5 |

| Table 16: Summary of Overall Compressor Types in Relationship with Cell Area, Power   |   |

| Consumption and Power Delay Product (PDP)                                             | 5 |

| Table 17: Total Number of Logic Gates Used and Critical Path Propagation Delay        |   |

| Comparisons between 7-3 Compressors                                                   |   |

| Table 18: Cell Area, Power Consumption and Power Delay Product Comparisons between 7  |   |

| 3 Compressors                                                                         | 6 |

| Table 19: Total Number of Logic Gates Used and Critical Path Propagation Delay        |   |

| Comparisons between 8-4 Compressors                                                   |   |

| Table 20: Cell Area, Power Consumption and Power Delay Product Comparisons between 8  |   |

| 4 Compressors                                                                         | 7 |

| Table 21: Total Number of Logic Gates Used and Critical Path Propagation Delay        |   |

| Comparisons between 9-4 Compressors                                                   |   |

| Table 22: Cell Area, Power Consumption and Power Delay Product Comparisons between 9  |   |

| 4 Compressors                                                                         | 8 |

# LIST OF ABBREVIATION

- 16-T : 16 Transistor

- EDP : Energy Delay Product

- PDP : Power Delay Product

- VLSI : Very Large Scale Integration

- CPU : Central Processing Unit

- FPGA : Field-Programmable Gate Array

- RTL : Register Transfer Language

- HDL : Hardware Description Language

- CMOS : Complementary Metal Oxide Semiconductor

## **CHAPTER 1: INTRODUCTION**

#### **1.1 BACKGROUND**

Multiplication can be considered as a complicated and time-consuming arithmetic operation and it is the key operation in most of the signal processing algorithm [1] [2] [3] [4]. Designing good multipliers is challenging for Very Large Scale Integration (VLSI) as they normally have long latency, large area, and consuming significant power [1] [5]. A good multiplier must be physically compact, consuming low power, and having a good speed [1]. Generally, the process of multiplication can be split into three stages: generating partial product stage, reducing partial product stage, and computing final product stage [2] [3] [6]. The partial product generation and final product computation concept is shown in Figure 1. In VLSI circuit, the stage of reducing partial product will greatly reduce multiplier performance from the aspect of dissipating power and speed [5] [7] [8] [9]. A long critical vertical path during addition causes partial product reduction to have high latencies [10] [11]. Adders that are generally used to shorten the vertical critical path will cause issues such as uneven signal transitions and glitches and more number of adder stages are required to reduce the partial product [1] [8] [12]. To handle these issues, compressors are required to be utilized in multiplier design as it provides a regular structure in the stage of reducing partial product [5].

| 1010    | $\rightarrow$ | Multiplicand      |

|---------|---------------|-------------------|

| × 1011  | $\rightarrow$ | Multiplier        |

| 1010    | $\rightarrow$ | Partial product 1 |

| 1010    | $\rightarrow$ | Partial product 2 |

| 0000    | $\rightarrow$ | Partial product 3 |

| 1010    | $\rightarrow$ | Partial product 4 |

| 1101110 |               |                   |

Figure 1: Partial Product Generation and Final Product Computation

#### **1.2 PROBLEM STATEMENT**

Computer system performance has flattened out as fabrication technology is reaching its physical limit. Thus, reviewing the circuit design is needed to search for possible speed up from smarter circuit design to give a faster computer for future demand. Typically, compressors are used in high speed addition and multiplication unit design in microprocessor. Thus, a faster compressor would allow for a faster addition and multiplication for future computer architecture systems design.

#### **1.3 OBJECTIVES**

The objectives of the project are:

- To repeat 7-3, 7-4, 8-3, 8-4, 9-3, and 9-4 compressor designs of others

- To verify researched compressor designs performance report

- To determine the best method of designing 8-3 compressor

#### **<u>1.4 SCOPES OF STUDY</u>**

This study was conducted by Leong Yuhao at Universiti Teknologi PETRONAS and it is vital as compressors consisted of adders and multiplexers and these are the fundamental for Central Processing Unit (CPU) to process data.

Besides that, this study also focuses on reading and understanding several research papers related to high order compressors such as 7-3, 7-4, 8-3, 8-4, 9-3, and 9-4 compressor designs. Then, the best way of designing the 8-3 compressor will be well-analysed by listing out the advantages and disadvantages of the compressors from the aspect of power consumption, propagation delay, and cell area and the best method of designing 8-3 compressor either using adders' method, combination of multiplexers and XOR logic gates, or combination of multiplexer and adders will be decided.

This project is relevant to Electrical and Electronics Engineering Programme as it allows me to write Verilog HDL and read signal transition diagrams for a better understanding of logic gates. Moreover, this project is feasible as it can be done with the aids of FPGA and Altera software for functional and timing simulation purposes.

#### **CHAPTER 2: LITERATURE REVIEW**

#### **2.1 LITERATURE REVIEWS**

Field-Programmable Gate Array (FPGA) is an integrated circuit containing programmable logic blocks arrays designed to be easily configured to logic gates to perform complex combinational functions, or merely simple logic gates like AND or XOR [13].

During partial product stage, multipliers need large amount of delay and power [10] [14]. At this stage, compressors will come into play where its usage is to reduce the partial product reduction. A compressor is merely an adder circuit which is a combinatorial device mainly utilized in multipliers to cut down the operands while summing partial products terms [10] [11]. It generates some sum signals by adding a number of equally-weighted bits. It is generally known to be used with the goal of cutting down a large number of inputs to a smaller number of outputs by utilising accumulation method in a parallel manner [12] [14]. Its primary usage is to concurrently sum up the large number of partial products happening in multipliers [10] [12] [14]. Compressors usage not only limited to reducing the vertical critical path of circuit but also simultaneously decreasing the stage operations [3] [7] [8]. The compressor structure avoids carry propagation. For instance, in 4:2 compressors, the value of  $C_{out}$  depends only on input A, B, C, and D but independent of  $C_{in}$ . In general, a compressor will consist of 2 types of adders which are half adders and full adders [1] [2] [3] [5]. Half adders can be constructed easily with one AND and one Exclusive-OR (XOR) gate while full adders can be easily constructed using one OR, 2 AND, and 2 XOR gates [2]. The full adder's equation can be summarised as below:

$$Sum = (A \oplus B) \oplus Cin$$

[2]

$$Cout = AB + Cin(A \oplus B)$$

[2]

To have better understanding of higher order compressors, 4 types of compressors that are 8:4 compressors, 8:3 compressors, 7:3 compressors, and 7:2 compressors are being studied.

#### 2.2 9-4 COMPRESSORS

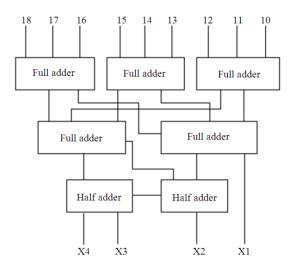

R.Marimuthu, et al. [1] proposed an 9-4 compressor using 5 Full Adders and 2 half adder as shown in Figure 2. Its implementation results are shown in Table 1 which it was compared with the 8-4 compressor. From the table, the power and EDP of 9-4 compressor is higher than 8-4 compressor. It shows that the higher order compressors consume more power, longer critical path propagation delay and larger compressor cell area. It shows that the vertical critical path of 9-4 compressors is longer than 8-4 compressors as 9-4 compressor involved more logic gates which are 2 AND gates and 1 XOR gate more than the 8-4 compressor. By increasing the number of logic gates in higher order compressors, the critical path propagation delay of the compressors is increased by 5.66% , contributing to higher power consumed and larger area of cell.

Figure 2: Implementation of 9-4 Compressor using Half and Full Adders

[1]

Table 1: Performance Comparison of 8-4 Compressor and 9-4 Compressor

[1]

|                             | 8-4 Compressor            | 9-4 Compressor            |

|-----------------------------|---------------------------|---------------------------|

| Parameters                  | Using full and half adder | Using full and half adder |

| Power (nW)                  | 18276-250                 | 21848.2180                |

| Delay (ps)                  | 1028.000                  | 1082.0000                 |

| Area (µm2)                  | 93.139                    | 102.1900                  |

| EDP 10 <sup>-24</sup> (J-s) | 19.310                    | 25.5779                   |

#### 2.3 8-4 COMPRESSORS

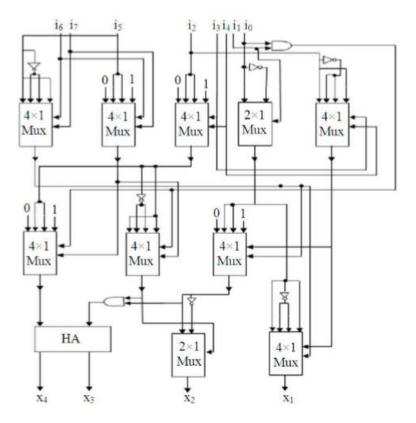

R.Marimuthu, et al. [1] proposed an 8-4 compressor using 10 multiplexers and 1 half adder as shown in Figure 3. Its implementation results are shown in Table 2 which it was compared with the conventional compressor. From the table, the power and EDP of 8-4 compressor using multiplexer is lower than the 8-4 compressor using adders. It shows that the compressors using multiplexers is more energy and power efficient. However, the critical path propagation delay and cell area of compressor using multiplexer is larger than compressor using half and full adder. It shows that the vertical critical path of compressors using multiplexer is 4.18% longer than compressors using half and full adder.

Figure 3: Implementation of 8-4 Compressor using Multiplexer [1]

Table 2: Performance Comparison of 8-4 Compressor [1]

|                             | 8-4 Compressor            |                   |  |

|-----------------------------|---------------------------|-------------------|--|

| Parameters                  | Using full and half adder | Using multiplexer |  |

| Power (nW)                  | 18276-250                 | 15263.603         |  |

| Delay (ps)                  | 1028.000                  | 1071.000          |  |

| Area (µm2)                  | 93.139                    | 110.779           |  |

| EDP 10 <sup>-24</sup> (J-s) | 19.310                    | 17.500            |  |

#### 2.4 7-3 COMPRESSORS

Nirlakalla et al. [2] proposed a (7:3) compressor consisted of 4 full adders. 5 types of adders such as Transmission Gate (TG) CMOS, Transmission Function Full Adder (TFA), 16 Transistors (16-T), 14 Transistors (14-T), and Sense Energy Recovery Full Adder 10 Transistors (SERF 10-T) are being compared for (4:3), (5:3), (6:3), and (7:3) compressors. At gate level, via utilizing Xilinx ISE 9.1 synthesis tool simulations, 16-T full adder showed lowest PDP and EDP proving that it is the most energy efficient if compared to the other 4 types of adders mentioned. However, Nirlakalla et al. 2011 research has limitations as it does not consider the aspects of fan-in and area and these 2 aspects are vital since the fan-in of logic gates or area of compressors increase, the costs increase.

#### 2.5 8-3 COMPRESSORS

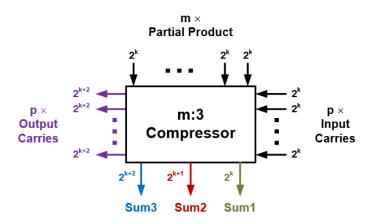

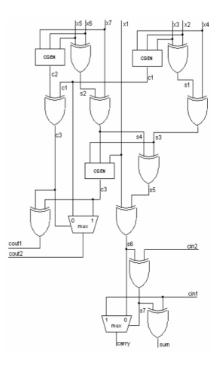

Dandapat et al. [3] proposed an 8:3 compressor design based on Figure 4 general structure of m:3 compressors. It consisted of 5 full adders and 2 half adders. Its implementation result with final ripple adder is stated in Table 3 which having lower data arrival time, lower power consumption, lower PDP and fewer connections than 8:2 compressors. However, it has larger total cell area which will be the factor of limiting the features of m:3 compressors within a specific area. Based on Figure 4, the formula can be derived as below:

$$\sum_{i=1}^{3} Output + \sum_{i=1}^{p} Output \ Carrier =$$

$$\sum_{i=1}^{m} Partial \ Product + \sum_{i=1}^{p} Input \ Carrier$$

[3]

$$2^{k} + 2^{k+1} + 2^{k+2} + px2^{k+2} = (m+p)x2^{k}$$

[3]

$$p = \left[\frac{m-7}{3}\right], p \ge 0 \qquad [3]$$

Since  $p = \frac{1}{3} > 0$  when m = 8, therefore, m = 1 (get ceiling)

However, Dandapat et al. does not consider the fan-in of logic gate. It is vital as the more fan-in of logic gate needed, the higher costs and higher complexity it is.

Figure 4: The Overall Proposed Structure of m:3 Compressor [3]

Figure 5: 8:3 New Hybrid Wide Compressor [15]

| Multiplier             | by only <i>m</i> :2<br>Compressors | by only <i>m</i> :3<br>Compressors |

|------------------------|------------------------------------|------------------------------------|

| Data Arrival Time      | 4.69 nsec                          | 4.46 nsec                          |

| Total Cell Area        | 4340.9 μm <sup>2</sup>             | 4428.4 μm <sup>2</sup>             |

| Cell Internal Power    | 1079.3 μW                          | 1002.9 μW                          |

| Net Switching<br>Power | 542.16 μW                          | 462.22 μW                          |

| Total Dynamic<br>Power | 1621.4 μW                          | 1465.2 μW                          |

| Cell Leakage Power     | 8.4090 μW                          | 8.4990 μW                          |

Table 3: Implementation Results with Final Ripple Adder [3]

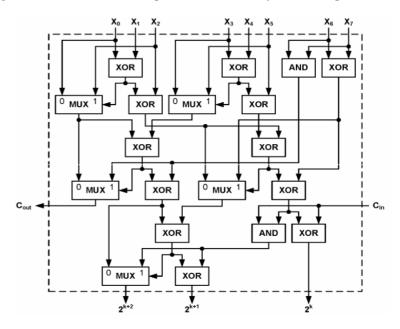

#### 2.6 7-2 COMPRESSORS

Rouholamini et. al. [14] proposed a 7:2 compressor consisted of 5 pieces of 3:2 compressors if compared to conventional 7:2 compressors which have 4 pieces of 3:2 compressors plus one final addition as shown in Figure 6. Both have 7 Exclusive-OR (XOR) gate delay. Referring to Table 4, the proposed 7:2 compressor has remarkable improvements in terms of power consumption from 0.07% (at 3.5V) to maximum of 11% (at 1.2V) and speed from 19% (at 3.5V) to 23% (at 1.2V) with respect to conventional 7:2 compressor has lower value than the conventional 7:2 compressor. By utilizing HSPICE simulator, the above simulations can be carried out as expected.

Figure 6: The Overall Proposed Structure of 7:2 Compressor [14]

# Table 4: Evaluation of Proposed 7:2 Compressor with respect to Conventional 7:2 Compressor [14]

|                                  | Min.<br>(3.5v) | Max.<br>(1.2v) |

|----------------------------------|----------------|----------------|

| Improvement in power consumption | 0.07 %         | 11 %           |

| Improvement in speed             | 19 %           | 23 %           |

## **CHAPTER 3: METHODOLOGY**

## 3.1 RESEARCH METHODOLOGY

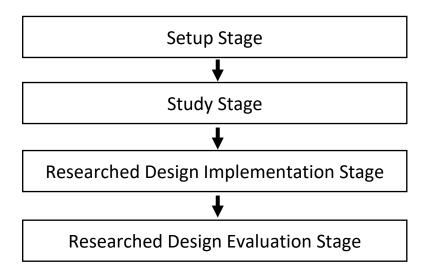

Figure 7: Research Methodology Used in Project

In this project, the research methodology can be categorized into four that are background study, tools used, design implementations, and further development plan.

The project started by having the background study of the concepts of compressors and different types of compressors have currently. The research papers related to compressors can be obtained from Institute of Electrical and Electronics Engineers (IEEE) Xplore Digital Library. I also approached my Final Year Project (FYP) supervisor to consult about the compressors in order to clear my doubts and have a better understanding to it.

Under tools used, it can be categorized into two, hardware and software. Under the hardware part, field-programmable gate array (FPGA) is used as it contains arrays of programmable logic blocks allowed to be configured to perform complex combination functions and it is useful when coming to designing the 8-3 compressor. Under the software part, 2 software that will be used are Altera Quartus II Web Edition and ModelSim-Altera to perform functional and timing simulation for researched compressor designs.

Under the researched designs implementation stage, the different types of researched compressor designs are implemented into FPGA to evaluate its performance in terms of fan-in, power consumption, cell area, and propagation delay. Then, the results of researched design compressors will be inter-compared with each other and determine the best way to design the 8-3 compressors which will give us the best compressor performance.

For further development, if extra time is allowed, 8-3 compressor will be designed and implemented into FPGA to evaluate and compared with the researched designs. Not to mention, the issues such as propagation delay, cell area, and power consumption have to be considered as well when designing the 8-3 compressors.

#### **3.2 RESEARCH ACTIVITIES**

Figure 8: Research Activities Used in Project

The research activities of this project can be divided into 4 parts which are setup stage, study stage, researched design implementation stages, and researched design evaluation stage.

Under the setup stage, 2 software will be installed that are Altera Quartus II Web Edition and ModelSim-Altera to allow performing the functional and timing simulation to the compressor designed. Verilog hardware description language (HDL) will also be studied in order to have basic idea on writing the compressor design (Finite State Machine or FSM of compressor) and test bench as it is commonly used in design and verification of digital circuits at the register-transfer level (RTL).

Under the study stage, a few research papers have been studied and understood their basic idea on designing a good compressor needs. The research data has to be well-analysed in terms of propagation delay, area of cell, power consumption, and number of logic gates used. Under the researched design implementation stage, several researched compressor designs will be implemented in into Altera Quartus II Web Edition. The researched design implemented can be known as finite-state machine. It is a model used to represent and control execution flow. The researched compressor designs are implemented using Verilog hardware description language as it includes ways of describing the propagation time and signal behaviour.

Last but not least, under the researched design evaluation stage, the researched compressor designs will be assessed by performing functional and timing simulation. Running functional simulation is to make sure that the researched compressor design implemented can handle all possible inputs and give expected output while running timing simulation is to evaluate the researched compressor design implemented from the view of real-time performance. To have better understanding on how the researched compressor designs work, it is implemented into FPGA to check its behaviour from the aspect of hardware devices. The propagation delay and power consumption will be recorded for further analysis.

# 3.3 PROJECT KEY MILESTONES (FINAL YEAR PROJECT I)

| ✓ | Collect and Analyse Researched Design             | : Week 5 |

|---|---------------------------------------------------|----------|

| √ | Install Simulation Software                       | : Week 6 |

| √ | Study Verilog Hardware Description Language (HDL) | : Week 6 |

| √ | Implemented 3 Researched Designs                  | : Week 9 |

| √ | Study the Implemented Researched Designs          | : Week   |

|   | 12                                                |          |

| √ | Proposed 8-3 Compressor Design Requirement        | : Week   |

|   | 13                                                |          |

## 3.4 PROJECT KEY MILESTONES (FINAL YEAR PROJECT II)

| ✓ | Generate random data to be processed by compressors         | : |

|---|-------------------------------------------------------------|---|

|   | Week 4                                                      |   |

| ✓ | Progress Report Submission                                  | : |

|   | Week 8                                                      |   |

| ✓ | Pre-Sedex Presentation                                      | : |

|   | Week 10                                                     |   |

| ✓ | Implemented 8 Researched Designs and Analyse Simulated Data | : |

|   | Week 11                                                     |   |

| ✓ | Draft Final Report Submission                               | : |

|   | Week 13                                                     |   |

| ✓ | Final Report & Technical Report Submission                  | : |

|   | Week 14                                                     |   |

| ✓ | Viva Presentation                                           | : |

|   | Week 15                                                     |   |

## 3.5 PROJECT TIMELINES (GANTT-CHART FOR FINAL YEAR PROJECT I)

| Activity Week                                                                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

|----------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|

| Title Selection / Proposal                                                       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Collect and Analyse Data                                                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Extended Proposal                                                        |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Install Altera Quartus II Web Edition &<br>ModelSim-Altera and Learn to Simulate |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Implement Researched Design in Simulator                                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Proposal Defense                                                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Study Implemented Researched Designs in<br>Depth                                 |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Proposed 8-3 Compressor Design<br>Requirement                                    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Draft Report                                                             |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Final Report                                                             |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

Table 5: Gantt chart for Final Year Project I

## **<u>3.6 PROJECT TIMELINES (GANTT-CHART FOR FINAL YEAR PROJECT II)</u>**

| Activity Week                                                                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

|----------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|

| Research on generating random data for implemented compressor designs to process |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Implement researched compressor designs                                          |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Collect and Analyse Data                                                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Progress Report                                                          |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare for Pre-Sedex                                                            |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Draft Final Report                                                       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Dissertation (Soft Bound)                                                |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Technical Paper                                                          |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Prepare Project Dissertation (Hard Bound)                                        |   |   |   |   |   |   |   |   |   |    |    |    |    |    |

Table 6: Gantt chart for Final Year Project II

## **CHAPTER 4: RESULTS AND DISCUSSIONS**

## 4.1 8-3 COMPRESSOR (FULL AND HALF ADDERS)

| Minir | mum Progagat | ion Delay   |       |

|-------|--------------|-------------|-------|

|       | Input Port   | Output Port | RŘ    |

| 1     | iSW[7]       | oLEDG[1]    | 5.994 |

| 2     | iSW[7]       | oLEDG[0]    | 5.967 |

| 3     | iSW[6]       | oLEDG[1]    | 5.941 |

| 4     | iSW[6]       | oLEDG[0]    | 5.914 |

| 5     | iSW[7]       | oLEDG[2]    | 5.889 |

| 6     | iSW[5]       | oLEDG[1]    | 5.872 |

| 7     | iSW[5]       | oLEDG[0]    | 5.844 |

| 8     | iSW[6]       | oLEDG[2]    | 5.836 |

| 9     | iSW[1]       | oLEDG[1]    | 5.793 |

| 10    | iSW[5]       | oLEDG[2]    | 5.767 |

| 11    | iSW[1]       | oLEDG[0]    | 5.730 |

| 12    | iSW[0]       | oLEDG[1]    | 5.724 |

| 13    | iSW[3]       | oLEDG[1]    | 5.690 |

| 14    | iSW[1]       | oLEDG[2]    | 5.688 |

| 15    | iSW[0]       | oLEDG[0]    | 5.687 |

| 16    | iSW[2]       | oLEDG[0]    | 5.659 |

| 17    | iSW[0]       | oLEDG[2]    | 5.619 |

| 18    | iSW[3]       | oLEDG[0]    | 5.612 |

| 19    | iSW[3]       | oLEDG[2]    | 5.585 |

| 20    | iSW[4]       | oLEDG[1]    | 5.572 |

| 21    | iSW[2]       | oLEDG[1]    | 5.564 |

| 22    | iSW[4]       | oLEDG[0]    | 5.486 |

| 23    | iSW[4]       | oLEDG[2]    | 5.467 |

| 24    | iSW[2]       | oLEDG[2]    | 5.459 |

Figure 9: Minimum 8-3 Compressor Propagation Delay [12]

| Prog | agation Delay |             |        |

|------|---------------|-------------|--------|

|      | Input Port    | Output Port | RŘ     |

| 1    | iSW[7]        | oLEDG[1]    | 11.287 |

| 2    | iSW[7]        | oLEDG[2]    | 11.260 |

| 3    | iSW[6]        | oLEDG[1]    | 11.167 |

| 4    | iSW[6]        | oLEDG[2]    | 11.137 |

| 5    | iSW[7]        | oLEDG[0]    | 11.017 |

| 6    | iSW[5]        | oLEDG[1]    | 11.016 |

| 7    | iSW[5]        | oLEDG[2]    | 10.991 |

| 8    | iSW[6]        | oLEDG[0]    | 10.897 |

| 9    | iSW[1]        | oLEDG[1]    | 10.795 |

| 10   | iSW[1]        | oLEDG[2]    | 10.768 |

| 11   | iSW[5]        | oLEDG[0]    | 10.746 |

| 12   | iSW[2]        | oLEDG[2]    | 10.704 |

| 13   | iSW[0]        | oLEDG[1]    | 10.699 |

| 14   | iSW[0]        | oLEDG[2]    | 10.664 |

| 15   | iSW[4]        | oLEDG[2]    | 10.663 |

| 16   | iSW[2]        | oLEDG[1]    | 10.631 |

| 17   | iSW[4]        | oLEDG[1]    | 10.554 |

| 18   | iSW[3]        | oLEDG[2]    | 10.542 |

| 19   | iSW[1]        | oLEDG[0]    | 10.524 |

| 20   | iSW[3]        | oLEDG[1]    | 10.444 |

| 21   | iSW[0]        | oLEDG[0]    | 10.428 |

| 22   | iSW[2]        | oLEDG[0]    | 10.361 |

| 23   | iSW[3]        | oLEDG[0]    | 10.174 |

| 24   | iSW[4]        | oLEDG[0]    | 9.902  |

Figure 10: 8-3 Compressor Propagation Delay [12]

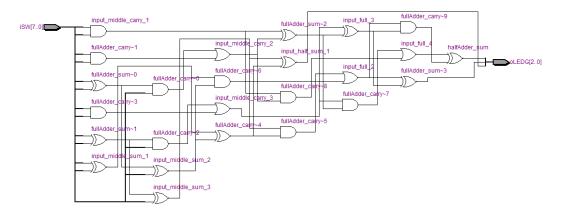

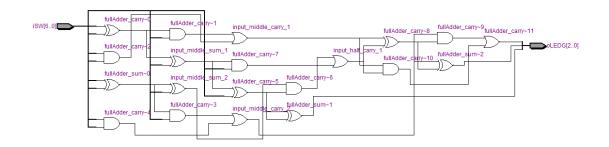

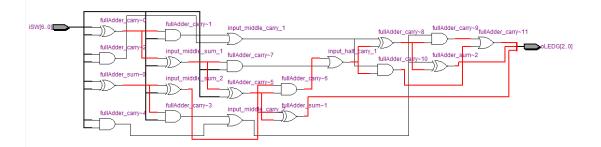

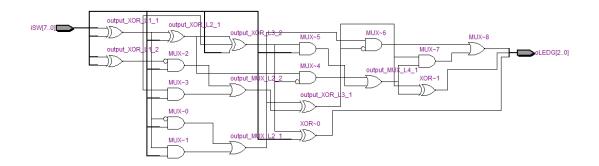

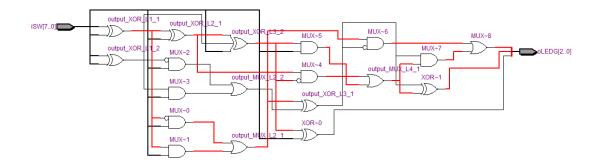

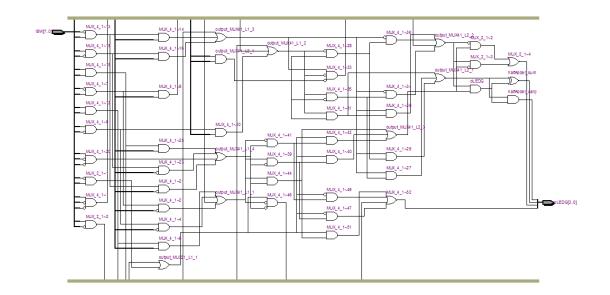

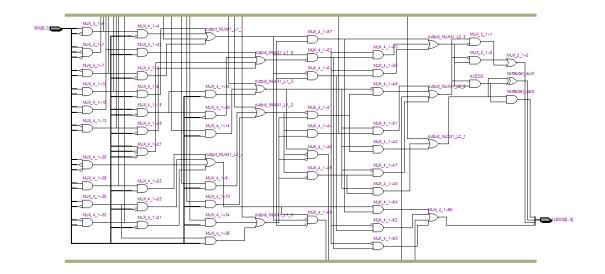

By referring to Figure 9 and Figure 10, it can clearly be seen that both the minimum propagation delay and simulated propagation delay has maximum value on input iSW[7] and output oLEDG[1]. This means that the critical path of 8-3 compressor model is the path that allowed signals to pass through from input iSW[7] to output oLEDG[1]. There are several values shown in Figure 9 and Figure 10. However, in this case, RR value is concerned in this design as this design is focusing on rising edge of clock at both source and destination. In order to have better understanding about the 8-3 compressor model, Register Transfer Level (RTL) view of circuit is shown in *Figure 11*.

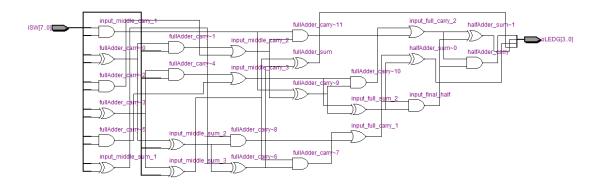

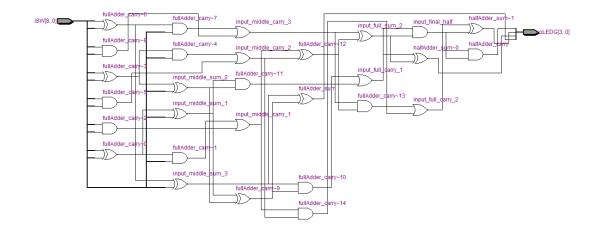

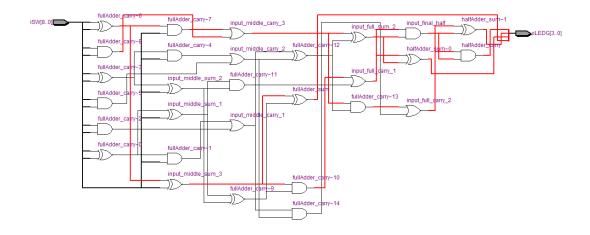

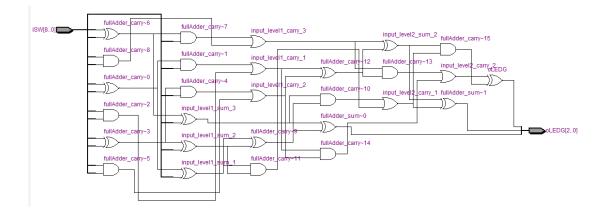

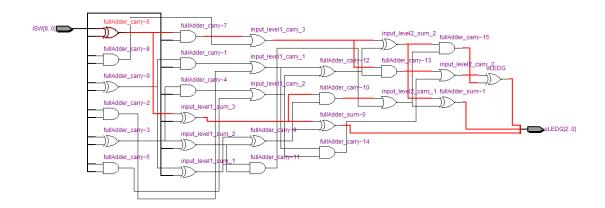

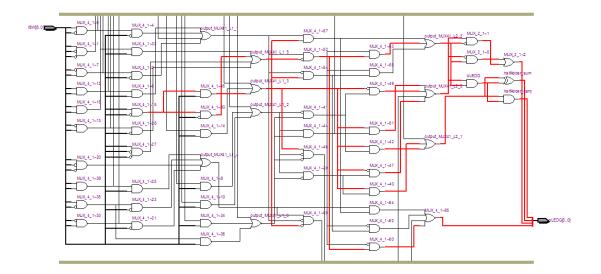

Figure 11: RTL View of 8-3 Compressor Model [12]

Figure 12: RTL View in Relationship with Input iSW[7] and Output oLEDG[1] [12]

*Figure 11* shows the RTL view of 8-3 compressor model. As we can see, the compressor model consisted of 10 AND gates, 11 XOR gates, and 4 OR gates. With input iSW[7] and output oLEDG[1] as shown in *Figure 12*, there are 4 AND gates, 5 XOR gates, and 3 OR gates involved. In RTL circuit, theoretically, XOR gates will be contributing most of the propagation delay if compared to AND gates and OR gates propagation delay.

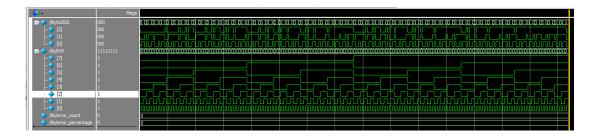

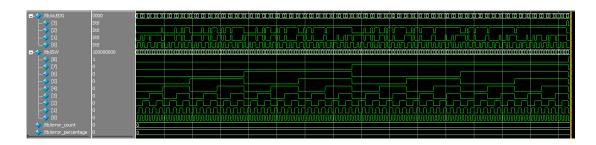

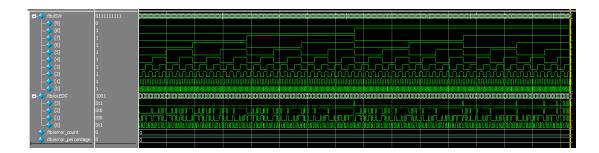

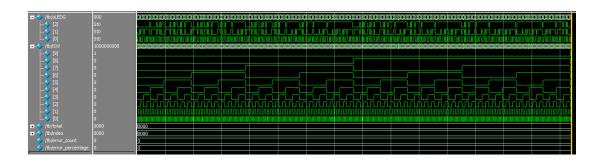

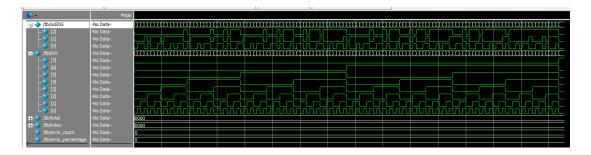

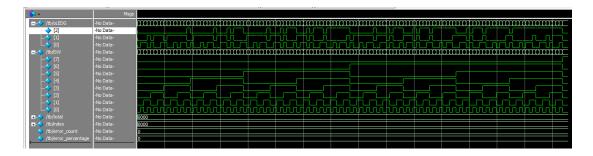

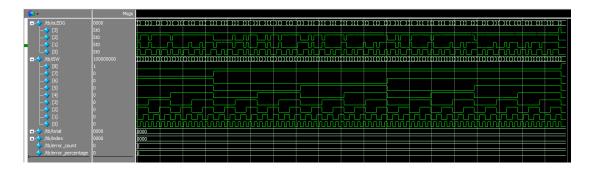

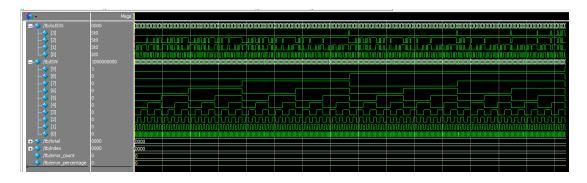

Figure 13: 8-3 Compressor Functional Simulation using ModelSim-Altera

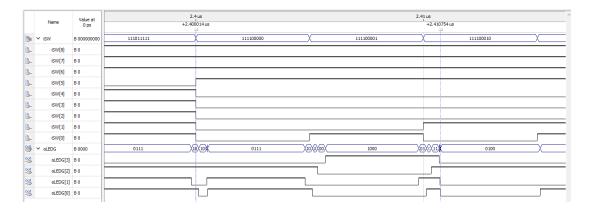

The 8-3 compressor model and self-written functional test bench are written using Verilog Hardware Description Language as shown in *Figure 74* and *Figure 75* based on Shima et al. researched proposal [12] which consisted of 5 full adders and 2 half adders. The reason of using functional test bench simulation is to make sure that the compressor designed is functioning as expected when fixed inputs are inserted and the expected output obtained. The 8-3 compressor model undergone functional selfwritten functional test bench which tested with inputs from 0 (000000<sub>2</sub>) to 255 (1111111<sub>2</sub>) and observed the outputs of 8-3 compressor model ranged from 0 (000<sub>2</sub>) to 7 (111<sub>2</sub>). Figure 10 above shows the functional simulation for 8-3 compressor using the self-written test bench with the aids of ModelSim-Altera.

```

The data input is 255

Total = 8, oLEDG = 0

Ok. Result = 8

Total Error Count = 0.00

The Failing Rate for Functional Testbench is 0.00

```

#### Figure 14: Error Result of 8-3 Compressor Functional Test bench on Console

Figure 13 above shows the number of error counts and percentage of error of outputs in 8-bits different combinations of inputs for 8-3 compressor model. The above error count is 0 after running 8-bits different combinations of inputs indicating the 8-3 compressor model is designed properly as expected.

|            | Name     | Value at<br>0 ps | 0 ps 80.0 ns 160.0 ns 240.0 ns 320.0 ns 400.0 ns 480.0 ns 560.0 ns 640.0 ns 720.0 ns 800.0 ns 880.0 ns 960.0 ns 1.04 us 1.12 us 1.2 us 1.28 us 1.36 us 1.44 us 0 ps |

|------------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ✓ iSW    | в 00000000       |                                                                                                                                                                     |

| <u>in</u>  | iSW[7]   | в 0              |                                                                                                                                                                     |

| in_        | iSW[6]   | в 0              |                                                                                                                                                                     |

| in_        | iSW[5]   | в 0              |                                                                                                                                                                     |

| in_        | ISW[4]   | в 0              |                                                                                                                                                                     |

| ₿-         | iSW[3]   | в 0              |                                                                                                                                                                     |

| ₿-         | iSW[2]   | B 0              |                                                                                                                                                                     |

| <u>in</u>  | iSW[1]   | в 0              |                                                                                                                                                                     |

| in_        | iSW[0]   | в 0              |                                                                                                                                                                     |

| 쐥          | ✓ oLEDG  | B 000            | on a charachta a bhair ann an an an an an an ann ann an an ann an a                                                                                                 |

| °≝t        | oLEDG[2] | в 0              |                                                                                                                                                                     |

| ᅄ          | oLEDG[1] | в 0              |                                                                                                                                                                     |

| <u>eut</u> | oLEDG[0] | в 0              |                                                                                                                                                                     |

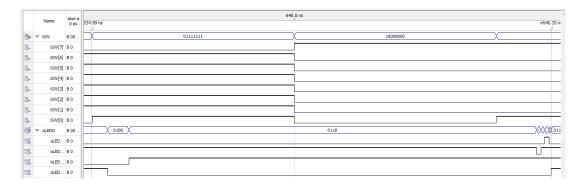

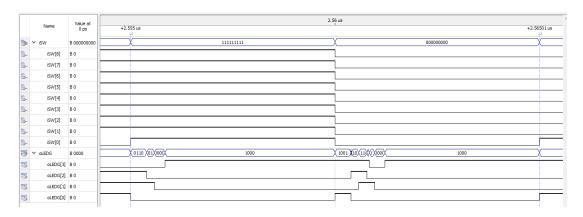

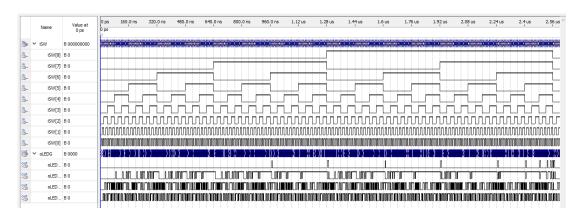

Figure 15: Overall 8-3 Compressor Model Timing Simulation

Figure 16: Timing Simulation for iSW[0..7] with bit 1s and output oLEDG[0..2]

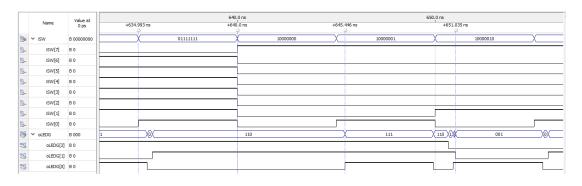

*Figure 15* shows the overall timing simulation for 8-3 compressor model designed. Timing simulation is used to emulate an implementation into real devices such as Field Programmable Gate Array (FPGA) to satisfy all the timing and functional needs. The input iSW[0] is inserted with signal 1 for each 10ns period with 50% duty cycle. The input iSW[1] is inserted with signal 1 for each 20 ns which is double period of previous iSW that is iSW[0] with also 50% duty cycle. The method of inputting the signals are applied to other inputs iSW[2..7].

*Figure 16* shows the timing simulation for the critical path of 8-3 compressor model. Referring to Figure 9 and Figure 10, it can be noticed that input iSW[7] and output oLEDG[1] will have the maximum propagation delay. To prove the statement, Figure 13 data is obtained and compared in *Table 7*.

| Input(s) with | Start Input | Start Output | Output – Input | Percentage |  |

|---------------|-------------|--------------|----------------|------------|--|

| 1s            | Transition  | Transition   | Transition     | Error      |  |

| iSW[07]       | 634.993 ns  | 645.446 ns   | 10.453 ns      | 1.6462 %   |  |

Table 7: Propagation Delay of input iSW[0..7] with Input 1s

|    | Input Port | Output Port | RĚ    |

|----|------------|-------------|-------|

| 1  | iSW[0]     | oLEDG[3]    | 5.984 |

| 2  | iSW[0]     | oLEDG[1]    | 5.883 |

| 3  | iSW[0]     | oLEDG[2]    | 5.883 |

| 4  | iSW[1]     | oLEDG[3]    | 5.883 |

| 5  | iSW[2]     | oLEDG[3]    | 5.862 |

| 6  | iSW[6]     | oLEDG[3]    | 5.832 |

| 7  | iSW[3]     | oLEDG[3]    | 5.79  |

| 8  | iSW[1]     | oLEDG[1]    | 5.787 |

| 9  | iSW[1]     | oLEDG[2]    | 5.78  |

| 10 | iSW[6]     | oLEDG[1]    | 5.77  |

| 11 | iSW[2]     | oLEDG[2]    | 5.76  |

| 12 | iSW[2]     | oLEDG[1]    | 5.746 |

| 13 | iSW[6]     | oLEDG[2]    | 5.73  |

| 14 | iSW[7]     | oLEDG[3]    | 5.70  |

| 15 | iSW[3]     | oLEDG[2]    | 5.690 |

| 16 | iSW[0]     | oLEDG[0]    | 5.67  |

| 17 | iSW[3]     | oLEDG[1]    | 5.65  |

| 18 | iSW[7]     | oLEDG[1]    | 5.650 |

| 19 | iSW[6]     | oLEDG[0]    | 5.63  |

| 20 | iSW[7]     | oLEDG[2]    | 5.602 |

| 21 | iSW[1]     | oLEDG[0]    | 5.576 |

| 22 | iSW[2]     | oLEDG[0]    | 5.53  |

| 23 | iSW[7]     | oLEDG[0]    | 5.498 |

| 24 | iSW[3]     | oLEDG[0]    | 5.440 |

| 25 | iSW[5]     | oLEDG[3]    | 3.41  |

| 26 | iSW[5]     | oLEDG[1]    | 3.358 |

| 27 | iSW[5]     | oLEDG[2]    | 3.310 |

| 28 | iSW[5]     | oLEDG[0]    | 3.207 |

| 29 | iSW[4]     | oLEDG[3]    | 3.188 |

| 30 | iSW[4]     | oLEDG[2]    | 3.106 |

| 31 | iSW[4]     | oLEDG[1]    | 3.005 |

| 32 | iSW[4]     | oLEDG[0]    | 2.793 |

Figure 17: Minimum 8-4 Compressor Model Propagation Delay [1]

|    | Input Port | Output Port | RŘ     |

|----|------------|-------------|--------|

| 1  | iSW[0]     | oLEDG[3]    | 11.305 |

| 2  | iSW[6]     | oLEDG[3]    | 11.217 |

| 3  | iSW[0]     | oLEDG[2]    | 11.109 |

| 4  | iSW[1]     | oLEDG[3]    | 11.035 |

| 5  | iSW[6]     | oLEDG[2]    | 11.021 |

| 6  | iSW[2]     | oLEDG[3]    | 10.992 |

| 7  | iSW[0]     | oLEDG[1]    | 10.973 |

| 8  | iSW[7]     | oLEDG[3]    | 10.909 |

| 9  | iSW[1]     | oLEDG[2]    | 10.839 |

| 10 | iSW[6]     | oLEDG[1]    | 10.825 |

| 11 | iSW[2]     | oLEDG[2]    | 10.796 |

| 12 | iSW[3]     | oLEDG[3]    | 10.784 |

| 13 | iSW[1]     | oLEDG[1]    | 10.730 |

| 14 | iSW[2]     | oLEDG[1]    | 10.726 |

| 15 | iSW[7]     | oLEDG[2]    | 10.713 |

| 16 | iSW[3]     | oLEDG[2]    | 10.588 |

| 17 | iSW[7]     | oLEDG[1]    | 10.517 |

| 18 | iSW[3]     | oLEDG[1]    | 10.512 |

| 19 | iSW[0]     | oLEDG[0]    | 10.380 |

| 20 | iSW[6]     | oLEDG[0]    | 10.291 |

| 21 | iSW[1]     | oLEDG[0]    | 10.110 |

| 22 | iSW[2]     | oLEDG[0]    | 10.067 |

| 23 | iSW[7]     | oLEDG[0]    | 9.983  |

| 24 | iSW[3]     | oLEDG[0]    | 9.859  |

| 25 | iSW[5]     | oLEDG[3]    | 7.276  |

| 26 | iSW[5]     | oLEDG[2]    | 7.080  |

| 27 | iSW[4]     | oLEDG[3]    | 6.966  |

| 28 | iSW[5]     | oLEDG[1]    | 6.884  |

| 29 | iSW[4]     | oLEDG[2]    | 6.770  |

| 30 | iSW[4]     | oLEDG[1]    | 6.749  |

| 31 | iSW[5]     | oLEDG[0]    | 6.350  |

| 32 | iSW[4]     | oLEDG[0]    | 5.370  |

Figure 18: 8-4 Compressor Model Maximum Propagation Delay [1]

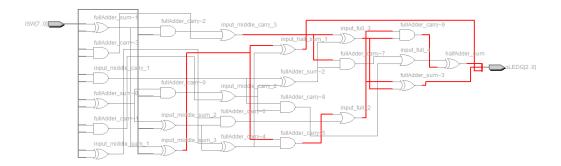

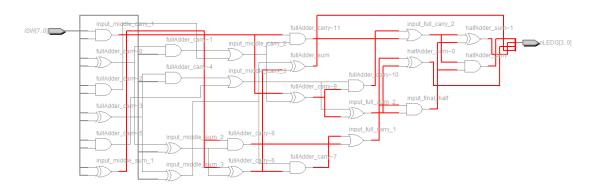

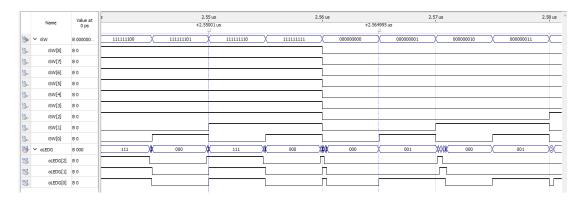

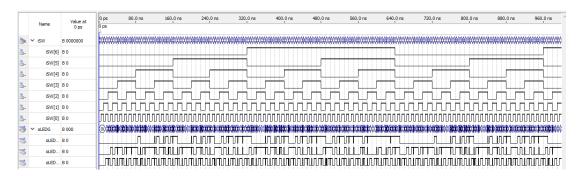

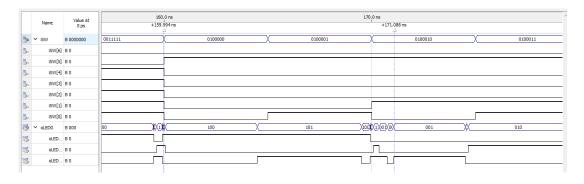

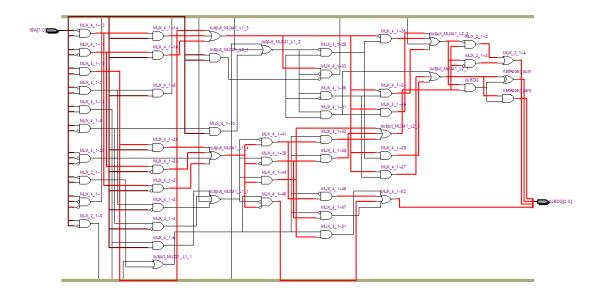

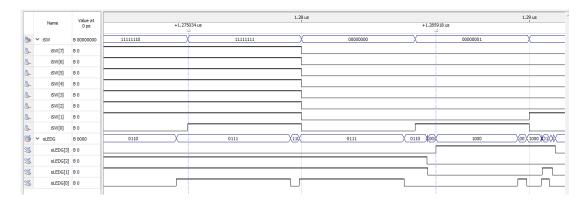

By referring to *Figure 17* and *Figure 18*, it can clearly be seen that both the minimum propagation delay and simulated propagation delay has maximum value on input iSW[0] and output oLEDG[3]. This means that the critical path of 8-4 compressor model is the path that allowed signals to pass through from input iSW[0] to output oLEDG[3]. There are several values shown in *Figure 17* and *Figure 18*. However, in this case, RR value is concerned in this design as this design is focusing on rising edge of clock at both source and destination. The critical path is the path between the input and output with maximum circuit delay. To have better understanding about 8-4 compressor model, RTL view of circuit is shown in *Figure 19*.

Figure 19: Overall RTL View of 8-4 Compressor Model [1]

Figure 20: RTL View in Relationship with Input iSW[0] and Output oLEDG[3] [1]

*Figure 19* shows the RTL view of 8-4 compressor model. As we can see, the compressor model consisted of 11 AND gates, 11 XOR gates, and 2 OR gates. With input iSW[0] and output oLEDG[3] as shown in *Figure 20*, there are 7 AND gates, 7 XOR gates, and 2 OR gates involved. In RTL circuit, theoretically, XOR gates will be contributing most of the propagation delay if compared to AND gates and OR gates propagation delay. In other words, when the number of XOR gates increases, the propagation delay of the compressor will be increased dramatically.

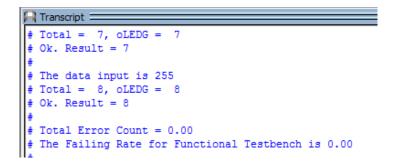

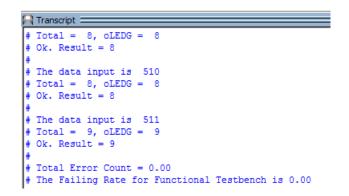

Figure 21: 8-4 Compressor Functional Simulation using ModelSim-Altera

The 8-4 compressor model and self-written functional test bench are written using Verilog Hardware Description Language as shown in *Figure 76* and *Figure 77* based on R.Marimuthu, et al. researched proposal [1] which consisted of 4 full adders and 3 half adders. The 8-4 compressor model undergone functional self-written functional test bench which tested with inputs from 0 (0000002) to 255 (11111112) and observed the outputs of 8-4 compressor model ranged from 0 (00002) to 8 (10002). *Figure 21* above shows the functional simulation for 8-4 compressor using the selfwritten test bench with the aids of ModelSim-Altera.

```

The data input is 255

Total = 8, oLEDG = 8

Ok. Result = 8

Total Error Count = 0.00

The Failing Rate for Functional Testbench is 0.00

```

Figure 22: Error Result of 8-4 Compressor Functional Test bench on Console

*Figure 22* above shows the number of error counts and percentage of error of outputs in 8-bits different combinations of inputs for 8-4 compressor model. The above error count is 0 after running 8-bits different combinations of inputs indicating the 8-4 compressor model is designed properly as expected.

|            | Name    | Value at<br>0 ps | 0 ps 80.0 ns 150.0 ns 240.0 ns 320.0 ns 400.0 ns 480.0 ns 550.0 ns 640.0 ns 720.0 ns 800.0 ns 880.0 ns 960.0 ns 1.04 us 1.12 us 1.24 us 1.28 us 1.35 us 1.44 us<br>0 ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>i</u>   | ✓ iSW   | B 00000000       | The second second second as a second descendence of the second descendence of the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| in_        | ISW[7]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| in_        | ISW[6]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| in_        | ISW[5]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| in_        | ISW[4]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ≞-         | ISW[3]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ₽.         | ISW[2]  | B 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |