# EXPERIMENTAL ANALYSIS OF GATE DRIVE CONTROL SYSTEM FOR SYNCHRONOUS DC/DC CONVERTER

BY

#### SITI NABILAH BT ABDUL RAHIM

#### FINAL YEAR PROJECT II

# Submitted to the Department of Electrical & Electronic Engineering in Partial Fulfilment of the Requirements

for the Degree

Bachelor of Engineering (Hons) (Electrical & Electronic Engineering)

Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh

Perak Darul Ridzuan

© Copyright 2012 by Siti Nabilah bt Abdul Rahim, 2012.

### **CERTIFICATION OF APPROVAL**

# EXPERIMENTAL ANALYSIS OF GATE DRIVE CONTROL SYSTEM FOR SYNCHRONOUS DC/DC CONVERTER

by

Siti Nabilah bt Abdul Rahim

A project dissertation submitted to the Department of Electrical & Electronic Engineering Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronic Engineering)

Approved:

Dr. Nor Zaihar Bin Yahaya,

Project Supervisor

# UNIVERSITI TEKNOLOGI PETRONAS

### TRONOH, PERAK

December 2012

## **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Siti Nabilah bt Abdul Rahim

### ABSTRACT

The design of the PCB board is important as it affects the overall performance of the overall system. The most common problem that affects the performance and efficiency of the PCB board are partitioning of the circuits, the problem of interconnecting traces, grounding schemes and thermal management. Overall, the primary objectives of the project are to understand the process flow of PCB and to acquire knowledge about PCB fabrication. Meanwhile, the secondary objectives of the project are to apply high frequency DC-DC Converter on PCB fabrication and lastly to test and verify the output of PCB fabrication. SRBC-PWM and SRBC-compensator-AGD are successfully implemented on PCB board. The knowledge about PCB design is acquired and the problems overcome while fabricating PCB are managed to overcome.

#### ACKNOWLEDGEMENTS

I would like to acknowledge those that have actively contributed and supporting me towards completing this Final Year Project (FYP) 1 and 2. In my endeavour to gain as much knowledge and experience during completion of final year project, your inputs have been a tremendous help to me especially regarding technical knowledge and facilities.

First and foremost, special thanks to Dr. Nor Zaihar Bin Yahaya and Mrs. Zazilah Binti May as my supervisor for their motivation, support and guidance for me towards completion of this project. Indeed, their sacrifice and seriousness for guiding me will always be remembered. Most importantly, special thanks to all my family members, especially both my parents Mr Abdul Rahim Bin Senik and Mrs Saleha Bt Yusoff, and my friends for all the support and motivation given along the journey.

Last but not least, I would like to extend my gratitude to anyone who has assisted me directly or indirectly in making my Final Year Project a success.

Thank you.

SITI NABILAH BT ABDUL RAHIM Electrical & Electronics Engineering Department Universiti Teknologi PETRONAS

## **TABLE OF CONTENTS**

### **1.0 PROJECT BACKGROUND**

| 1.1 | Background of Research       | 3 |

|-----|------------------------------|---|

| 1.2 | Problem Statement            | 5 |

| 1.3 | Objectives of Research       | 6 |

| 1.4 | Relevancy of the Research    | 6 |

| 1.5 | Challenges                   | 6 |

| 1.6 | Significant of Project       | 7 |

| 1.7 | Contribution of the Research | 7 |

### 2.0 LITERATURE REVIEW

| 2.1 | Printed Circuit Board                | 8  |

|-----|--------------------------------------|----|

| 2.2 | Partitioning of the PCB Layout       | 9  |

| 2.3 | Grounding Schemes of PCB             | 10 |

| 2.4 | Synchronous Rectifier Buck Converter | 13 |

| 2.5 | Pulse Width Modulation               | 16 |

| 2.6 | Adaptive Gate Drive                  |    |

### 3.0 METHODOLOGY

| 3.1 | Projec      | t Flow                                           | 20       |  |  |  |

|-----|-------------|--------------------------------------------------|----------|--|--|--|

| 3.2 | Gantt chart |                                                  |          |  |  |  |

| 3.3 | Softwa      | are and Tool Required                            | 24       |  |  |  |

| 3.4 | Proces      | ss Flow of PCB                                   | 25       |  |  |  |

| 3.5 | Know        | ledge About PCB Fabrication                      |          |  |  |  |

| 3.6 | Apply       | ing High Frequency DC-DC Converter on PCB Applic | ation.28 |  |  |  |

|     | 3.6.1       | Adaptive Gate Drive                              | 29       |  |  |  |

|     | 3.6.2       | SRBC with Compensator -AGD                       | 30       |  |  |  |

|     | 3.6.3       | SRBC with PWM                                    |          |  |  |  |

| 3.7 | Testin      | g and Verify the Output of PCB fabrication       | 32       |  |  |  |

| 3.8 | Circui      | t Parameters                                     |          |  |  |  |

| 4.0 | RESU | LTS AND FINDING                                   | 35  |

|-----|------|---------------------------------------------------|-----|

|     | 4.1  | PCB Artwork                                       | .35 |

|     | 4.2  | PCB Knowledge                                     | .37 |

|     | 4.3  | Circuit Results                                   | .38 |

|     |      | 4.3.1 SRBC                                        | .38 |

|     |      | 4.3.2 SRBC with Compensator -AGD                  | .38 |

|     | 4.4  | Comparison between Simulation and Experimentation | 41  |

| 5.0 | CONCLUSION | 46 |

|-----|------------|----|

|     |            |    |

| 6.0 | REFERENCES | 47 |

## **LIST OF FIGURE**

| Figure 1: Circuit Design on Breadboard                  | 3  |

|---------------------------------------------------------|----|

| Figure 2: Circuit Design Using PCB Fabrication          | 4  |

| Figure 3: Fabrication Flow Chart for Single-Sided PCB   | 7  |

| Figure 4: Photo-Resist Board                            | 8  |

| Figure 5: PCB Mask + Photo Resist Board                 | 8  |

| Figure 6: An Operational model of Faraday Shield        | 9  |

| Figure 7: Ground Loop                                   | 7  |

| Figure 8: Layout of Guard Ring                          | 11 |

| Figure 9: Decoupling Capacitor                          | 12 |

| Figure 10: Synchronous Rectifier Buck Converter Circuit | 13 |

| Figure 11: Synchronous Switching using PWM              | 14 |

| Figure 12: Example of PWM Signal                        | 15 |

| Figure 13: The Generation of PWM Signal                 | 16 |

| Figure 14: FDR Control Signal                           | 17 |

| Figure 15: Digital Delay Line for AGD Control Circuit   | 18 |

| Figure 16: Project Flow of the Project                  | 19 |

| Figure 17: Routing Rules of PCB                         | 25 |

| Figure 18: Auto Routing of PCB                          | 26 |

| Figure 19: Adaptive Gate Drive Circuit Schematic        | 28 |

| Figure 20: SRBC-Compensator-AGD Schematic               | 29 |

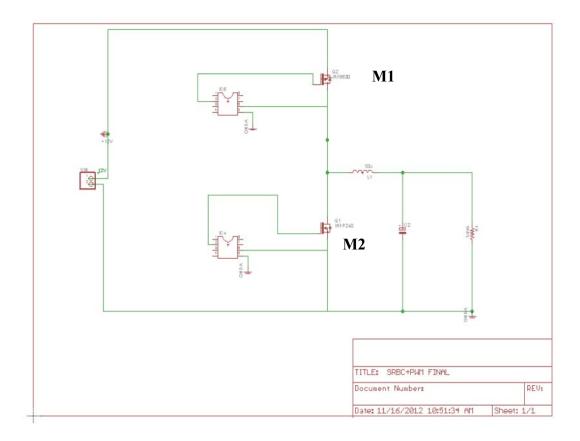

| Figure 21: SRBC-PWM schematics                          | 30 |

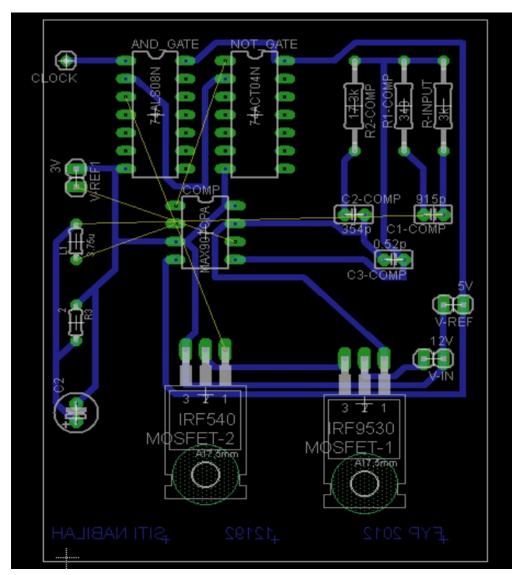

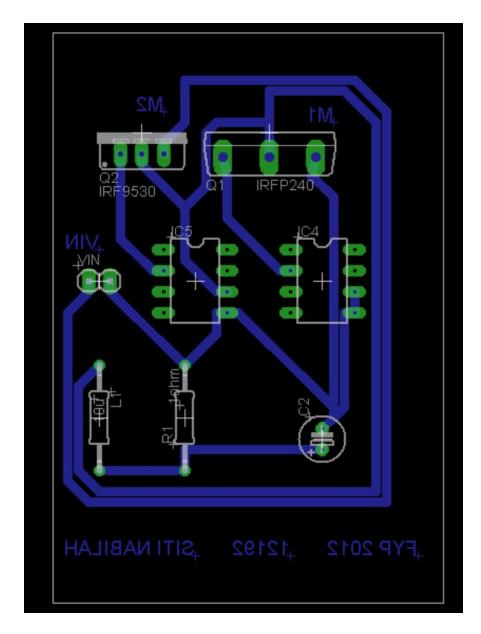

| Figure 22: SRBC-Compensator- AGD PCB Layout             | 32 |

| Figure 23: SRBC-PWM Layout                              | 33 |

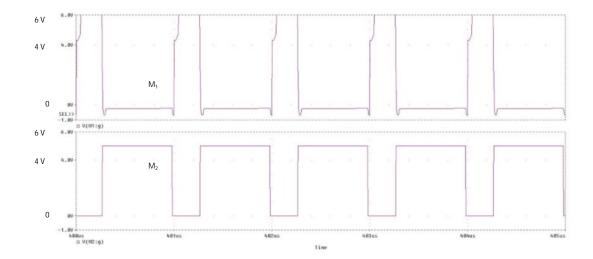

| Figure 24: PWM OF SRBC                                  | 38 |

| Figure 25: PWM OF SRBC- Compensator-AGD                 |    |

| Figure 26: Output Voltage for SRBC- PWM (simulation)                  | 41 |

|-----------------------------------------------------------------------|----|

| Figure 27: Output Voltage for SRBC- Compensator-AGD (simulation)      | 41 |

| Figure 28: Output Voltage for SRBC- PWM (experimentation)             | 42 |

| Figure 29: Output Voltage for SRBC- Compensator-AGD (experimentation) | 42 |

| Figure 30: Node Voltage for SRBC-PWM (simulation)                     | 43 |

| Figure 31: Node Voltage for SRBC-compensator-AGD (simulation)         | 43 |

| Figure 32: Node Voltage for SRBC-compensator-AGD (experimentation)    | 44 |

## LIST OF TABLE

| Table 1: Gantt Chart for Final Year 2                        | 22  |

|--------------------------------------------------------------|-----|

| Table 2: Details about Eagle Software                        | 23  |

| Table 3: Differential Signal Clearance                       | 27  |

| Table 4: Same Signal Clearance                               | 27  |

| Table 5: Simulation Parameters of SRBC with compensator- AGD | 33  |

| Table 6: Simulation Parameters for SRBC                      | .34 |

| Table 7: Comparison between Simulation and Experimentation   | .45 |

## LIST OF ABBREVIATION

| AGD            | Adaptive Gate Drive                         |

|----------------|---------------------------------------------|

| ССМ            | Continuous Conduction Mode                  |

| D              | Duty cycle                                  |

| DC             | Direct Current                              |

| DCM            | Discontinuous Conduction Mode               |

| MOSFET         | Metal Oxide silicon field effect transistor |

| PWM            | Pulse Width Modulation                      |

| SRBC           | Synchronous Rectifier Buck Converter        |

| $f_s$          | Switching frequency                         |

| $I_L$          | Inductor current                            |

| $P_{BD}$       | Body diode conduction losses                |

| $T_{BD}$       | Body diode conduction time                  |

| t <sub>D</sub> | Dead time                                   |

| $V_{ds}$       | Drain to source voltage                     |

| $V_{gs}$ .     | Gate to source voltage                      |

| Vref           | Reference voltage                           |

| Vin            | Input Voltage                               |

#### **CHAPTER 1: INTRODUCTION**

This chapter discusses the background of research work, problem statement, objective of the research, relevancy of the research, challenges faced towards completion of this project, significance of the project and contribution of project.

#### **1.1 Background of Research**

The project discusses about the experimentation of DC-DC Converter on the Printed Circuit Board (PCB). PCB is used to provide mechanical basis and electrically connect electronic components by using the conductive pathways and tracks from copper sheets laminated onto a non-conductive substrate. It will be mainly focused on the process flow of PCB fabrication and methodology on how to implement high frequency DC-DC Converter on PCB.

Circuits implemented on PCB fabrication will be Adaptive Gate Drive (AGD) and Synchronous Rectifiers Buck Converter (SRBC). This controller which is AGD will be incorporated with Synchronous Rectifier Buck Converter (SRBC) circuit using pulse width modulator (PWM) gate driver. The switching frequency applied is 500 kHz. SRBC is chosen because of its application in industry especially for lower power conversion.

In order to develop prototype on PCB, circuit will be firstly designed and simulated by using Eagle software.

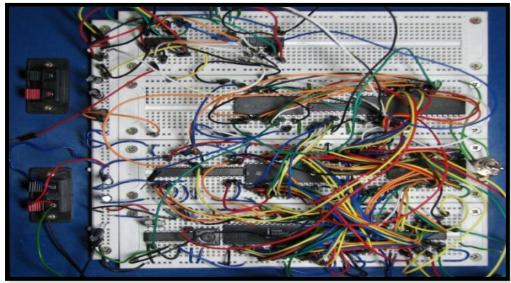

Figure 1: Circuit Design on Breadboard [1]

Figure 1 shows circuit designed on breadboard. The circuit is complex and not organized. In terms of testing, it is difficult to detect the circuit error since there is a lot of wiring on the board.

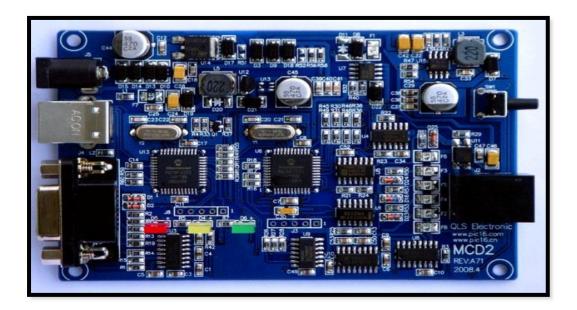

Figure 2 : Circuit Design using PCB fabrication [2]

Figure 2 shows circuit design using PCB fabrication. Circuit design is more organized and in terms of testing, it is easier to detect error and examine the output.

#### **1.2 Problem Statement**

Printed circuit boards (PCBs) have been commonly used in electronic devices, high definition displays, and high-density packages. However, increasing the benefits and performance rates of these interconnection systems have resulted in inevitable challenges to PCB designers due to issues of PCB level signal integrity, power integrity and electromagnetic compatibility (EMC).

To prevent these issues from becoming more serious, appropriate process flow of PCB fabrication needs to be examined thoroughly. Several other aspects that affect the validity of output result on PCB fabrication are power consumption, PCB size and environment noise. Nowadays, PCB fabrication has improved in terms of its level modelling, design and measurement especially in relation to signal integrity and power integrity.

In line with the improvement of PCB fabrication in electronic industry, real study and knowledge about PCB fabrication are important. In order to fabricate PCB, there will be problems such as the size of component's pin hole is varied according to its type. Grounding issues are also critical. The purpose of this project is to analyze issues that lead to the failure of PCB functionality such as errors due to component partitioning, interconnecting traces and finally come out with the solution and step to overcome the problems.

#### 1.3 Objective of the Research

The main objectives of the research are:-

- To understand the process flow of PCB

- To acquire knowledge about PCB fabrication

- To apply high frequency DC-DC Converter on PCB fabrication

- To test and verify the output of PCB fabrication

#### 1.4 Relevancy of the Research

The research is very relevant to the scope of undergraduate level. This is to make sure that the knowledge about the process flow of fabricating Printed Circuit Board (PCB) is captured. The project will be focusing on implementing high frequency DC-DC Converter circuit on PCB. While conducting this project, knowledge and experience can be obtained regarding the process flow of PCB fabrication, the relevancy of IC and electronic components on the PCB boards and external factors that will affect the validation of output.

Furthermore, Electrical & Electronic Department provides the facilities to fabricate the PCB in the lab. Some of the components and IC that will be used are also available in EE store.

#### 1.5 Challenges

The main challenge for this project is conducting literature review regarding PCB because a lot of ideas and opinion from the previous research need to be considered. A lot of information from the thesis and journal results in confusion. Another challenge is to select the suitable type of component in order to obtain the optimum result. Time constraints are also one of the limitations to complete this project. The duration given to complete this project is about eight months.

#### **1.6 Significance of Project**

Significance of the project is in terms of verifying simulation circuit with fabrication of PCB. Circuit simulation is done using the Eagles Software. Gebber file obtained from the circuit simulation is used for PCB fabrication. With this representation of the circuit to the physical form on PC, performance of the Synchronous DC/DC Converter in terms of total gate drive loss, body diode conduction loss and switching power loss can be examined physically. The benefit obtained from the representation of the circuit simulation to the physical form on PCB board is in form of testing that conducted manually. This method also required knowledge about fabricating PCB.

#### **1.7 Contribution of Work**

Before fabricating on PCB, testing of electrical component and circuit need to be done on the breadboard which requires a lot of wire connections and consequently percentage of error is high. PCB fabrication improves the circuit design by minimizing the loss, making the circuit more organized and resulting in more accurate and precise output. Since the fabrication of PCB is regarding the Synchronous DC/DC Converter, the project will contribute to analysis of total gate drive loss, body diode and conduction loss and switching loss.

### **CHAPTER 2: LITERATURE REVIEW**

Chapter 2 comprises of literature review which was conducted in order to gather information and knowledge about PCB fabrication. The process flow and fabrication design of PCB are reviewed in this section. In addition, the study of DC-DC converter is also included in this chapter. The sequence of the literature review was based on the priority of the objective stated in Chapter 1.

#### 2.1 Printed Circuit Board (PCB)

Research regarding PCB fabrication can be divided into three main areas: process modeling, board design and PCB testing. Process modeling develops a model to predict the relevancy and compatibility of the model on the PCB. Board design empirically predicts the manufacturing yield by looking at the design parameters and characteristics of the PCB. PCB testing relates closely between the estimation of model on simulation and the percentage of faults.

Thermal management is a serious problem for electronic component especially in PCB fabrication. PCB board that experiences thermal problem will have high percentage of faults. Solution is introduced regarding how to solve the thermal problem on PCB construction. Small piece of metal coin is embedded inside PCB under the high power components [1]. The coins inserted are small and can be electrically connected to the ground of PCB layer. Instead of using coin, metal and copper can also be used but under the consideration of electrical grounding.

#### 2.1.1 PCB Manufacturing Process

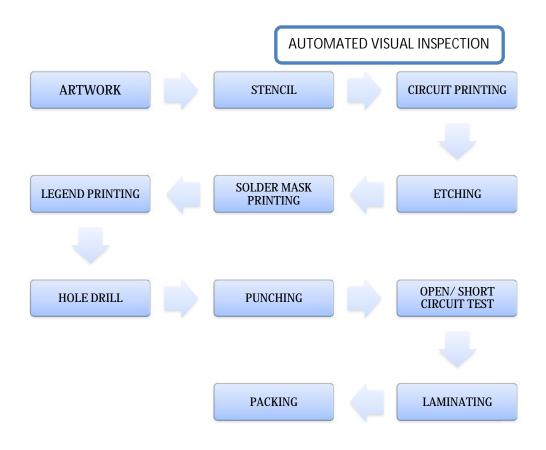

Figure 3: Fabrication Flow Chart for Single-sided PCB

Figure 3 shows the flowchart for fabrication of single-sided PCB. In the etching process, ferric chloride is used. The process of PCB fabrication needs to be done in sequential order to avoid any mistake that will affect the accuracy of the output.

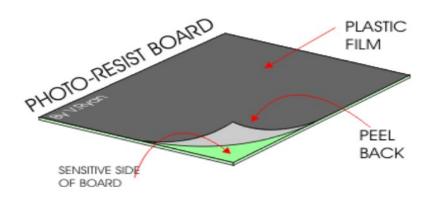

Photo-resist board that is a piece of glass reinforces plastic is used to fabricate PCB. Photo- resist board is used because UV light is exposed for several minutes to the board [2].

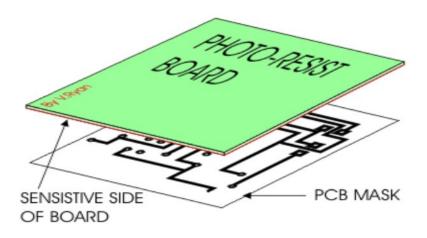

Figure 4: Photo-Resist Board [3]

Figure 4 shows photo-resist board that used in PCB manufacturing. This board comprises of copper clad (sensitive side of board) that has a photosensitive coating. When the plastic film is peeled back, sensitive coating is revealed.

Figure 5: PCB Mask + Photo-Resist Board [3]

Figure 5 is the illustration of combining PCB mask underneath the photoresist board. This procedure is significant and needs to ensure PCB mask is in the right way with the photo-resist board. If PCB mask is slightly misplaced, the tracks of the circuit will be in incorrect way.

#### 2.2 Partitioning of the PCB layouts

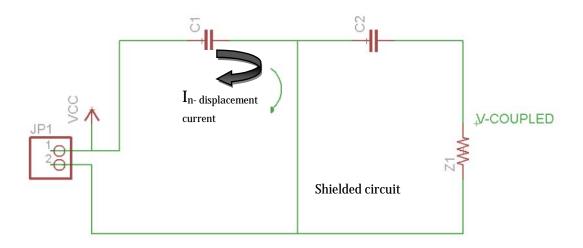

Circuits layouts that operate at high frequency will normally experience crosstalk. Crosstalk will occur when different signals interfere with each other. The best partitioning of the PCB layout can be such that all signal conductors must be in parallel position [5, 6]. This is to avoid signal conductors from contacting the ground pins and therefore create a Faraday shield. Faraday shield is a set of parallel wires that are attached to a common conductor at one end. Faraday shield prevents interference from other electrical waves from interfering with the flow of power within the enclosure [7].

Figure 6: An operational model of Faraday shield

Figure 6 shows the operational model of Faraday Shield. Faraday shield helps block the electric field between the source,  $V_{cc}$  and shielded circuit. It must also be connected so that the displacement current returns to  $V_{cc}$  without flowing in any part of the circuit.

Multiple ground pins will help maintain ground in position which is at the junction between the board and the backplane. Contact resistance used is in the range of 10 m $\Omega$  [6, 7]. To ensure the efficiency of the PCB, ground pins connection should be in range of 30 % to 40 % distance to the PCB connector pins [6, 8].

#### 2.3 Grounding Schemes of PCB

Grounding is important because it acts as a reference to the circuit which signal is based. Improper grounding application can affect the accuracy of the circuit. Spurious ground and backward signal voltage have to be grounded properly. To overcome this problem and improve grounding quality, ground planes are introduced [7].

The PCB is made of copper metal so that the ground planes are applied on the PCB. Low resistance can be obtained when large amount of metal is used. This will minimize spurious ground difference voltages across the conducting planes. However, while injecting high currents into a ground plane, precaution step should be considered as voltage drops will be produced and interfered with sensitive circuitry [7, 8].

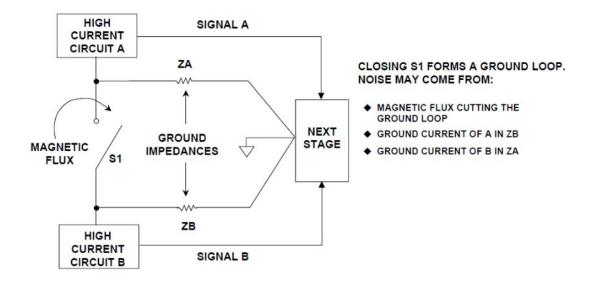

Grounding pattern is important to minimize the ground impedance and potential ground loops from circuit to the power supply. Ground loop occurs when two components are connected to ground through more than one path.

Figure 7: Ground Loop [7]

Figure 7 shows the example of ground loop. Closing of S1 will result in ground loop to occur because magnetic flux will present and cut the ground loop.

Guard ring is introduced to prevent the backward flow of return current. Guard ring acts like a field fringing sink and is placed around the edge of power plane [8].

Figure 8: Layout of Guard Ring [8]

Figure 8 shows the layout of guard ring. Tracks for the component used are grounded following guard ring layout. Usually, no currents are present in the grounded track.

For the connector grounding on the PCB, it is necessary to connect all connectors to the PCB ground. Connector pin that is not grounded will cause impedance mismatch and will lead to signal oscillations. Mismatch will result in current circulating and bouncing through the conductor [9]. This will affect the performance of the system as the signal cannot be controlled according to the desired condition.

Installing decoupling capacitor on the PCB is important because it will smoothed out the oscillation of voltage from power supply to the IC. However, decoupling capacitor should be grounded perfectly to avoid any voltage drop and signal mismatch. Decoupling capacitor should be placed between the supply pin and ground plane.

Figure 9: Decoupling capacitor [9]

Figure 9 shows the example of decoupling capacitor arrangement. Yellow colour indicates the decoupling capacitor.

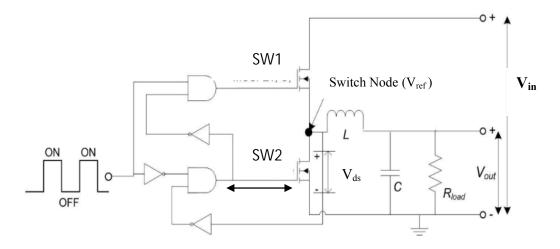

# 2.4 Synchronous Rectifier Buck Converter (SRBC)

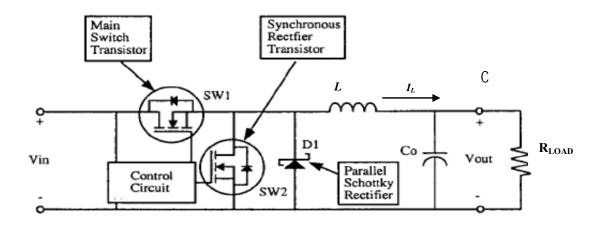

SRBC is the modified version of the buck converter circuit by replacing the diode, in the buck converter with a second switch, SW2 as illustrated in Fig 10. This will improve the efficiency of the SRBC compared to conventional buck converter. SRBC will allow bi-directional power flow and efficiency is increased by minimizing the voltage drop at the SW2 compared to the forward voltage of diode.

Figure 10: Synchronous Rectifier Buck Converter Circuit [10]

SW2 is added to replace diode used in conventional buck converter. This adjustment is the transaction between the increased cost and better efficiency of the converter. SW2 allows bidirectional power flow to the circuit [11]. Furthermore, it is essential to ensure both SW1 and SW2 do not turn on at the same time [12]. To prevent this circumstance from happening, adequate delay is added [13].

Formula used to calculate total power loss in the switch: [10, 11, 13]

$$P_{sw(total)} = P_{sw(on)} + P_{sw(off)} + P_{sw(cond)+} P_{sw(gate)}$$

(1)

Where

$P_{sw(total)}$  = total power loss in the switch  $P_{sw(on)}$  =power loss in the switch when switch is on  $P_{sw(off)}$  = power loss in the switch when switch is off  $P_{sw(cond)}$  = power loss in the switch when switch is conducted  $P_{sw(gate)}$  = power loss in the switch at the gate Formula used to calculate total gate drive loss in the switch: [10, 11, 13]

$$P_{gate(t)} = P_{gate(SW1)} + P_{gate(SW2)}$$

(2)

Where

$P_{gate(t)}$  = total gate drive loss in the switch

$P_{gate(SW1)}$  = total gate drive loss at SW1 which is main switch transistor in the buck converter

$P_{gate(SW2)}$  = total gate drive loss at *SW2* which is synchronous rectifier transistor.

Formula used to calculate power dissipation: [10, 11, 13]

$$P_{d(on)} \quad \frac{1}{2} \times C_{diode} \times V_{DC}^{2} \times f_{s} \tag{3}$$

Where

$P_{d(on)=}$  Power dissipation in diode  $C_{diode}=$  Capacitance of diode during reverse bias

Formula used to calculate body diode conduction loss in the switch: [10, 11, 13]

$$P_{SW1(cond)} = (I_L)^2 R_{DS(on)SW1} . D$$

(4)

Where D = Duty ratio of SW1 $I_L = Current at inductor$

$$P_{SW2(cond)} = (I_L)^2 R_{DS(on)SW2} . (1 - D)$$

(5)

Where

D =Duty ratio of SW2  $I_L =$ Current at inductor

Formulas used to calculate total power loss, total gate drive loss and body diode conduction loss are important. The results are analyzed and compared between SRBC-PWM and SRBC-Compensator-Adaptive.

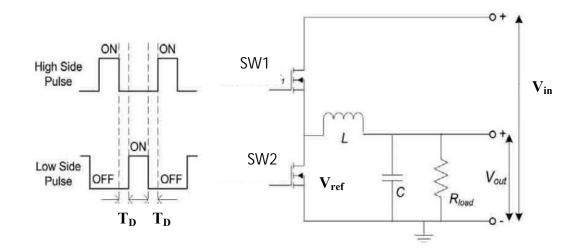

Figure 11 shows the application of Pulse Width Modulator (PWM) signal in Synchronous Buck converter circuit.

Figure 11: Synchronous Switching using PWM [14]

Figure 11 shows those two pulses: High side and Low side pulses are applied respectively to drive SW1 and SW2. This is important to avoid both of the MOSFETS to turn on at the same time.  $T_D$  is defined as the dead time or in simple word known as delay when turn on and turn-off of the switch occurs.

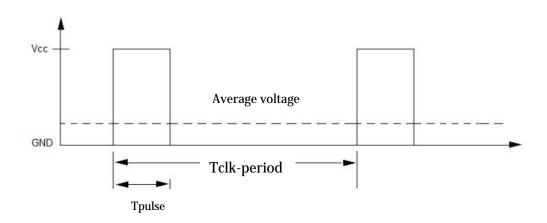

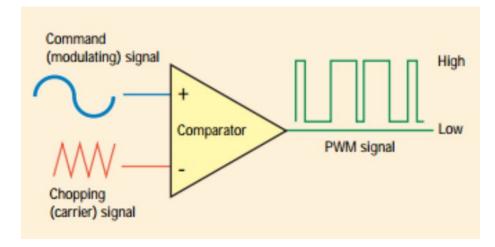

#### 2.5 Pulse Width Modulation

PWM technique is used to drive MOSFET to the ON or OFF position. PWM is operated by comparing the output voltage of the SRBC,  $V_{out}$  with the  $V_{ref}$  (desired voltage supplied to the system) of PWM. Figure 12 shows the example of PWM signal.

Figure 12: Example of PWM signal

Duty cycle of PWM is referred to percentage of the pulse period that is the amount of time in the period when the pulse is high. Duty cycle of the PWM can be calculated using formula (6)

Formula to calculate duty cycle [15]

Duty Cycle =

$$\binom{Tpulse}{Tclk\_period} \times 100\%$$

(6)

Average Voltage =

$$Duty \ cycle \times V_{CC}$$

(7)

From the eq. (6), *Tpulse* is greater when the percentage of Duty Cycle is increased.

Figure 13: The generation of PWM signal [16].

Figure 13 shows the process of generation PWM signal by comparing the carrier signal with the modulating signal which is the output voltage from the SRBC at the comparator. The output of the comparator which is the PWM signal will be generated and the signal will be in digital signal.

\

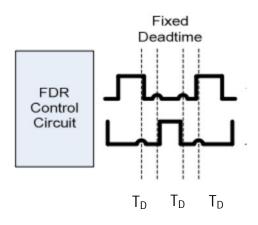

#### 2.6 Adaptive Gate Drive

Adaptive Gate Drive (AGD) is the improvement of the driver to overcome the limitation of Fixed Duty Ratio (FDR) [15, 16]. The limitation of FDR is that the pulse dead time,  $T_D$  is longer to prevent cross conduction from occurring. Longer  $T_D$  will allow body diode of the switch to conduct. Longer  $T_D$  will introduce losses due to body diode conduction [17]. Body diode conduction occurs when one switch is turned on and the other switch is turned off, energy is transferred to the load. When  $T_D$  is applied, delay exists between turn on and turn off of the switch.  $T_D$  signal is shown in Figure 14

Figure 14: FDR control signal [16]

Figure 14 shows FDR control signal.  $T_D$  affects the signal system.

From Fig 15, control loop which includes a digital delay line will detect the drain to source voltage,  $V_{ds}$  of the SW2 and will compare the digital delay line based on the amount of delay should be applied to turned on the SW2 [14, 16] Every controller has its own advantages and weaknesses. AGD can reduce the dead time,  $T_D$  and make it compatible with the component used so that electronic component won't be damaged. However, weakness of AGD is in terms of body diode conduction time due to the logic components that function as feedback. AGD circuit is shown in Figure 15

Figure 15: Digital Delay Line for AGD control circuit [18]

The main components of the AGD circuit are AND, NOT and OR logic gates. Input is directly taken from switch node and will be compared with the  $V_{ref.}$  Adjustment of delay for AGD is made adaptively because AGD uses control loop that detect  $V_{ds}$  and only turns on the SW2 when switch node is equal to zero. Output from AGD will directly feed to SW2 gate terminal.

## **CHAPTER 3: METHODOLOGY**

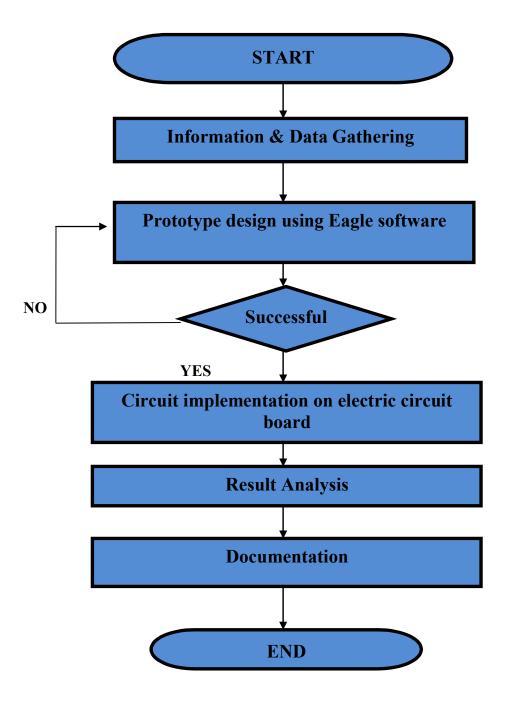

#### **3.1 Project Flow**

A good project planning would lead to a success of a project. As illustrated in Figure 16, the project is systematically planned to meet with the specific timeline.

Figure 16: Flowchart of the Project

#### 3.1.1 Information & Data Gathering

Literature review was conducted to study about PCB fabrication and the problems on PCB fabrication process. Controller designs were analyzed based on function, advantages, disadvantages and operation of controller. Literature review was conducted by referring to journal and conference papers. Comparison between results is done and the best criteria, solution and disadvantages of PCB fabrication are examined.

#### 3.1.2 Prototype Design using Eagle Software

From the literature review, the best design of controller and type of component used are chosen. The circuit was simulated in the Eagle Software so that the clear view of the schematic can be analyzed. By using Eagle software, the schematic circuits are converted to the board as a representation of PCB and circuit is analyzed with regards to its connection and size of pin hole. The important step of using the software is the exact type of component has to be chosen because this will affect the on foot print of PCB.

#### 3.1.3 Circuit Implementation on Electric Circuit Board

Circuit testing is done on the board in order to make sure circuit is working and the suitable type of component is chosen. In case the circuit is not working and the result obtained is not satisfactory, the process is repeated and the circuit is simulated again.

#### 3.1.4 Result Analysis

When the circuit successfully works on the board, the project continues with implementing the circuit on PCB. When the fabrication of PCB is successfully done, the output of the project will be analyzed in terms of total gate drive loss, body diode conduction loss and switching power loss.

#### **3.1.5 Documentation**

The documentation compilation is the final stage where all research work, methods and outcome of the projects will be documented. This is important so that the progress of the project is monitored and recorded and also to make sure it is completed on schedule.

## 3.2 Gantt Chart

# Table 1: Project Gantt Chart and Key Milestone

| No | Detail / Week FYP I                     | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|----|-----------------------------------------|---|---|---|---|---|---|---|---|---|

| 1  | Selection of Project Topic              |   |   |   |   |   |   |   |   |   |

| 2  | Literature Review                       |   |   |   |   |   |   |   |   |   |

| 3  | Submission of Extended Proposal Defence |   |   |   |   |   |   |   |   |   |

| 4  | Proposal Defence                        |   |   |   |   |   |   |   |   |   |

| 5  | Project work on PCB                     |   |   |   |   |   |   |   |   |   |

| 6  | Submission of Interim Draft Report      |   |   |   |   |   |   |   |   |   |

| 7  | Submission of Interim Report            |   |   |   |   |   |   |   |   |   |

| No | Detail / Week FYP II                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|----|--------------------------------------|---|---|---|---|---|---|---|---|---|

| 1  | EAGLE software design                |   |   |   |   |   |   |   |   |   |

| 2  | Component selection                  |   |   |   |   |   |   |   |   |   |

| 3  | Submission of Progress Report        |   |   |   |   |   |   |   |   |   |

| 4  | Functionality Test of circuit        |   |   |   |   |   |   |   |   |   |

| 5  | Fabrication of PCB                   |   |   |   |   |   |   |   |   |   |

| 6  | Draft Report                         |   |   |   |   |   |   |   |   |   |

| 7  | Submission and Completion of Project |   |   |   |   |   |   |   |   |   |

Table 1 show the planning for the project and the current progress is at week 14 of FYP II where the submission and completion of project is under assessment.

#### 3.3 Software and Tool Required

Since the project is focusing on the fabrication of PCB. The software used to transfer the circuit into the compatible circuit on PCB board is Eagle Software. The experimentation part of the PCB fabrication will involve a lot of circuit testing. The tools required for experimentation are ammeter, oscilloscope and power supply.

| Table 2 | : Details | about Eagle | Software |

|---------|-----------|-------------|----------|

|         |           |             |          |

| Name      | EAGLE                 |

|-----------|-----------------------|

| Version   | 5.2.0                 |

| Build     | 105                   |

| Developer | Cadsoft Design System |

Table 2 shows the details about Eagle Software. Version of the software is 5.2.0 and developed by Cadsoft Design System.

#### 3.4 Process flow of PCB

Process flow of PCB fabrication is one of the objectives for this project. Knowledge regarding PCB design flow process was obtained from the journal, thesis and books. There are many steps of PCB design flow processes. Basically, process flow of PCB consists of eleven steps which are

- Artwork

- Circuit Printing

- Solder Mask Printing

- Hole Drill

- Open/Short Circuit Test

- Packing

- Stencil

- Etching

- Legend Printing

- Punching

- Laminating

However, in this project the main step is artwork. Creating PCB artwork is the initial process in PCB fabrication. There are five rules to follow while creating PCB artwork. They are:

a) Creating schematic diagram using Eagle Software

Schematic diagram of SRBC and Adaptive Gate Drive and schematic diagram of SRBC and PWM are created using Eagle software. This step is also known as designing PCB layout. Suitable component is chosen based on the function and application of the component on PCB. During this stage of artwork, component footprints need to be placed in order to comply with the size of PCB.

b) Defining the layer of PCB

PCB is divided into three types which are single layer, double layer and multilayer PCB. However, under the scope of research, PCB type that are fabricate are single-sided PCB.

#### c) Defining route rule

Routing rule needs to be determined and Eagle software will produce an artwork which is easily transferable on to PCB.

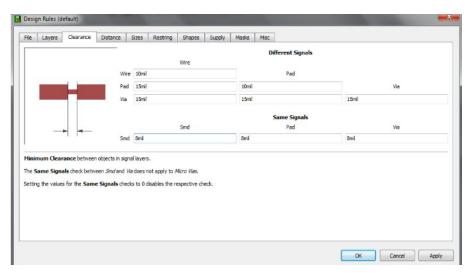

Figure 17: Routing Rules of PCB

Figure 17 shows routing rules of PCB. Sizes of clearance cannot be too small because it will cause problems of broken tracks or tracks shorting during the transfer process. The value of clearances should be as close as possible to the value stated in Figure 17. As stated in Figure 17, the clearance for wire, pad and via for different signal and same signals are tabulated in Table 3 and Table 4, respectively.

#### Table 3: Differential Signals Clearance

|      | WIRE   | PAD    | VIA    |

|------|--------|--------|--------|

| WIRE | 10 mil |        |        |

| PAD  | 15 mil | 10 mil |        |

| VIA  | 15 mil | 15 mil | 15 mil |

Table 4: Same Signals Clearance

|     | SMD   | PAD   | VIA   |

|-----|-------|-------|-------|

| SMD | 8 mil | 8 mil | 8 mil |

d) Auto-routing

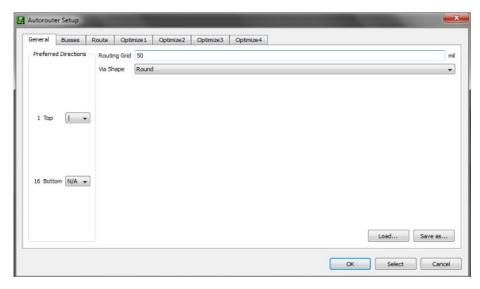

Auto routing will route the tracks for the components. However, auto routing will not be able to route and clean up all redundant tracks. Redundant tracks need to be cleared up manually and this will take some time in order to make the board looking orderly and less complicated.

Figure 18: Auto-routing of PCB

Figure 18 shows the steps to auto route the PCB layout. For single sided PCB, only top layer will have the tracks where the bottom layer is used to solder the components on the PCB.

e) Printing the complete artwork

This is the last step of PCB artwork. To make sure all the settings and component placements are in the right order, layout of PCB is printed on A4 paper first. After all the settings and results are correct, PCB layout will be printed on transfer film. This completes the process of PCB artwork.

#### 3.5 Knowledge about PCB fabrication

Knowledge about PCB fabrication covers from artwork until the testing of PCB. The knowledge is very wide and a lot of knowledge can be acquired from this project. However, it is restricted to the most common issues that are discussed regarding PCB fabrication. Knowledge about PCB fabrication is acquired by using method of research, reviewing tutorial on PCB and asking information and knowledge from technician. The most important aspect is regarding the partitioning of the PCB layouts, grounding schemes, interconnecting traces and component placement.

Furthermore, it is crucial to know the exact technique on soldering the component. Soldering technique will affect the connectivity of the track. While soldering the component on the PCB board, it is important to ensure the current and voltage drop on the tracks for each component are in the percentage required. The percentage required is about 5 % more and less from the actual specification of the component as stated in electronic datasheet of the component [22].

#### 3.6 Applying High Frequency DC-DC Converter on PCB

In this project, AGD will be fabricated on PCB and will be compared with the conventional PWM.

Circuits that will be fabricated on PCB are:

- a) Synchronous Rectifier Buck Converter + Adaptive Gate Drive

- b) Synchronous Rectifier Buck Converter + Pulse Width Modulator

### 3.6.1 Adaptive Gate Drive Circuit

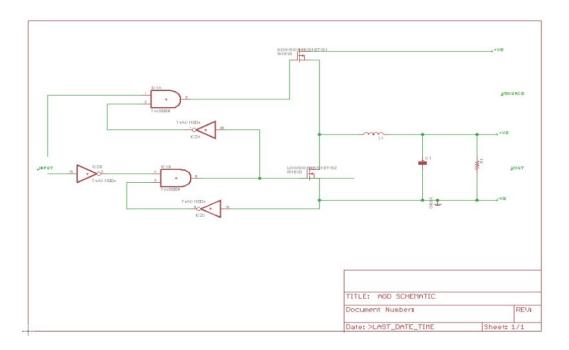

Figure 19: Adaptive Gate Drive Circuit

Figure 19 shows the schematic of the SRBC used in this project. This adaptive circuit diagram is simulated using Eagle Software. Type of component used is carefully chosen in order to obtain optimum output result. Furthermore, pin head of each component in the circuit should be in same size as the real components. This is to avoid any error and difficulties at the stage of soldering the components.

#### 3.6.2 SRBC with Compensator-AGD

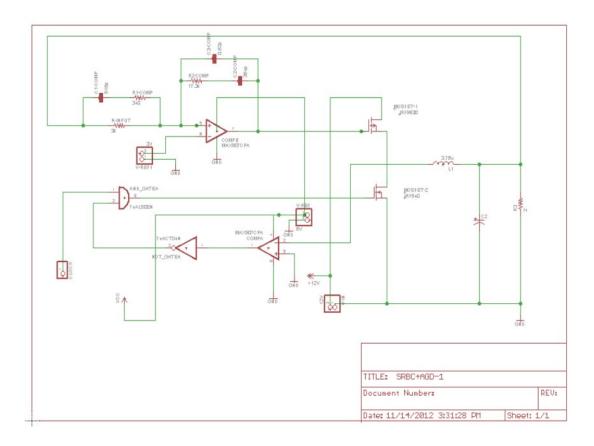

Figure 20: SRBC-Compensator-AGD schematic

Figure 20 shows the schematic for the SRBC with compensator and AGD. The circuit has three sources which are V-IN supplying 12V, V-REF supplying 5V and V-REF1 supplying 3V. Type of capacitors used in this schematic is electrolytic capacitors. Electrolytic capacitors are used in main application of supply voltage filtering. Electrolytic capacitors act as a filter to the circuit in order to convert DC output smoothly.

#### 3.6.3 SRBC with PWM

Figure 21: SRBC-PWM schematics

Figure 21 shows the schematic for SRBC with PWM that is used in this project. The type of PWM used is Low-Power BICMOS Current Mode PWM. Output of the PWM will cause switches M1 and M2 turn on alternately in order to allow current charging and discharging at the inductor, L1.

#### 3.7 Testing and Verifying the Output Results

After PCB is successfully fabricated, PCB is tested to obtain the results. It is taken for experimentation. The results are analyzed and verified to get the output ripple voltage,  $V_{op-p}$ , output ripple current,  $I_{op-p}$ , average output voltage,  $V_{o}$  (avg), average output current,  $I_{o}$  (avg) and body diode conduction loss,  $P_{bd}$ .

#### 3.7.1 Output Ripple Voltage

a) Equation used to calculate output ripple voltage is as Eq. (8)

$$V_{op-p} = \frac{\frac{v_{max} - v_{min}}{\frac{v_{max} + v_{min}}{2}} \times 100\%$$

(8)

#### **3.7.2 Output Ripple Current**

b) Equation used to calculate output ripple current is as Eq. (9)

$$I_{op-p} = \frac{I_{max} - I_{min}}{\frac{I_{max} + I_{min}}{2}} \times 100\%$$

(9)

#### 3.7.3 Average Output Voltage

c) Equation used to calculate average output voltage is as Eq. (10)

$$V_{avg} = \frac{v_{max} + v_{min}}{2} \tag{10}$$

#### 3.7.4 Average Output Current

d) Equation used to calculate average output current is as Eq. (11)

$$I_{avg} = \frac{i_{max} + i_{min}}{2} \tag{11}$$

### **3.8 Circuit Parameters**

| Components          | Parameter Settings in PSPICE simulator and Component used. |

|---------------------|------------------------------------------------------------|

| C <sub>1-COMP</sub> | 1.93 nF                                                    |

| C <sub>2-COMP</sub> | 1.63 pF                                                    |

| C <sub>3-COMP</sub> | 383.68 pF                                                  |

| R <sub>1-COMP</sub> | 34.62 k Ω                                                  |

| R <sub>2-COMP</sub> | 164.49 Ω                                                   |

| R <sub>-INPUT</sub> | 3 kΩ                                                       |

| Comp_A, Comp_B      | MAX942CPA/MXM                                              |

| Not_GateA           | 7404                                                       |

| And_GateA           | 7408                                                       |

| $V_{-REF}$          | 5 V                                                        |

| V <sub>-REF1</sub>  | 3 V                                                        |

| V <sub>-IN</sub>    | 12 V                                                       |

| $M_2$               | IRFP250                                                    |

| $M_{I}$             | IRFR9212                                                   |

| $R_3$               | 1 Ω                                                        |

| $L_l$               | 10 µH                                                      |

| $C_{I}$             | 0.375 μF                                                   |

Table 5: Simulation Parameters of SRBC with compensator-AGD [23]

Table 5 shows the simulation parameters used in experimentation for the SRBC with Compensator-AGD.

| Components            | Parameter Settings in PSPICE simulator and Component used.                       |

|-----------------------|----------------------------------------------------------------------------------|

| PWM <sub>1</sub>      | V1=0, V2=5V, $T_d$ = 0ns $T_r$ = 5ns, $T_f$ = 5ns, PW = 240ns, PER=<br>1000ns    |

| PWM <sub>2</sub>      | V1=0, V2=5V, $T_d$ = 265ns, $T_r$ = 5ns, $T_f$ = 5ns, PW = 710ns, PER=<br>1000ns |

| $V_{-IN}$             | 12 V                                                                             |

| <i>M</i> <sub>2</sub> | IRFP250                                                                          |

| <i>M</i> <sub>1</sub> | IRFR9212                                                                         |

| R <sub>1</sub>        | 1 Ω                                                                              |

| $L_{I}$               | 10 µH                                                                            |

| <i>C</i> <sub>1</sub> | 0.375 μF                                                                         |

Table 6: Simulation Parameters for SRBC [23]

Table 6 shows the parameters for SRBC for  $f_s$  of 500 kHz. These parameters are applied to the simulation in PSpice software and the experimentation of SRBC on PCB board.

### **CHAPTER 4: RESULTS AND DISCUSSION**

This project focuses on the process about PCB fabrication. However, in order to have knowledge regarding PCB fabrication, the analysis of gate drive control system for synchronous DC/DC converter which involved the application of SRBC and AGD circuit is also important. These two circuits: SRBC and AGD compensator circuit and SRBC with PWM compensator which are fabricated on PCB.

#### 4.1 PCB artwork

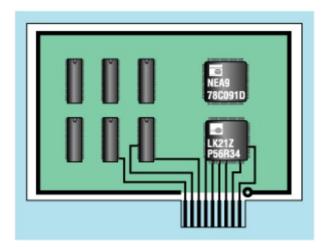

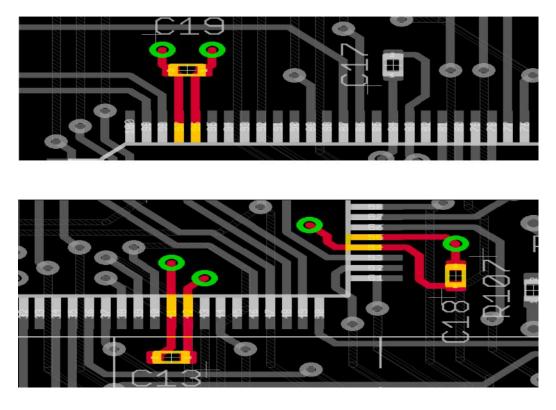

Figure 22: SRBC-Compensator - AGD PCB Layout

Figure 22 shows the SRBC with compensator and AGD PCB layout. As can be seen from the figure, tracks between each component are successfully printed. Based on the previous research, nets distance should be keeping as short as possible because longer total track length will cause increase in resistance, capacitance and inductance of the PCB. As for the PCB design in Figure 22, the complete auto-routers achieved are 88.4 %. Instead of using auto-route, manual route is also done in order to ensure the copper track flow between each of component is smooth and not crossing and interfering with each other.

Figure 23: SRBC-PWM Layout

Figure 23 shows the SRBC with PWM PCB layout. Another rule routing is that the tracks on the PCB layout should have angles of 45 degrees. In order to produce professional and efficient appearance, PCB components should be rotated in 90 degree movement and the tracking degree should have angles of 45 degrees. However, based on Figure 23, the tracking degree is not fixed to 45 degrees due to some error during the component placement. The errors are corrected by manual route the tracking degree. As can be seen from the Figure 23, copper track is smoothly routed according to the pin configuration and circuit design. PCB design for SRBC with PWM circuit is fully completed with the percentage of routers between each component is 100 %. This completes the process of artwork in PCB. PCB layout for SRBC with compensator and AGD and also PCB layout SRBC with PWM are reviewed in order to make the board look efficient and reduce error to the minimum level at the stage of fabrication PCB. Complete PCB layout will be printed on the thin films and this process finally completed the first objective of the project.

#### 4.2 Grounding & Component

The knowledge about PCB fabrication especially about the grounding and component placement are very crucial in order to complete this project and obtain the best PCB design. While drawing the schematic of circuit, grounding of the components is located separately from each other. However, after converting the circuit to board design, each component shares common ground. Common grounding problem causes component placement process on the board is messy. This problem was solved by running separate ground paths for critical part of the circuit such as the circuit for SRBC with compensator and AGD.

Component placement is made up of 90 % to the PCB design. This is one of the important steps that need to be considered in creating PCB layout. The basic rule that helps simplify large and complex signal and gives the best electrical performance is by placing and routing each critical component separately. As in Figure 22, the critical component that affects the PCB routing is N-channel MOSFET and IC gate since they have a lot of input and output. The best solution to this problem is by separately routing the N-channel MOSFET and IC gate and moving the completed routing component to the best position on the PCB. Based on the discussion earlier, this completes the objective two of the project that is to acquire knowledge about PCB fabrication.

#### 4.3 Circuit Results

Objective three of the project is to apply high frequency DC-DC converter on PCB fabrication which has been achieved by fabricating SRBC and AGD circuit on PCB. The comparison between SRBC with PWM and SRBC with Compensator and AGD circuit will be analysed and verified. This will complete objective four of the project.

The results obtained are average output voltage and current for SRBC with compensator and AGD improved from average output voltage and current for SRBC with PWM. Output ripple voltage and current for SRBC with Compensator and AGD should also be higher compared to SRBC with PWM. In terms of body diode conduction loss, the loss for SRBC with compensator and AGD is reduced and this concludes that body diode conduction loss for SRBC with Compensator with AGD is better compared to SRBC with PWM.

#### 4.3.1 SRBC

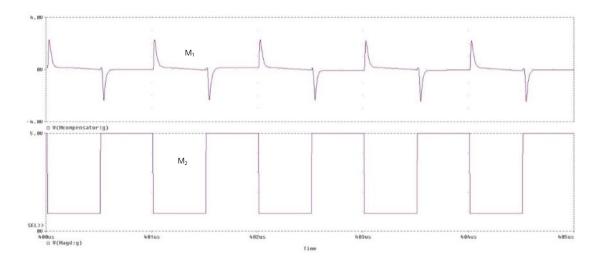

Figure 24: PWM of SRBC

Figure 24 shows the PWM of the SRBC. The switches  $M_1$  and  $M_2$  turn on alternately to avoid cross conduction of current in the switches allow the current charging and discharging at the inductor.

### 4.3.2 SRBC-Compensator-AGD

Figure 25: PWM of SRBC-Compensator-AGD

Figure 25 shows the PWM of the SRBC with Compensator and AGD. The switches alternately turn on and turn off.

The results that need to be analyzed are the output voltage and node voltage for both of the circuits. However, based on the result obtained previously, it can be concluded that SRBC with compensator and AGD control circuit is improved than the conventional SRBC.

#### 4.4 Comparison between Simulation and Experimentation Result

Comparison between simulation and experimentation result will be done by measuring the percentage difference of the outputs. The desired percentage difference is around 5% difference.

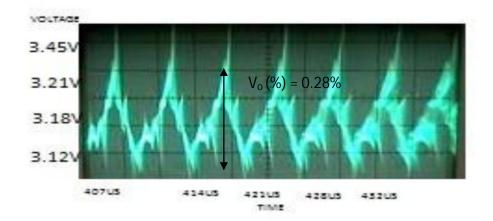

4.4.1 Output Voltage (V<sub>0</sub>)

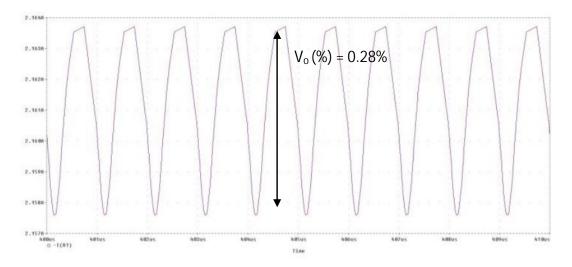

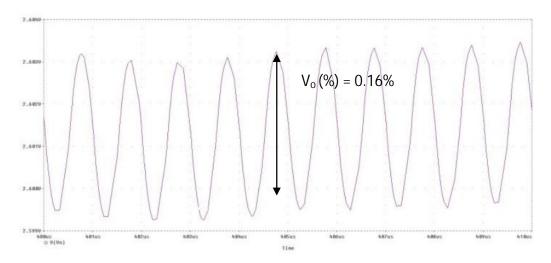

Figure 26: Output Voltage for SRBC-PWM (simulation)

Figure 27: Output Voltage for SRBC-Compensator-AGD (simulation)

Figure 26 and 27 show the simulation results of output voltage for SRBC-PWM and SRBC-compensator-AGD. The desired output voltage for SRBC-PWM is 2.16 V and for the SRBC-compensator-AGD is 2.60 V. However, the output voltage for the experimentation result shows in detail in Figure 28 and Figure 29.

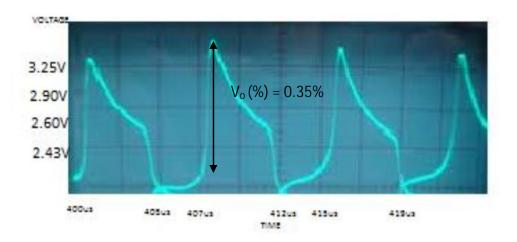

Figure 28: Output Voltage for SRBC-PWM (experimentation)

Figure 29: Output Voltage for SRBC-Compensator-AGD (experimentation)

Figure 28 and Figure 29 show the experimentation results of output voltage for SRBC-PWM and SRBC-compensator-AGD. The average voltages that obtained for both of the circuit design are slightly higher compared to the simulation result. The percentage difference between simulation result and experimentation result should be in the range below 5%. The difference level between experimentation and simulation occurs because of design parameters value of the component used between simulation value and experimental value.

#### 4.4.2 Node voltage, (V<sub>node</sub>)

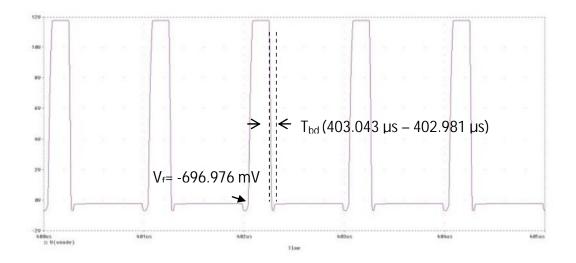

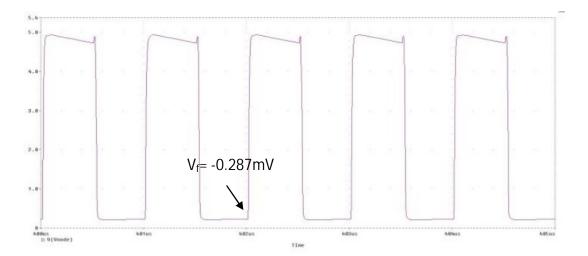

Figure 30: Node Voltage from SRBC-PWM (simulation)

Figure 31: Node Voltage from SRBC-Compensator-AGD (simulation)

Figure 30 and Figure 31 show the node voltages from both of the circuit design. The waveform obtained from the simulation shows that forward voltage ( $V_f$ ) is present for SRBC-PWM is large value compared to SRBC-compensator-AGD circuit. This difference concludes that body diode conduction loss for SRBC-PWM is higher compared to SRBC-compensator-AGD circuit. However, the actual result is calculated based on the experimentation shown in Figure 32.

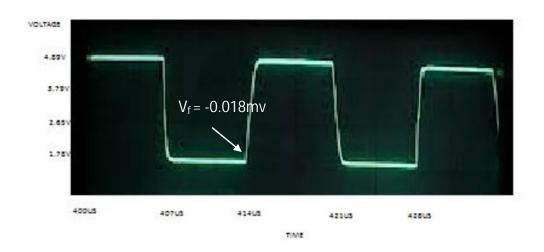

Figure 32: Node Voltage from SRBC-Compensator-AGD (experimentation)

Figure 32 shows the actual value of forward voltage for SRBC-compensator-AGD circuit. The forward voltage is slightly lower compared to the simulation value. The experimentation result is proven to be more accurate and precise compared to the simulation result because lower forward voltage obtained will reduce body diode conduction loss,  $P_{bd}$  and increase the efficiency of the circuit.

#### 4.4.3 Comparison of results

|                                                          | Simulation | Experiment | % Δ    |

|----------------------------------------------------------|------------|------------|--------|

| V <sub>o</sub> SRBC-PWM (V <sub>o</sub> )                | 0.28       | 0.35       | 25%    |

| V <sub>0</sub> SRBC-COMPENSATOR-AGD<br>(V <sub>0</sub> ) | 0.16       | 0.28       | 75%    |

| V <sub>f</sub> SRBC-PWM (mV)                             | -696.976   | -485.67    | 30.31% |

| V <sub>f</sub> SRBC-COMPENSATOR-AGD<br>(mV)              | -0.287     | -0.018     | 93.73% |

| Table 7: Comparison | between Simula | tion and Expe | rimentation result |

|---------------------|----------------|---------------|--------------------|

|                     |                |               |                    |

Table 7 shows the tabulated comparison between SRBC-PWM and SRBCcompensator-AGD. Based on the table, the percentage difference is slightly higher. This is due to the high tolerance and noise occurs while validating the result. However, even though the percentage difference is higher, it does not affect the conclusion for this project which is the efficiency and operation of SRBC with compensator and AGD control circuit is better compared to the conventional SRBC.

#### **CHAPTER 5: CONCLUSION**

The project of experimental analysis of gate drive control system for synchronous DC/DC converter has provided knowledge about PCB fabrication and the performance study of the AGD converter. The objectives of project which are to understand the process flow of PCB, acquire knowledge about PCB fabrication, applying high frequency DC-DC converter on PCB fabrication and lastly test and verified the accuracy output of PCB fabrication. Along the project, the problems include the selection of suitable ICs components. ICs components such as capacitors are selected based on the types whether electrolytic or non-electrolytic, resistance to heat and size of components used.

#### 5.1 Significance and Contribution of Work

The significance of the project is in terms of verifying simulation circuit with fabrication of PCB. The result from the simulation and experimentation is compared and the best controller is concluded. Project is also significant in order to analyze the best controller circuit of DC-DC Converter. Furthermore, based on the objective stated, the contribution of project is achieved in terms of minimizing the loss and transforming the circuit to more organized circuit layout. Finally, the contribution of project is achieved that the best controller is proven to be compensator-AGD.

#### REFERENCES

- Chien-Cheng Lee, Wu-Yung Chen, "Coin Insertion Technology for PCB Thermal Solution", in IEEE International Conference, vol4 pp 1-2, April 2007

- [2] Photolithography and Photoresist retrieved from http://pcbhowto.com/pcbhowto-photoresist.php at 10.05 on 21st October 2012

- [3] Manufacture of Printed Circuit Board, retrieved from <u>http://www.technologystudent.com/pcb/PCB3A.htm</u> at 11.08 on 14 December 2012.

- [4] Moldovan,H, Marius.M "PCB Testing Using Infrared Thermal Signatures", *IEEE, Instrumentation and Measurement Technology Conference*, Ottawa Canada vol3 pp 1970-1974, 17-19 May 2005.

- [5] Xin He, "Principal Component Analysis-Based Compensation for Measurement Errors Due to Mechanical Misalignments in PCB testing", *in test conference (ITC)*, pp. 1-10, 2010

- [6] Hroundas, G.," Economics of bare printed circuit board testing", *Circuit World*, 1986, Vol. 12, No. 2, p. 31-34.

- [7] Rahman.S, "Automatic Search for Break Points in Printed Circuit Board using Intelligent Visual System Based on DSP Algorithms", *Research Journal on Algoritms*, pp. 9-10.

- [8] D.L Jones, "Printed Circuit Board (PCB) Design Tutorial, *pdf*, revision A, pp 1-25, June 2004

- [9] Printed Circuit Board (PCB) Design Issues, "Partitioning", Research Journal on PCB Partitioning Method, No. 12 pp123

- [10] Printed Circuit Board (PCB) Design Issues, "Grounding Issues", Research Journal on PCB Partitioning Method, No. 12 pp125

- [11] Martin O.Hara, "Grounding Strategies for PCB", Research Journal on Grounding Techniques, Vol. 2, pp 15

- [12] D. Hirschmann, S. Richter, C. Dick and R.W. De Doncker "Unified Control Strategy Covering CCM and DCM for a Synchronous Buck Converter" in *IEEE 22<sup>nd</sup> Annu. Appl. Power Electron. Conf.*, 2007, pp. 489-494.

- [13] S. Y. Liang, H. S. Chu & K. C. Hung, "Circuit and Method for Predicting Dead Time", U. S. Patent 7053632B1, May 2006.

- [14] "A Soft-Switching Synchronous Buck Converter for Zero Voltage Switching (ZVS) in Light and Full Load Conditions" in *IEEE App. Power Electron. and Expo.*, Feb. 2008, pp. 1460-1464.

- [15] Naeem.A, "PCB Grounding Techniques", Research Journal, pp 27

- [16] Scott Deuty, "Optimizing Transistor Performance in Synchronous Rectifier, Buck Converter", *Application Specialist on Semiconductor*, pp 676-678, 23-25 May 2008.

- [17] B. Ramachandran & D. Maksimovic, "Dynamic Operation of Sensorless Dead – Time Optimization in Digitally Controlled DC – DC Converters", in *CoPEC Ann. Meeting*, Nov. 9, 2006, pp. 1 – 15.

- [18] Robert Selders, "Pulse Width Modulation", *in article of Silicon Blue*, pp 1-2, March 2008.

- [19] N.Z Yahaya, K.M Begam, M.Awan, K.M Zaini," A New Approach Of Simple Predictive Control Scheme in High Frequency Gate Driver Design" in IEEE International Conference: Electrical Energy and Industrial Electronic Systems EEIES,2009.

- [20] MIT, fab.cba.mit.edu/classes/MIT/961.04/topics/pwm.pdf, retrieved on November 5<sup>th</sup> 2012.

- [21] Taeyoung Ahn, Heejun Kim, Koosuke Ham, "Fixed Frequency, Fixed Duty Ratio Controlled Forward ZVS-MRC Using a Saturable Core" IEEE 7<sup>th</sup> International Conference on Power and Energy, pp 551-557

- [22] DM 7408 Quad 2-input AND Gates, 'Fair Child Semiconductor Datasheet', March 1998.

- [23] I.K. Suhaimi, "Comparative Study of Multiple Controller Design for High Frequency Converter", Bachelor of Engineering (Hons) Thesis, Universiti Teknologi Petronas, Malaysia 2011.

### **APPENDICES**

# **APPENDIX A**

# **DATASHEET OF COMPONENT**

# **APPENDIX B**

### REFERENCES

# APPENDIX C TECHNICAL PAPER

# **APPENDIX D**

### POSTER

# **APPENDIX E**

### **POWER POINT SLIDE**