## STATUS OF THESIS

address 14200 Sungai Jawi, Penang

Date: 24th Mary 04

| Title of thesis                       | Optimization of Rapid Ther<br>Poly Silicon Gate | rmal Processing in 0.13 micron CMOS                       |

|---------------------------------------|-------------------------------------------------|-----------------------------------------------------------|

| Universiti Teknolo                    | ogi PETRONAS (UTP) with the                     | ormation Resource Center (IRC) of e following conditions: |

| 1. The thesis bec                     | omes the property of UTP                        |                                                           |

| 2. The IRC of U                       | ΓP may make copies of the thesi                 | s for academic purposes only.                             |

| 3. This thesis is o                   | classified as                                   |                                                           |

| Confi                                 | dential                                         |                                                           |

| X Non-o                               | confidential                                    |                                                           |

| If this thesis is cor                 | nfidential, please state the reason             | 1:                                                        |

| The contents of the Remarks on disclo | e thesis will remain confidential               | for years.                                                |

|                                       |                                                 |                                                           |

| Endorsed by                           |                                                 |                                                           |

| - Just !                              |                                                 | Marfliohs.                                                |

| Signature of Author                   | or                                              | Signature of Supervisor                                   |

| Permanent: 1873 ]                     | <u> Kampung Lima Kongsi,</u>                    | Name of Supervisor                                        |

Assoc Prof. Dr Norani Muti Mohamed

Date: W May 2004

Date :\_

### APPROVAL PAGE

#### UNIVERSITI TEKNOLOGI PETRONAS

Approval by Supervisor (s)

The undersigned certify that they have read, and recommend to The Postgraduate Studies Programme for acceptance, a thesis entitled "Optimization of Rapid Thermal Processing in 0.13 micron CMOS Poly-silicon Gates" submitted by (Chew Soon Aik) for the fulfilment of the requirements for the degree of masters of science in electrical and electronics engineering.

| 24th | May | 04 |

|------|-----|----|

| Date |     |    |

Main Supervisor

Date

Co-Supervisor 1

Date

Assoc. Prof. Dr Noraus Muli Mohamed

24th May 2004

all V. Karley

#### UNIVERSITI TEKNOLOGI PETRONAS

Optimization of Rapid Thermal Processing in 0.13 micron CMOS Poly Silicon Gate

Ву

Chew Soon Aik

#### A THESIS

# SUBMITTED TO THE POSTGRADUATE STUDIES PROGRAMME AS A REQUIREMENT FOR THE

## DEGREE OF MASTERS OF SCIENCE IN ELECTRICAL AND ELECTRONICS

#### **ENGINEERING**

Electrical and Electronics Engineering

BANDAR SERI ISKANDAR,

PERAK

MONTH NOVEMBER, 2003

## **DECLARATION**

I hereby declare that the thesis is based on my original work except for quotations and citations, which have been duly acknowledged. I also declare that it has not been previously or concurrently submitted for any other degree at UTP or other institutions.

| Signatu | re: | futile        |  |

|---------|-----|---------------|--|

| Name    | :   | Chew Soon Aik |  |

| Date    |     | Jefter may or |  |

#### ACKNOWLEDGEMENT

First of all, I would like to acknowledge my supervisor, Assoc Prof Dr. Norani Muti Mohamed. She has been a great mentor to me with her management skills and enthusiasm. She has also been an exceptional role model of life. She has done her utmost to help relieve concerns that her advisees have. It has been memorable in that she had encouraged and supported me to apply for Silterra Postgraduate Internship while I was in deep depression.

I also would like to thank my co-supervisor, Mr Albert Victor Kordesch, Senior Manager of Device Modeling Department, Silterra. Throughout my association with him, he gave me strong motivation in doing my research. I consider him to be a living encyclopedia that answers almost all my queries. Besides that, his encouragements also make me feel more comfortable and confidence while carrying out my research in Silterra.

I am indebted to the internal and external examiner who will be evaluating my thesis and oral exam. I am also grateful to Assoc Prof Ir. Dr.Ahmad Fadzil Mohamad Hani who has agreed to be the chairman of the UTP oral committee in spite of his busy schedule.

I wish to thank the Silterra (M) Sdn Bhd, pioneer of Malaysia semiconductor industry for the support of this work through postgraduate internship program. Silterra provides every technical support including financial, equipment, research environment and technical advice for my research work. I would like to acknowledge

the Device Modeling Dept (Mr. Yusman Mohd Yusof, Ms. Norhafizah Che May, Mr. Philip Tan, Mr. Gilbert See, Mr. Nor Razman Md Zin and Mr. Mohd Fahmi Muhsain), Mr. CO Lim, Mr. Anuar Fadzil Ahmad, Mr. Daniel Oh, Mr. Mohamad Zainizan Zakaria, Ms. Su-Ann Heng, and Mr. KJ Koh. Special appreciation also goes to Mr. Palanivel Balasubramaniam for his advice and approval, Dr HC How and Ms. PL Teh for SIMS profile measurements and FIB scanning, and Ms. KS Lim for her advice on process and procedure. Ms Lena Tan, Mrs. Reha and Mr. Abdullah bin Lin for the non-technical support in Silterra. Lastly, many thanks to Silterra management for their support on the managing of the postgraduate internship program.

#### ABSTRACT

Complementary Metal-Oxide-Silicon (CMOS) technology has gained a great deal of attention in the decade of VLSI (Very Large Scale Integration) in the 1980s. As the CMOS devices continue to scale down, many problems such as poly depletion effect, stress induced leakage current etc. have arised leading to the reduction in the device performance. The objective of this work is to reduce the poly depletion effect occurring in deep submicron CMOS devices and at the same time suppresses boron penetration through the thin gate oxide. The study focused on optimising the spike annealing process on nitrided gate oxide of the  $0.13-\mu m$  CMOS devices.

The work began with the simulation on the fabrication process of CMOS devices using different parameters of implant dosage, implant energy, implant angle and heat treatment. After successful simulated outcomes have been obtained, experiments were conducted based on the parameters used in the simulation work. The Source Drain Rapid Thermal processing (SD-RTP) using the spike annealing technique was adopted as the heat treatment process on the polysilicon layer. The samples were then characterized electrically using four-point probe and structurally using Secondary Ion Mass Spectrometry (SIMS) and Focused Ion Beam (FIB).

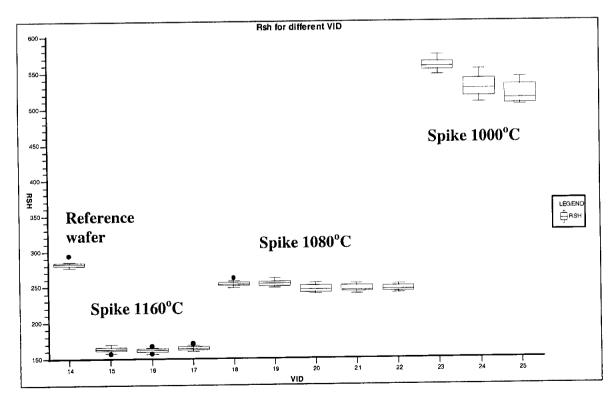

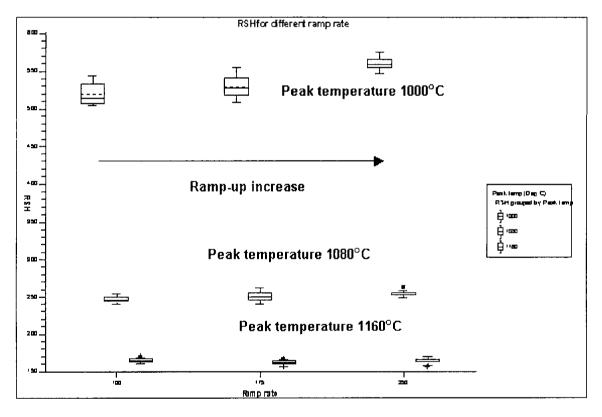

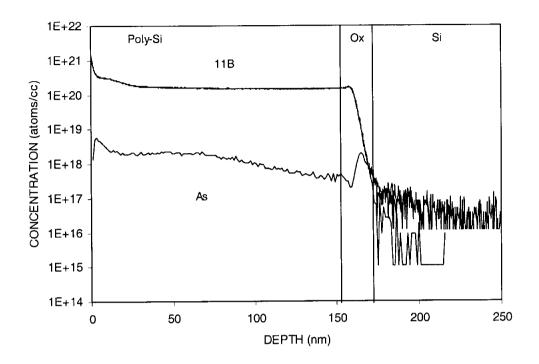

Results showed that peak temperature has a bigger influence in controlling the dopant activation in the poly gate compared to ramp-up rate. As evident in SIMS profile, boron concentration in the polysilicon that had been subjected to spike annealing at the peak temperature of 1080°C was found to be uniform. Uniform distribution of boron will reduce the poly depletion effect. FIB image showed that polysilicon treated to a higher peak temperature or longer annealing duration, has larger grain size. It is believed that with larger grain size, boron activation is increased due to the reduced ability to absorb interstitials. Moreover, dopant segregation at the grain boundaries is also decreased. As a conclusion for 0.13-µm CMOS devices, spike annealing at an optimum peak temperature of 1080°C is recommended to replace the existing RTP process to reduce the poly depletion effect and at the same time, suppressing the boron penetration.

#### ABSTRAK

Teknologi CMOS telah beroleh banyak perhatian pada dekad VLSI pada 1980an. Apabila saiz peranti CMOS semakin mengecil, banyak masalah seperti kesan susut poli, arus bocor terangsang dan lain-lain timbul menyebabkan penurunan dalam prestasi peranti. Objektif penyelidikan ini ialah untuk mengurangkan kesan susut poli yang berlaku dalam peranti submikron CMOS dan pada masa yang sama menahan penembusan boron melepasi get oksida yang nipis. Kajian memfokus kepada mengoptimumkan proses sepuhlindap puncak keatas oksida get nitrida bagi 0.13-μm peranti CMOS.

Penyelidikan bermula dengan simulasi keatas proses fabrikasi peranti CMOS dengan menggunakan parameter berbeza bagi dos penanaman, tenaga penanaman, dan sudut penanaman dan rawatan haba. Selepas berjaya memperolehi keputusan simulasi, eksperimen dijalankan berdasarkan kepada parameter yang digunakan dalam kerja simulasi. Pemprosesan terma kejut sumber parit (SD-RTP) dengan teknik sepuhlindap puncak digunakan sebagai rawatan haba keatas lapisan polisilikon. Sampel kemudiannya dicirikan secara elektrik dengan penduga-empat-titik dan secara struktur dengan spektrometer jisim ion sekunder (SIMS) dan bim ion fokus (FIB).

Keputusan menunjukkan bahawa suhu puncak mempunyai pengaruh yang lebih besar keatas pengaktifan pendop dalam get poli berbanding dengan kadar kenaikan sepuhlindap. Terbukti dalam profil SIMS, kepekatan boron dalam polisilikon yang dikenakan sepuhlindap pada suhu 1080°C telah didapati seragam. Taburan boron yang seragam akan mengurangkan kesan susutan poli. Imej FIB menunjukan bahawa polisilikon yang dirawat pada suhu puncak yang lebih tinggi dan tempoh sepuhlindap yang lebih lama, mempunyai saiz butiran yang lebih besar. Dipercayai bahawa dengan saiz butiran yang lebih besar, pengaktifan boron meningkat disebabkan oleh penurunan keupayaan untuk resapan pendop secara selitan. Tambahan pula, pengasingan pendop di sempadan butiran akan turut berkurang. Sebagai kesimpulan untuk peranti CMOS 0.13-μm, sepuhlindah kejut pada suhu puncak optimum 1080°C dicadangkan untuk mengganti proses RTP yang tersedia bagi mengurangkan kesan susutan poli dan pada masa yang sama, menahan penembusan boron.

## TABLE OF CONTENT

| STAT         | US OF T         | `HESIS                                           | i           |

|--------------|-----------------|--------------------------------------------------|-------------|

| APPR         | OVAL P          | AGE                                              | ii          |

|              |                 |                                                  |             |

|              |                 | ON                                               |             |

|              |                 | DGEMENT                                          |             |

|              |                 |                                                  |             |

|              |                 |                                                  |             |

|              |                 | ONTENT                                           |             |

|              |                 | LES                                              |             |

|              |                 | JRES                                             |             |

| LIGI         | <i>J</i> 1 1100 | 'ICLO                                            |             |

| СНАР         | TFR 1·I         | IINTRODUCTION                                    | 1           |

| 1.1          |                 | ound of CMOS Devices                             |             |

| 1.2          |                 | ive                                              |             |

| 1.3          |                 | of the Work                                      |             |

| 1.4          |                 | zation of the Thesis                             |             |

|              |                 |                                                  |             |

| CHAP         | TER 2: I        | BACKGROUND AND LITERATURE REVIEW                 | <i>J</i> 10 |

| 2.1          | Gate Po         | oly Depletion and Boron Penetration              | 10          |

| 2.2          | Method          | Is Attempted by Other Researchers                | 15          |

|              |                 |                                                  |             |

|              |                 | THEORY OF PROCESSES AND                          |             |

| CHAR         |                 | IZATION TECHNIQUES                               |             |

| 3.1          | Process         | ses                                              |             |

|              | 3.1.1           |                                                  |             |

|              |                 | .1.1 Oxide Growth Kinetics                       |             |

|              |                 | 1.1.2 Oxidation Reactor                          |             |

|              | 3.1.2           | Chemical Vapour Deposition (CVD)                 |             |

|              |                 | .2.1                                             |             |

|              |                 | lysilicon Deposition Mechanism                   |             |

|              |                 | 1.2.2 LPCVD Furnace                              |             |

|              | 3.1.3           | Ion Implantation                                 |             |

|              | 3.1.4           | 1.3.1 Ion Implanter                              |             |

|              |                 | 1.4.1 Infinite-source Diffusion (Pre-deposition) |             |

|              |                 | 1.4.2 Limited-source Diffusion (Drive-in)        |             |

|              |                 | 1.4.3 Diffusion Mechanism                        |             |

|              |                 | 1.4.4 Diffusion in Polysilicon                   |             |

|              |                 | 1.4.5 Annealing Profile                          |             |

| 3.2          |                 | terization Techniques                            |             |

| ~ · <b>-</b> | 3.2.1           | Four-Point Probe                                 |             |

|              | 3.2.2           | Secondary Ion Mass Spectrometry                  |             |

|              | 3.2.3           | Focused Ion Beam                                 |             |

| CHAP  | TER 4: 1 | METODOLOGY PROCEDURES           | 44  |

|-------|----------|---------------------------------|-----|

| 4.1   | Simula   | ation                           | 44  |

|       | 4.1.1    | Process Simulation              | 44  |

| 4.2   | Experi   | ment                            |     |

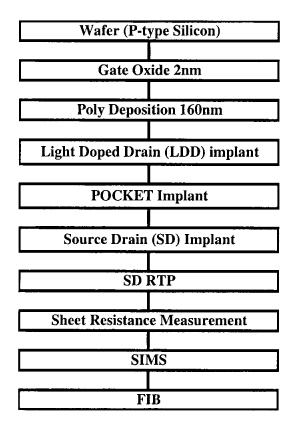

|       | 4.2.1    | Process Flow of The Experiment  | 47  |

|       | 4.2.2    | Wafer                           | 47  |

|       | 4.2.3    | Gate Oxide Growth               | 48  |

|       | 4.2.4    | Polysilicon Deposition          |     |

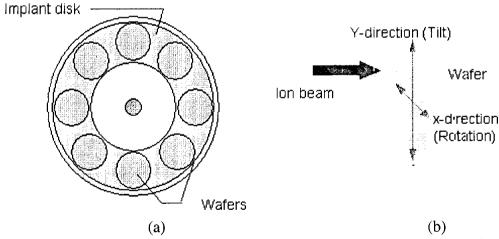

|       | 4.2.5    | Ion Implantation                | 49  |

|       | 4.2.6    | Rapid Thermal Processing        | 51  |

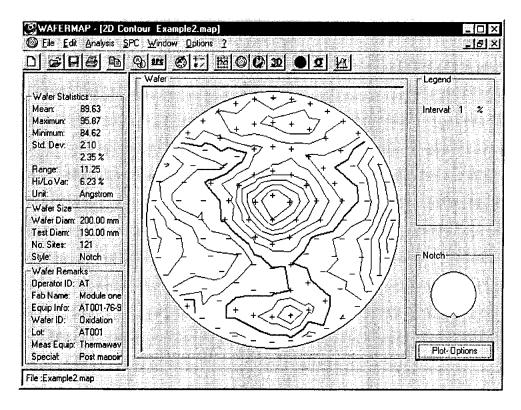

|       | 4.2.7    | Sheet Resistance Measurement    | 53  |

|       | 4.2.8    | Secondary Ion Mass Spectrometry |     |

|       | 4.2.9    | Focused Ion Beam                | 54  |

| СНАР  | TFR 5    | RESULT AND DISCUSSION           | 56  |

| 5.1   |          | ation result                    |     |

| 5.1   | 5.1.1    | NMOS Simulation                 |     |

|       | 5.1.2    | PMOS Simulation                 |     |

| 5.2   |          | imental Result                  |     |

| 3,4   | 5.2.1    | Sheet Resistance                |     |

|       | 5.2.2    |                                 |     |

|       | 5.2.3    |                                 |     |

| 5.3   |          | rial Verification               |     |

| СНАР  | TER 6.   | SUMMARY, CONCLUSION AND         |     |

|       |          | DATION                          | 76  |

| 6.1   |          | pary                            |     |

| 6.2   |          | usion                           |     |

| 6.3   |          | nmendation                      |     |

| 0.5   | Recon    | imendation                      |     |

| BIBLI | OGRAF    | PHY                             | 81  |

| PUBL  | ICATIO   | NS                              | 88  |

| APPE  | NDIX A   | <b></b>                         | 89  |

|       |          |                                 | 90  |

| A DDC | NINV D   |                                 | Q() |

## LIST OF TABLES

| <b>Table 3.1.</b> | List of dopants commonly used in semiconductor doping         | 30 |

|-------------------|---------------------------------------------------------------|----|

| <b>Table 4.1.</b> | Implantation recipe used in the simulation                    | 46 |

| <b>Table 4.2.</b> | Spike annealing process recipe.                               |    |

| Table 5.1.        | Sheet resistance mean value for different wafer with differen |    |

|                   | anneal split.                                                 | 67 |

## LIST OF FIGURES

| Figure 1.1.  | Simple CMOS device cross-sectional view1                                                                       |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Figure 1.2.  | An example of simulation window of TSUPREM45                                                                   |

| Figure 1.3.  | An example of finer grid for the model6                                                                        |

| Figure 1.4.  | An example of process editing in implantation step6                                                            |

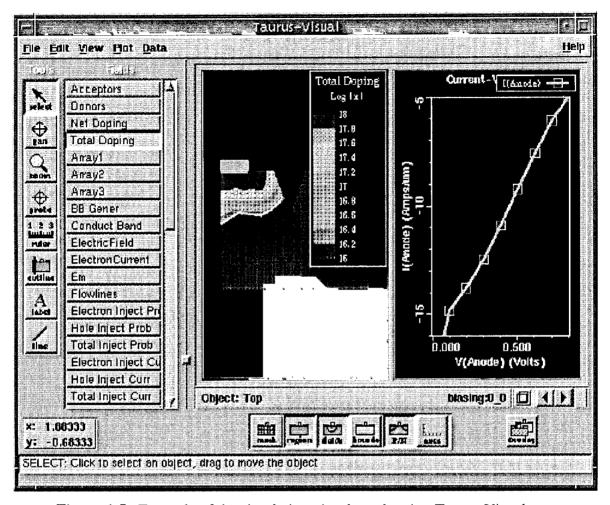

|              | Example of the simulation visual result using Taurus Visual7                                                   |

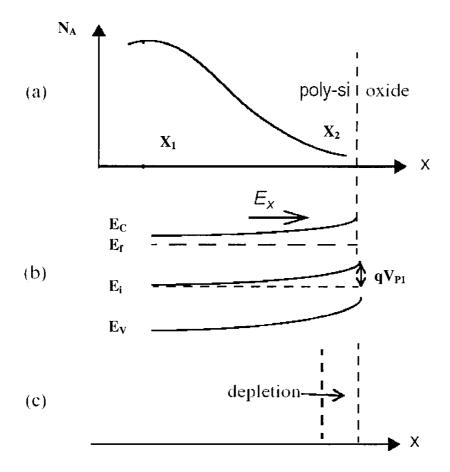

| Figure 2.1.  | Band diagram of a poysilicon-gate depleted N-channel MOS capacitor                                             |

|              | (Reproduced from Choi Changhoon, 2002)10                                                                       |

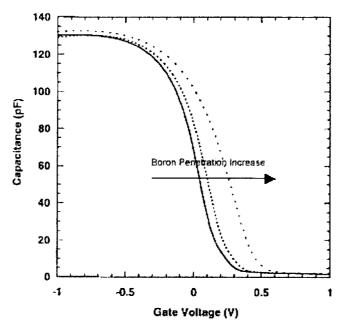

| Figure 2.2.  | C-V curves of N-channel MOS capacitors in the presence of polysilicon                                          |

|              | depletion effects. (Reproduced from Choi Changhoon, 2002)11                                                    |

| Figure 2.3.  | Potential distribution of MOS from the top of the poly-gate to the silicon                                     |

|              | substrate considering poly-depletion effects. (Reproduced from Choi                                            |

|              | Changhoon, 2002)12                                                                                             |

| Figure 2.4.  | Non-uniform, graded impurity distribution and corresponding energy-                                            |

|              | band diagram (Reproduced from Choi Changhoon, 2002)13                                                          |

| Figure 2.5.  | High-frequency C-V curves of a MOS Capacitor for different boron                                               |

|              | penetration level. (Reproduced from Cao Min et. al, 1998)                                                      |

| Figure 3.1.  | Oxidation process on silicon                                                                                   |

| Figure 3.2.  | Deal/grow model for oxidation                                                                                  |

| Figure 3.3.  | Simple diagram of oxidation reactor                                                                            |

| Figure 3.4.  | LPCVD Furnace for polysilicon deposition                                                                       |

| Figure 3.5.  | Atoms bonding diagram for an undoped silicon crystal30                                                         |

| Figure 3.6.  | N-type dopant in the silicon crystal causes an excessive electron in the                                       |

| E: 35        | lattices                                                                                                       |

| _            | P-type dopant in the silicon crystal cause a hole in the lattice                                               |

| Figure 3.8.  | Basic diagram of ion implanter. (Reproduced from Silterra, 2000)32                                             |

| Figure 3.9.  | Direct diffusion mechanism within crystal targets. The diffuser can travel exclusively on interstitial sites35 |

| Figure 2 10  | Dopant diffusion by vacancy mechanism                                                                          |

|              | Dopant diffusion via a substitutional-interstitialcy interchange37                                             |

| Figure 3.11. | Three-dimensional perspective drawing of a grain/grain boundary                                                |

| rigure 3.12. | network. (Reproduced from Puchner, 1996)39                                                                     |

| Figure 3.13. | Spike annealing profile                                                                                        |

|              | Four-point probe schematic diagram41                                                                           |

| Figure 3.15. | Extraction of dopant profile from the bombardment of ions                                                      |

| Figure 4.1.  | Process flow of the experiment47                                                                               |

| Figure 4.2.  | (a) Implant disc for ion implant tools. (b) Tilt and rotation angle for ion                                    |

| J            | implantation50                                                                                                 |

| Figure 4.3.  | CDE ResMap four-point probe machine53                                                                          |

| Figure 4.4.  | ResMap contour map after the sheet resistance measurement54                                                    |

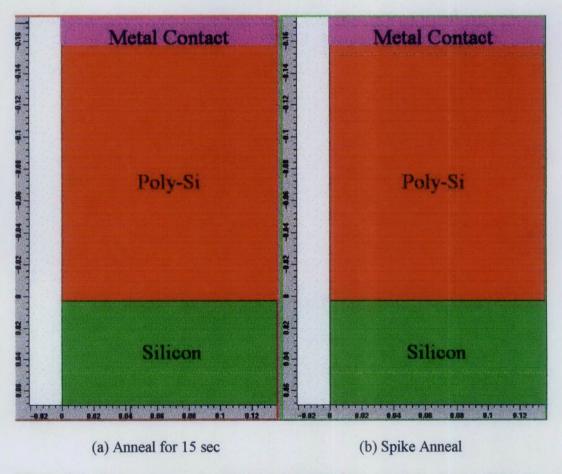

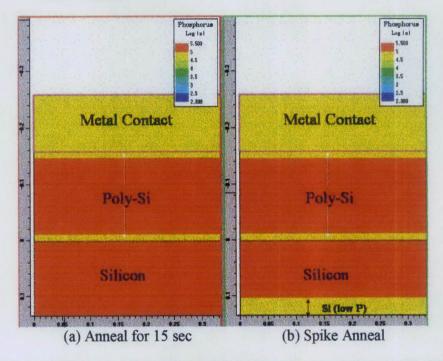

| Figure 5.1.  | Device cross-sectional view of NMOS from simulation for (a) RTP and                                            |

|              | (b) spike anneal57                                                                                             |

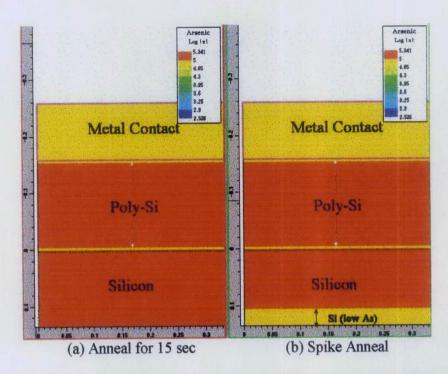

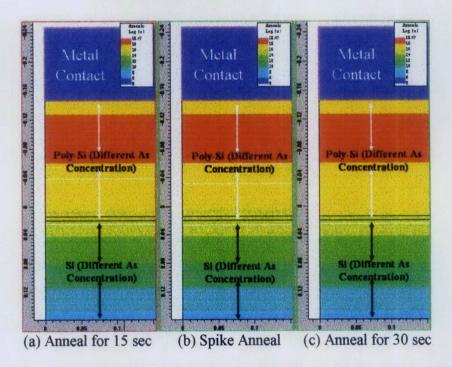

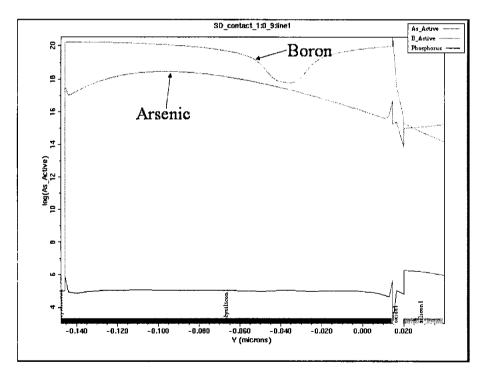

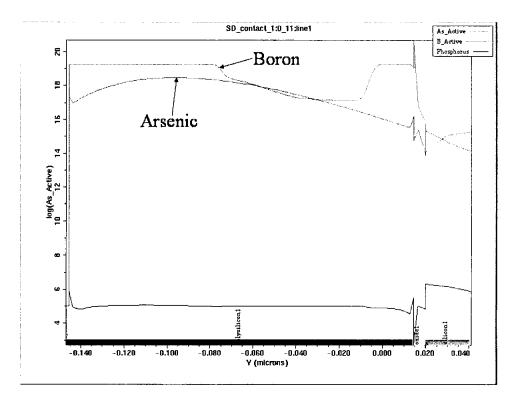

| Figure 5.2.  | Distribution of arsenic in N-polysilicon for (a) Anneal for 15 sec and (b)                                     |

|              | Spike Anneal                                                                                                   |

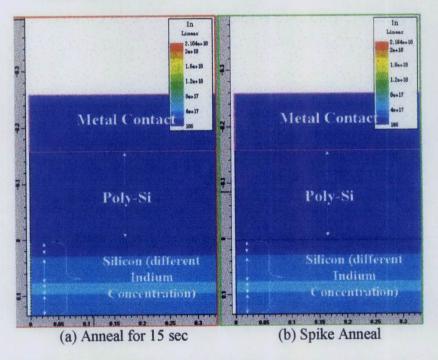

| Figure 5.3.  | Distribution of indium in N-polysilicon for (a) Anneal for 15 sec and (b)                                      |

|              | Spike Anneal                                                                                                   |

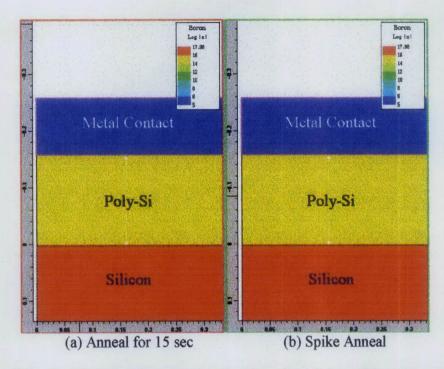

| Figure 5.4.  | Distribution of boron in N-polysilicon for (a) Anneal for 15 sec and (b)                                       |

|              | Spike Anneal59                                                                                                 |

| Figure 5.5.     | Distribution of phosphorus in N-polysilicon for (a) Anneal for 15 sec       |

|-----------------|-----------------------------------------------------------------------------|

| T: 5.           | and (b) Spike Anneal                                                        |

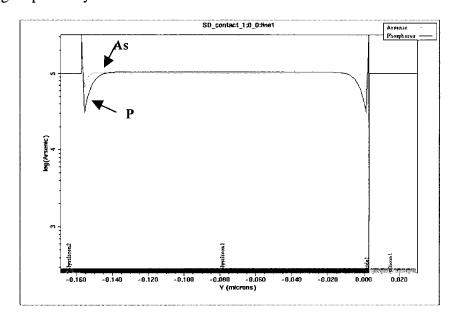

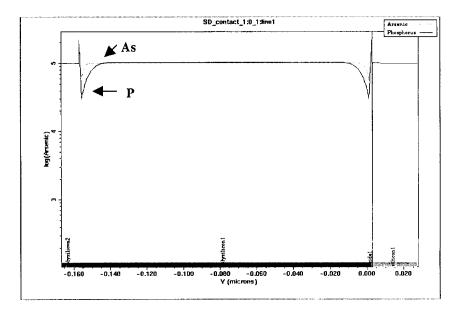

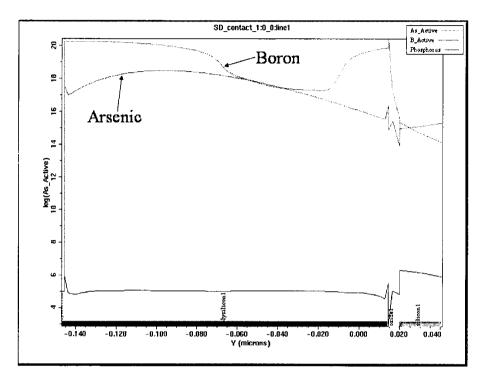

| Figure 5.6.     | A plot of dopant concentration versus depth for NMOS after standard         |

|                 | RTP60                                                                       |

| Figure 5.7.     | <u> </u>                                                                    |

|                 | annealing60                                                                 |

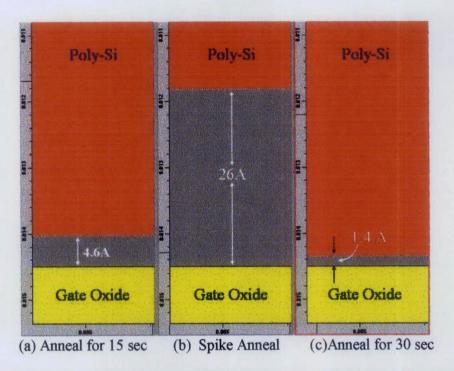

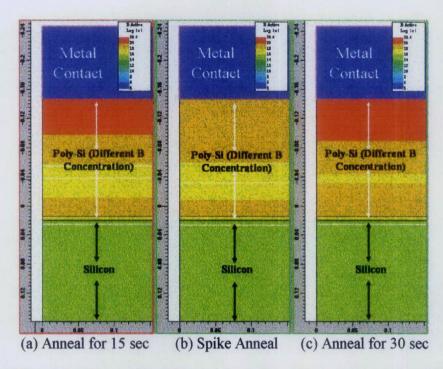

| Figure 5.8.     | Cross-sectional view of PMOS for (a) standard RTP for 15 seconds, (b)       |

|                 | spike annealing and (c) standard RTP for 30 seconds62                       |

| Figure 5.9.     | Distribution of Arsenic in the P-polysilicon for (a) Anneal for 15 sec, (b) |

|                 | Spike Anneal and (c) Anneal for 30 sec62                                    |

| Figure 5.10.    | Distribution of boron in the P-polysilicon for (a) Anneal for 15 sec, (b)   |

| _               | Spike Anneal and (c) Anneal for 30 sec63                                    |

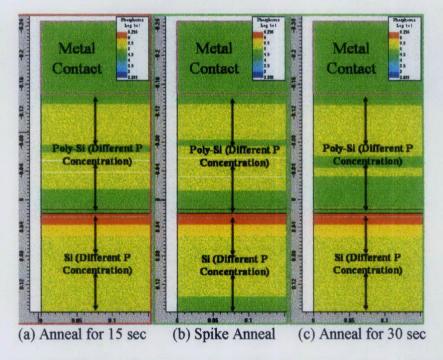

| Figure 5.11.    | Distribution of phosphorus in the P-polysilicon for (a) Anneal for 15 sec,  |

|                 | (b) Spike Anneal and (c) Anneal for 30 sec63                                |

| Figure 5.12.    | A plot of dopant concentration versus depth for PMOS after standard         |

| 8               | RTP for 15 seconds65                                                        |

| Figure 5.13.    | A plot of dopant concentration versus depth for PMOS after standard         |

|                 | RTP 30 seconds.                                                             |

| Figure 5.14.    | A plot of dopant concentration versus depth for PMOS after spike            |

| - 180-10 012 11 | annealing                                                                   |

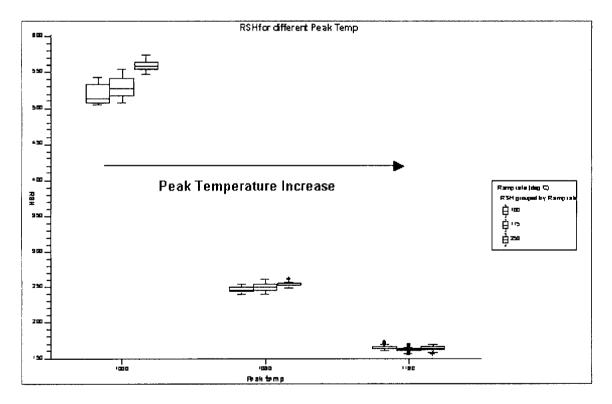

| Figure 5.15.    | Box plot of sheet resistance for different wafer (VID)68                    |

|                 | A plot of $R_S$ against ramp-up rate for different peak temperature69       |

|                 | A plot of $R_S$ against peak temperature for different ramp-up rate70       |

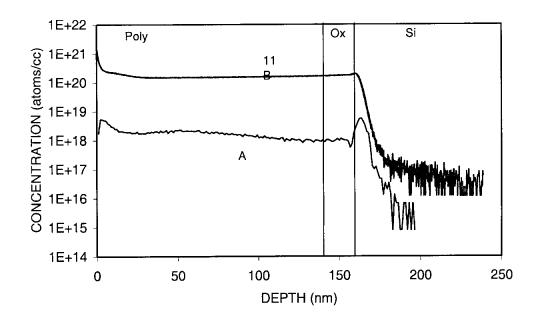

|                 | SIMS for boron and arsenic (from Pocket implant) in polysilicon after       |

| rigure 5.10.    | Standard RTP at 1000°C for 15 seconds                                       |

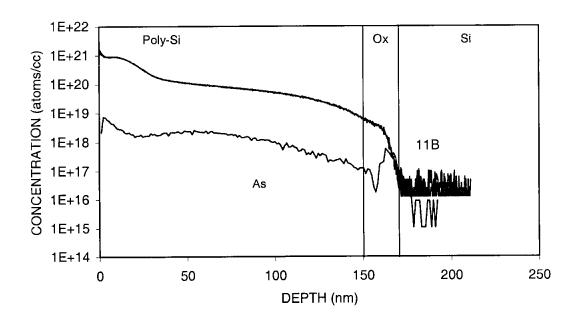

| Figure 5 10     | SIMS for boron and arsenic (from Pocket implant) in polysilicon after       |

| riguit 5.17.    | spike annealing at peak temperature 1000°C71                                |

| Figure 5 20     | SIMS for boron and arsenic (from Pocket implant) in polysilicon after       |

| rigure 5.20.    | spike annealing at peak temperature 1080°C                                  |

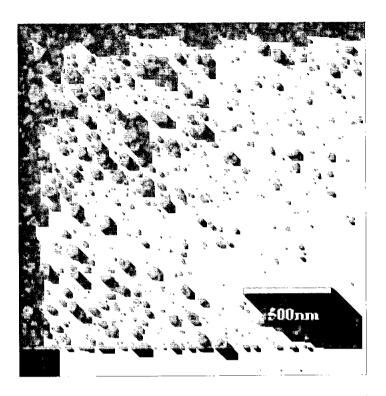

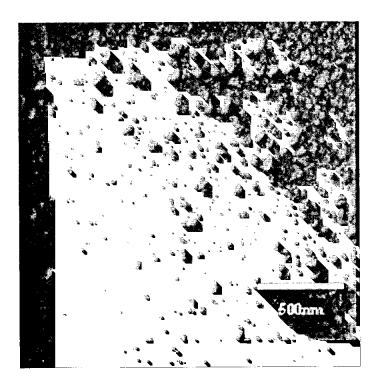

| Figure 5 21     | FIB image of polysilicon grain size after standard RTP for 15 seconds at    |

| riguie 3.21.    |                                                                             |

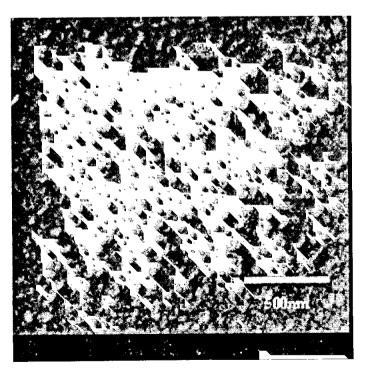

| Figure 5 22     | 1000°C. d <sub>grain</sub> =113.5 nm                                        |

| r igure 5.23.   | FIB image of polysilicon grain size after spike anneal at peak              |

| E: 5.24         | temperature 1080 °C. d <sub>grain</sub> =106.42 nm                          |

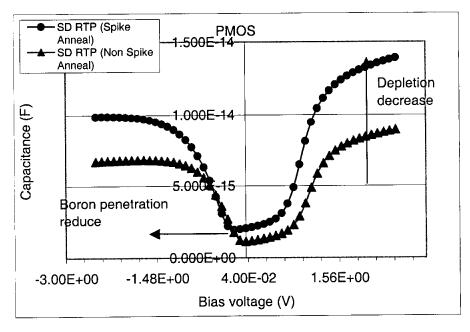

| Figure 5.24.    | Comparison C-V curves between reference wafer (Non spike annealing)         |

|                 | and wafer spike annealing at peak temperature 1080°C74                      |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background of CMOS Devices

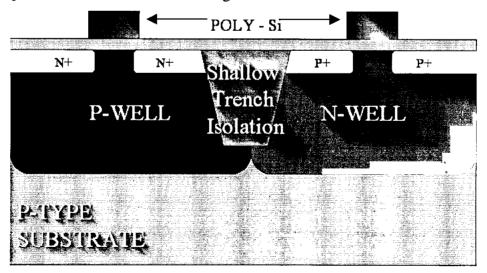

Complementary Metal-Oxide-Silicon (hereafter abbreviated as CMOS) technology has acquired a tremendous amount of interest in the decade of Very Large Scaled Integration (hereafter abbreviated as VLSI) in the 1980s. The great interest is because CMOS, when compared with N-type MOSFET (hereafter abbreviated as NMOS), has much lower power, comparable speed, slightly poorer density but better reliability. The major advantage of using CMOS is the low power dissipation. In a VLSI circuit, too many devices exist and they run very fast. As a result, more power is dissipated from each device and even more power is dissipated from a chip. Current packaging technology limits power dissipation at a few watts per chip to avoid high temperature induced reliability problems. Sophisticated packages are being developed, but at a great expense. Even CMOS, with its inherent low power characteristics is now pushing the limits of thermal packaging (Kamins, 1998). The cross-sectional view of the simple CMOS device is shown in Figure 1.1.

**Figure 1.1.** Simple CMOS device cross-sectional view.

In the early development, most gate electrodes for MOS were made from aluminum, which was deposited after the source, and drain regions were doped. However, in this case aluminum gate must overlap the source and drain region by at least one alignment tolerance. This can cause a significant Miller feedback capacitance between the gate and the drain resulting in a reduction in the circuit speed. The Miller effect is a way of dealing with a situation where the voltages at both ends of a capacitor change at the same time, either independently or dependently. In certain circuits, instead of taking into account what actually happens with the voltage, it is equivalent Polysilicon gates have much smaller Miller effect to having a larger capacitor. because the source and drain are self-aligned. So, polysilicon is used only after the Chemical Vapor Deposition (hereafter abbreviated as CVD) method has been developed. The ability of polysilicon to be oxidized and its compatibility with further high-temperature processing has allowed development of complex device structures employing several layer of polysilicon. As a conductor, polysilicon can be used to interconnect devices, allowing more flexible layout than obtained with only aluminum interconnections. Polysilicon can also be used for high-value resistors, thus further reducing the chip area (Sze, 1985).

#### 1.2 Objective

As the critical dimensions of semiconductor MOS transistor are continually scaled down to deep-submicron for higher levels of integration and performance, polydepletion effect and boron penetration through thin gate oxide have became more severe. In order to reduce poly-depletion effect and to suppress boron penetration, researchers have attempted several methods however none had claimed highly successful in reducing these two effects (Bin Yu et al., 1998). On the other hand, having a heavily doped gate can lead to boron penetration resulting in large threshold voltage shift, large charge trapping rate, degradation of p-channel subthreshold slope and poor reliability of the devices (Lurng Shehng Lee et al., 1998). Boron penetration is caused by thermal diffusion of boron through the gate oxide. To reduce boron penetration, source drain rapid thermal processing (hereafter abbreviated as SD-RTP)

duration and temperature need to be reduced further. However if the time and temperature is reduced too much, low activation (less than the solid solubility) can arise. Spike annealing is widely used now in the wafer fabrication industries as a replacement for SD-RTP. Spike annealing is a special RTP process with faster rampup rate and zero dwell time.

Here, the goal of the research work is to optimize the spike annealing process parameters for the 0.13-µm micrometer channel CMOS devices in Silterra (M) Sdn Bhd. In Silterra, the wafer fabrication factory mainly fabricates chips designed by customers. There is a need to study activation of the dopant in the polysilicon after the heat treatments because higher concentration of activated dopant in the polysilicon can actually reduce the polydepletion effect. At the same time, boron penetration through the thin insulator gate oxide layer has to be prevented.

#### 1.3 Scope of the Work

The work is mainly focused on optimizing the process recipe for 0.13-μm CMOS devices to reduce the polydepletion effect and suppress boron penetration.

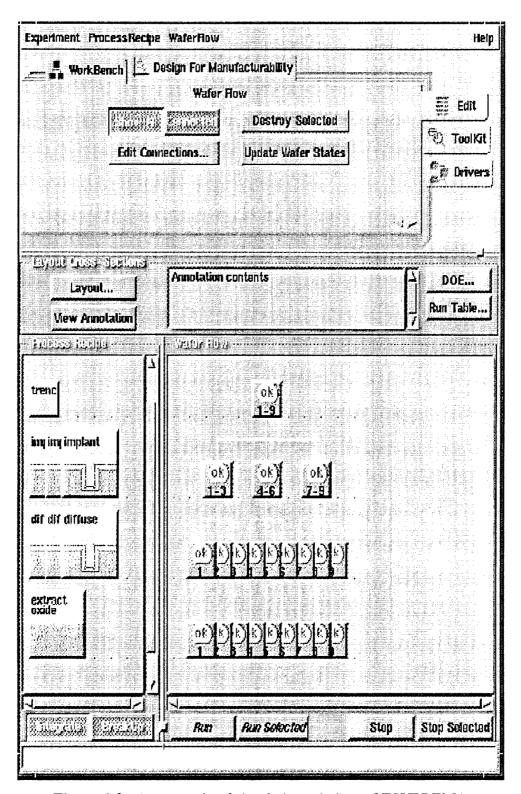

In this work, process simulation software is used to get the optimized process recipe for 0.13- $\mu$ m CMOS devices. The software comprises of 2 types of tools known as TSUPREM 4 for the process simulation and MEDICI for device characterization. An example of the simulation window is shown in Figure 1.2. TSUPREM 4 has been adopted from the SUPREM 3, which was developed at Stanford University in the 1980s. MEDICI is a 2-Dimensional finite element Poisson equation solver developed at Stanford University in the 1980s. This physically based process simulator can predict the outcome that result from specified process sequences. Simulation has been very important for the reason that it is always quicker and cheaper than performing experiments. It also provides information that is difficult or impossible to measure. The simulation software is also based on mathematical calculations such that finer

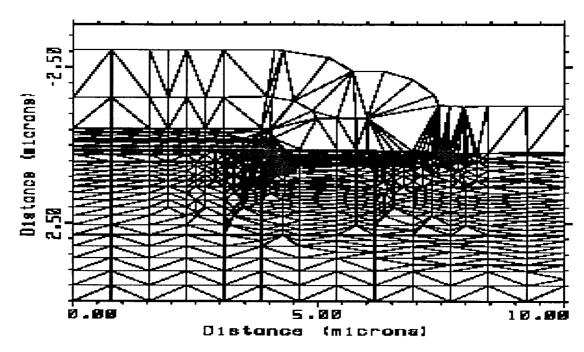

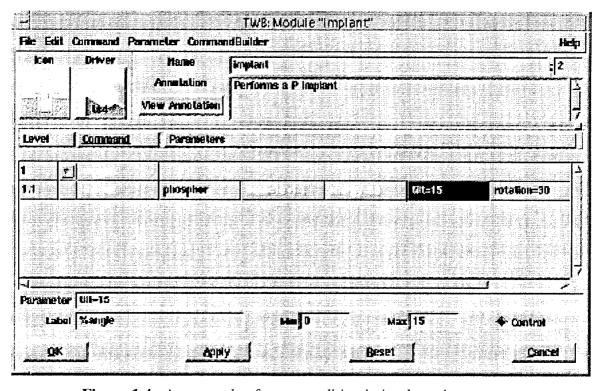

grid (Figure 1.3) is needed for accurate result. After obtaining a better grid, an experiment can be planned and executed. Effect of different process condition in ion implantation, annealing, deposition and etching was studied by using TSUPREM 4. Figure 1.4 shows an example of the editing the implantation process. MEDICI was used to do the device electrical characterization, namely Current-Voltage (hereafter abbreviated as I-V) and Capacitance-Voltage (hereafter abbreviated as C-V) characterization. In simulation, different implantation parameters such as dopant species, implant doses, implant energy, implant tilt and rotation angle can be changed. Different thickness of deposition can also be done, as well as different annealing conditions. Simulation software also have the function to check the cross-sectional view of the devices (Figure 1.5), dopant distribution profile, junction depth, well isolation, sheet resistance and etc. MEDICI can calculate the threshold voltage and drain current. It can also check the electrical flow lines, leakage region, electric field, plot the I-V curve, plot the C-V curve and many more.

Figure 1.2. An example of simulation window of TSUPREM4.

Figure 1.3. An example of finer grid for the model.

Figure 1.4. An example of process editing in implantation step.

Figure 1.5. Example of the simulation visual result using Taurus Visual.

After the simulation, an experiment with the optimized process parameters from the results was planned and executed to optimize the process parameters with the objective to reduce polydepletion effect and suppress boron penetration. In this experiment, wafers were run through the processes such as oxidation, implantation, deposition and annealing. Through the experiment, we can get the exact result because some of the new process recipes such as spike annealing, grain boundary diffusion rate and etc have not yet included in the simulation calculation. After that, structural and electrical characterizations were carried out to study the effect of the new process recipe.

For a process recipe to be industrially accepted, a physical experiment needs to be conducted by introducing the new recipe into the process flow of the device fabrication. This involved measurement on 0.13- $\mu$ m Metal Oxide Silicon Capacitor (hereafter abbreviated as MOSCAP) where C-V can be extracted and depletion thickness can then be calculated.

#### 1.4 Organization of the Thesis

This thesis is organized into five chapters.

Chapter 1 provides an introduction to the CMOS devices, motivation of this work, and an outline of the thesis.

Chapter 2 focuses on the problems encountered during the process of downscaling CMOS. A review of other works in reducing the polydepletion effect and boron penetration is also given in this chapter.

Chapter 3 describes the theory of the processes and characterization techniques. Processes such as oxidation, ion implantation, diffusion/annealing and deposition are explained. Characterization techniques like Secondary Ion Mass Spectrometry (hereafter abbreviated as SIMS), Focused Ion Beam (hereafter abbreviated as FIB) and Four-Point Probe (FPP) are the three characterization techniques used in this work.

In chapter 4, the experiment procedure for this work has been elaborated. This chapter will cover all the experimental processes involved, equipments utilized and characterization test conducted.

Chapter 5 focuses on the result, discussion and conclusion. In this chapter, the simulation and experiment results are given. Here, interpretation is made based on the

observation of the structural and electrical analysis. Conclusions of this work and recommendation process parameter made to Silterra are also described in this chapter.

#### **CHAPTER 2**

#### BACKGROUND AND LITERATURE REVIEW

#### 2.1 Gate Poly Depletion and Boron Penetration

Present deep submicron CMOS technologies including the  $0.13-\mu m$  modes always use polysilicon as gate material. The polysilicon should be degenerately doped; however, due to processing circumstances, insufficient doping concentration and/or insufficient activation can lead to the formation of a depletion layer in the gate, causing a nonnegligible voltage drop. This voltage drop in the gate reduces the effective gate voltage available to create inversion in the channel, and therefore reduces the device performance.

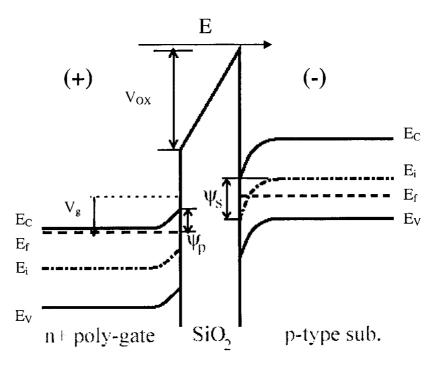

Figure 2.1. Band diagram of a poysilicon-gate depleted N-channel MOS capacitor (Reproduced from Choi Changhoon, 2002)

All device characteristics, i.e. charge/transcapacitance and drain current/transconductance are affected especially when using thin oxide thickness. Consider the band diagram of an n<sup>+</sup>-polysilicon gated n-channel MOS structure biased into inversion as shown in Figure 2.1. Since the oxide field is in the direction, which attracts negative charge toward the gate, the bands in the n<sup>+</sup>-polysilicon bend slightly upward near the surface. The field depletes the surface of electrons and forms a thin space-charge region in the polysilicon layer, which lower the total capacitance as given by:

$$\frac{1}{C} = \frac{1}{C_{OX}} + \frac{1}{C_{Si}} + \frac{1}{C_{den}}$$

(Eq 2.1)

Where  $C_{OX} = Oxide$  capacitance

$C_{Si}$  = Silicon substrate capacitance

$C_{dep}$  = Depletion capacitance

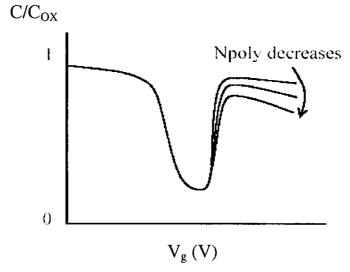

Typical low-frequency C-V curves in the presence of this gate depletion effect are shown in Figure 2.2. The maximum inversion capacitance is less than  $C_{OX}$ , and the higher the polysilicon doping concentration the less pronounced is the gate depletion effect.

Figure 2.2. C-V curves of N-channel MOS capacitors in the presence of polysilicon depletion effects. (Reproduced from Choi Changhoon, 2002)

It has been understood that increasing the poly doping will reduce the poly-depletion effect, but the doping is limited by other considerations, such as boron penetration through the thin gate oxide and dopant uniformity. The work reported by Choi Chang-Hoon (2002) showed how the dopant profile and gate geometric influence the polydepletion effect.

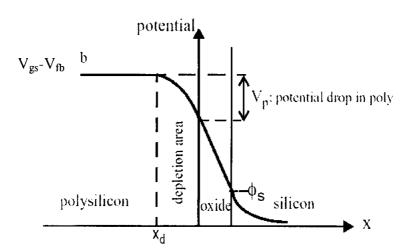

The potential drop  $(V_p)$  in the presence of the poly-depletion effect is represented in Figure 2.3. When the gate is doped by ion implantation, the dopant distribution as a function of position from the top of gate to the gate oxide direction can be represented as in Figure 2.4. Since the dopant density and carrier concentration vary with position, a built-in electric field exists leading to built-in depletion. Under thermal equilibrium, since there is no current flow, the built-in field  $(E_x)$  in a p-type poly-gate can be expressed as (Muller and Kamins, 1986):

$$E_x = -\frac{d\phi}{dx} \approx -\frac{kT}{q} \frac{1}{N_A} \frac{dN_A}{dx} \qquad d\phi = \frac{kT}{q} \frac{dN_A}{N_A}$$

(Eq. 2.2)

where  $N_A$  = active dopant concentration

q = electron charge

k = Boltzman constant

T = absolute temperature

Figure 2.3. Potential distribution of MOS from the top of the poly-gate to the silicon substrate considering poly-depletion effects. (Reproduced from Choi Changhoon, 2002)

A potential drop  $(\Delta V_{pl})$  is established at the interface due to the graded dopant distribution between  $x_l$  and  $x_2$ , which can be approximated as:

$$\Delta V_{p1} = \phi_1 - \phi_2 = \frac{kT}{q} \ln \frac{N_{A1}}{N_{A2}}$$

(Eq. 2.3)

When  $N_A$  changes from  $10^{20}$  to  $10^{18}$  cm<sup>-3</sup> (from SIMS profile for spike anneal at peak temperature  $1000^{\circ}$ C), the potential drop is about 0.12 V from equation (2.3) even without any gate bias, which is on the order of the threshold voltage for sub-micron MOSFETs. This additional potential drop across the polysilicon gate  $(\Delta V_{pI})$  does not contribute to gate bias, so it reduces transistor current.

**Figure 2.4.** Non-uniform, graded impurity distribution and corresponding energy-band diagram (Reproduced from Choi Changhoon, 2002)

For boron-implanted polysilicon subjected to RTP at 960-1150°C, the carrier mobility is higher than after furnace annealing at the same temperatures. This finding is explained by a nonuniform impurity distribution inside grains and by the related decrease of carrier scattering at the grain boundaries. At the lowest temperature (840°C) the impurity peak does not change from the position in the as-implanted process, a process sandwiched between ion implantation and annealing. At higher temperatures, diffusion of impurity atoms into polysilicon would be initiated. At 1080°C, impurity profiles become flat throughout the polycrystalline layer. The uniform doping level is retained up to 1200°C. This is the temperature range where the experimental carrier concentration fits the clustering model. It also means that at that temperature range, the average grain size is large enough to minimize segregation at grain boundaries (Borisenko *et. al*, 1997).

The dopant distribution in the poly is complicated by the implant and heat treatment steps, and by the poly grain size. So, various studies are needed to understand this problem.

Boron penetration becomes a major issue in the fabrication of deep submicron PMOS device with  $P^+$  poly doping and thin gate oxide. The boron penetration can cause the shifts of flatband voltage  $(V_{FB})$ , the distortion of C-V curves, the increase of subthreshold swing (S) and leakage current, and the deterioration of the gate oxide quality. Therefore, boron penetration should be eliminated to keep the desired performance of the surface-channel device. The boron penetration effect is characterized by the amount of flat band shift in the C-V curves of a MOS capacitor. Figure 2.5 shows the flat band voltage increases (shifts to the right side) when boron penetration increases.

Figure 2.5. High-frequency C-V curves of a MOS Capacitor for different boron penetration level. (Reproduced from Cao Min et. al, 1998)

#### 2.2 Methods Attempted by Other Researchers

As silicon devices are continuously scaled to smaller sizes, gate oxides becomes thinner, polydepletion effect and boron penetration effect have become more severe. Polysilicon, although is easy to manufacture, it also causes a lot of problems to CMOS devices. Researchers have been trying to find alternative gate materials to replace polysilicon. Poly-Si<sub>1-x</sub>Ge<sub>x</sub> has been introduced into Thin Film Transistor (hereafter abbreviated as TFT) devices since early 90s. Lee Wen-Chin *et. al.* (1998) and Yu Bin *et. al.* (1998) mentioned that with the germanium content of  $\approx 20\%$ , both PMOS and NMOS have the least poly depletion effect. It is because of the higher active dopant concentration observed. In these papers, the authors used conventional Low Pressure Chemical Vapor Deposition (hereafter abbreviated as LPCVD) system to grow poly-Si<sub>1-x</sub>Ge<sub>x</sub>. The results obtained are as follows;

1. For both types of devices, the thinner the gate oxide, the more will be the capacitance reduction in the inversion region. This is because a higher electric field will cause more depletion near the poly/SiO<sub>2</sub> interface.

- For NMOS devices, less polydepletion effect (determined by the capacitance reduction in inversion region) was observed for germanium content of 20%; while for PMOS, resistance to polydepletion effect increase as germanium mole fraction increases.

- 3. For NMOS devices, a threshold voltage  $(V_t)$  is not affected by germanium content whereas for PMOS, the more germanium contents, the less boron penetration, which means less  $V_t$  shift.

In the work reported by Ponomarev et. al. (2000), it was mentioned that boron diffusion in poly-SiGe is slower, while arsenic and phosphorus diffusions are faster than in poly-Si. These differences are increasing with germanium fraction. At the same time, boron activation is higher in poly-SiGe while arsenic is more difficult to activate in poly-SiGe, especially when the germanium percentage rises above  $\approx 50\%$ . These facts suggest that poly-SiGe allows for good dopant activation in p-type gates, while for higher germanium mole fractions n-type gate activation becomes problematic. In order to reduce this problem at NMOS, Rhee et. al. (2001) has introduced a Ge-redistributed poly-Si/SiGe stacked gate (hereafter abbreviated as GRPSG). GRPSG can improve the current performance of PMOS without the degradation of NMOS. In this method, thin poly-SiGe (20% - 40% germanium) and poly-Si capping layers were in-situ deposited by LPCVD using GeH<sub>4</sub> and SiH<sub>4</sub>. Then, N<sup>+</sup> poly implantation and annealing for germanium distribution were performed. N-type dopants such as phosphorus and arsenic can enhance the germanium diffusion into poly-Si more than boron. After the annealing for germanium redistributed, different germanium concentration was obtained at the gate/oxide interface between NMOS and PMOS. The current performance of the NMOS with GRPSG with low germanium content (< 5%) was not degraded.

Lin Chih-Yung et. al. (1995) reported the use of amorphous/polysilicon gate electrode in BF<sub>2</sub>-implanted poly-gated P-MOSFET's to suppress the boron penetration. SIMS analysis clearly shows that fluorine prefers to accumulate in the layer of amorphous

silicon. The retardation of boron diffusion is therefore achieved by trapping of fluorine in the amorphous layer of stacked amorphous/polysilicon (hereafter abbreviated as SAP) p-type gate due to a lower diffusion rate of fluorine in the amorphous silicon layer. Polysilicon depletion effect did not become severe by introducing the amorphous silicon. In addition, using the gate structures does not degrade gate oxide reliability. But Yu Bin *et. al.* (1998) noticed that the depletion in amorphous silicon is slightly more severe than polysilicon. The result indicated that amorphous silicon reduces the gate dopant diffusion but increases gate depletion after rapid thermal annealing (hereafter abbreviated as RTA) more than 1000°C.

Besides using alternate gate materials and changing gate microstructure, researchers also did a lot of studies in gate doping. Sun W.T. *et. al.* (1995) reported that phosphorus or arsenic co-implant in p-poly-gate can prevent boron penetration. In the paper, a comprehensive study of the phosphorus dosage and annealing condition dependencies of boron penetration and poly-depletion is presented. The experimental results show that the boron penetration in BF<sub>2</sub> implanted poly-gate is significantly reduced as the dose of co-implanted phosphorus increases. The phosphorus dose about 1.5 x 10<sup>15</sup> cm<sup>-2</sup> in p<sup>+</sup>-poly gate can effectively retard the penetration of boron in BF<sub>2</sub> 3 to 5 x 10<sup>15</sup> cm<sup>-2</sup> doped poly gate under 900°C, 60 min annealing (30 min reflow anneal, and 30 min post-contact implant anneal). The performance of boron-penetration-free phosphorus co-implanted p<sup>+</sup>-poly gate MOSFETs is also shown to be much better than the device with boron-penetration. In arsenic co-implanted p-poly gate, it also appears that arsenic co-implant would also retard boron penetrating through thin gate oxide. However, boron penetration becomes very severe when annealed at higher temperature for longer time.

In the work reported by Kuroi et. al. (1995), nitrogen implantation into polysilicon gate was introduced. In these papers, authors claim that nitrogen implantation can reduce the problem of boron penetration. It is because the nitrogen implanted into the polysilicon gate is segregated into the gate oxide during heat treatment after

implantation. The nitrogen in the gate oxide film can act as a barrier layer for boron penetration and reduce the random failures of gate oxide films under highly doped polysilicon gates. Yu Bin et. al. (1997) mentioned that a nitrogen dose of 5 x 10<sup>15</sup> cm<sup>-2</sup> is the optimum choice at implant energy of 40 KeV in terms of the overall performance of both p- and n-MOSFET's. The suppression of boron penetration is confirmed by the SIMS profiles to be attributed to the retardation effect in polysilicon with the presence of nitrogen. SIMS profile showed that nitrogen peak and boron peak is at the same location. It is believed that nitrogen peak in the bulk poly-Si is mainly responsible for the suppression, since the boron diffusion is retarded in the bulk. High nitrogen dose (1 x 10<sup>16</sup> cm<sup>-2</sup>) results in polydepletion and increase of sheet resistance in both unsilicided and silicided p<sup>+</sup> poly, degrading the transistor performance. Chao T.S. et. al. (1997) is using nitrogen co-implanted with boron method to suppress the boron penetration. In this method, it was found that nitrogen combines with the boron to form a B-N complex. This B-N complex can retard the penetration of boron itself and it was identified by X-ray photoelectron spectroscopy (hereafter abbreviated as XPS). The optimum dosage of nitrogen should be 1 x 10<sup>15</sup> cm<sup>-2</sup>. Excessive amount of the nitrogen concentration will increase sheet resistance,  $R_S$  and polydepletion effect. In the work reported by Liu C. T. et. al. (1996), nitrogen was implanted into silicon substrate prior to the growth of gate oxides. From the SIMS profile, the nitrogen peak is observed to be in the gate oxide and boron concentration falls off right before the nitrogen peak. No boron is seen beyond the oxide layer.

Apart from implanting nitrogen into polysilicon or silicon substrate, annealing in nitrogen ambient can also be used to establish a nitrogen diffusion barrier at the interface of the poly-Si and oxide. Yu Bin et. al. (1998), Han L.K. et. al. (1995) and Chao T.S. et. al. (1997) mentioned that thermally nitrided oxide or reoxidized nitrided oxide in NO, N<sub>2</sub>O or NH<sub>3</sub> ambient can act as a diffusion barrier for boron. However, H atom residues during the NH<sub>3</sub> nitridation reduce the resistance to hot carrier stressing, introduces a large number of interface traps and fixed oxides charge. This contributes to 1 by Flickers noise. An additional reoxidation process needs to be done

to reduce the H atom. Hence, the NH<sub>3</sub> nitridation process is too complex to implement in a real production line. Therefore, a nitridation process on the oxide surface without H incorporation has started to be used. But between N<sub>2</sub>O and NO, NO is the preferred ambient. It is because N<sub>2</sub>O based oxides require a much higher thermal budget for sufficient nitrogen concentration. Han L. K. et. al. (1995) reported the use of rapid thermal NO-nitrided SiO<sub>2</sub> as an alternate oxynitride with enhanced boron diffusion barrier properties while maintaining a low thermal budget and H-free nature of the processing ambient. In this method, thermal oxides are grown at 1050°C in pure oxygen followed by in-situ nitridation at 1000°C in pure NO ambient, finally received an in-situ nitrogen anneal at 1050°C. Results show that NO-nitrided SiO<sub>2</sub>, as compared to conventional thermal SiO<sub>2</sub>, exhibits much higher resistance to boron penetration and also reduce polydepletion effect. It is believed to be due to the incorporation of nitrogen in the dielectric during NO nitridation. In the work of Xiang Qi et. al. (2000), ultra-thin nitride/oxynitride stack gate dielectric was formed by the thermally growing of oxynitride followed by Si<sub>3</sub>N<sub>4</sub> deposition. Pre-doped gates for both N- and P-MOS devices (P-doped for NMOS and N-doped for PMOS) are employed to minimize poly depletion and maximize drive currents. The result shows that the stack gate dielectric has strong boron penetration resistance, which allows pre-doped for both type devices to minimize poly depletion and improve device performance.

Boron diffusion and activation is normally controlled by the annealing process after the implantation. To prevent boron penetrating through thin gate oxide, one can optimize the annealing parameters to get the optimize boron activation and diffusion in polysilicon gate. Fiory *et. al.* (2000) reported that when choosing ion implants and thermal budget for the polysilicon gate engineering in deep submicron devices, the following conditions must be met:

(i) The activation of implanted dopants (usually boron for PMOS and arsenic or phosphorus for NMOS devices) should be high across the gate in order to minimize the poly-depletion effect and to maximize the device speed;

- (ii) Boron penetration through the thin gate oxides (which causes threshold voltage shifts in PMOS devices) should be minimal; and

- (iii) Lateral diffusion (which cause cross-doping in connected gates) should be minimal.

These goals are difficult to achieve, since electrical activation of dopants in poly-Si entails rapid grain boundary diffusion and slower diffusion within grains. Fiory *et. al.* (2000) used spike annealing to avoid boron penetration through gate oxide. It is because of sufficient rapid grain boundary assisted diffusion of boron in polycrystalline silicon films where high carrier concentration could be achieved by utilizing high temperature annealing, since the concentration of boron in solid solution increases with temperature. It is concluded that spike annealing can increase effective diffusivity of boron in polysilicon of up to 200 times greater than in crystal silicon. The activation of boron also increases based on the lower sheet resistance of the polysilicon after spike annealing. In the work of Yu Bin *et. al.* (1999), laser thermal process (hereafter abbreviated as LTP) was introduced. LTP has 3 attractive features:

- 1. "Zero" thermal budget. Laser pulses last a few nanoseconds, which is about 8 orders of magnitude shorter than rapid thermal processing. Thermal diffusion of dopants is almost negligible.

- 2. Metastable process without dopant solid solubility limit. This allows active dopant concentrations larger than 10<sup>21</sup> cm<sup>-3</sup> to be achieved,

- 3. Local selective heating of specific regions of silicon wafer. No thermal budget is added to  $V_t$ /retrograde channel/halo profiles.

Although the results show the sheet resistance is lower, activation of the dopants occurs during LTP. But the gate-depletion effect is not significantly changed by LTP. Unfortunately, LTP could not be made into production process yet. The main problem faced is the non-uniform heating.

From the literature review work, the polydepletion effect and boron penetration effect are well understood. Based on the literature and equipment availability in Silterra, the spike annealing and NO gate oxide have been chosen as the main focus in this work.

#### **CHAPTER 3**

## THEORY OF PROCESSES AND CHARACTERIZATION TECHNIQUES

#### 3.1 Processes

In this experimental work, several processes were adopted. These processes are oxidation, chemical vapour deposition, ion implantation and annealing. The theory of the processes is discussed in the following subsections.

#### 3.1.1 Oxidation

Oxidation of silicon is a thermal process to grow an oxide layer. This process is easily achieved by heating the silicon substrate to temperatures typically in the range of 900 - 1200°C. Oxidation can divided into wet or dry oxidation, depending on the atmosphere in the furnace. The atmosphere in the furnace can either contain pure oxygen or water vapour. Both of these molecules diffuse easily through the growing SiO<sub>2</sub> layer at these high temperatures. Oxygen arriving at the silicon surface will react with silicon to form silicon dioxide. The chemical reactions that take place are either

$$Si + O_2 \rightarrow SiO_2$$

for so-called dry oxidation or

$$Si + 2H_2O \rightarrow SiO_2 + 2H_2$$

for wet oxidation.

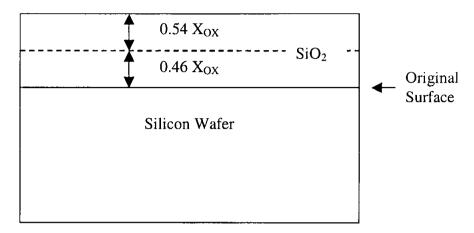

Due to the stoichiometric relationships in these reactions and the difference between the densities of Si and SiO<sub>2</sub>, about 46% of the silicon surface is "consumed" during oxidation. That is, for every 1  $\mu m$  of SiO<sub>2</sub> grown, about 0.46  $\mu m$  of silicon is consumed (see Figure 3.1).

Figure 3.1. Oxidation process on silicon.

#### 3.1.1.1 Oxide Growth Kinetics

The growth of silicon dioxide only involved surface reaction. However, after the layer of SiO<sub>2</sub> is getting thicker, the arriving oxygen molecules must diffuse through the growing SiO<sub>2</sub> layer to react with the silicon surface.

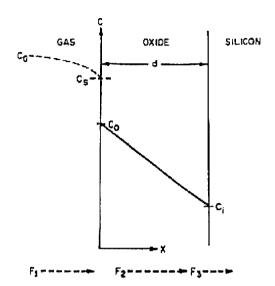

"Deal/Grove" model (Puchner, 1996) is used to explain the oxide growth kinetics. This model is generally valid for temperatures between 700 and  $1300^{\circ}$ C, partial pressures between 0.2 and 1.0 atmosphere, and oxide thickness between 0.03 and 2  $\mu$ m for both wet and dry oxidation. To understand this model, please refer to Figure 3.2, and let:

$C_g$  = concentration of oxidant molecules in the bulk gas

$C_s$  = concentration of oxidant molecules immediately adjacent to the oxide surface

$C_o$  = equilibrium concentration of oxidant molecules at the oxide surface

$C_i$  = concentration of oxidant molecules at the Si/SiO<sub>2</sub> interface

Figure 3.2. Deal/grove model for oxidation.

Note that: 1)  $C_g > C_s$  (due to depletion of the oxidant at the surface)

2)  $C_s > C_o$  (due to the solubility limits of SiO<sub>2</sub>)

The oxidizing species (oxygen or water vapour) are flowed from the bulk gas to the gas/oxide interface with flux  $F_1$  (where flux is the number of molecules crossing a unit area per unit time). The species are flowed diffuse through the growing oxide toward the silicon surface with flux  $F_2$ , and react at the Si/SiO<sub>2</sub> interface with flux  $F_3$ . Mathematically:

$F_I$  = flux of oxidant from gas to surface

$$F_1 = H_g (C_g - C_s)$$

(Eq 3.1)

where  $H_g$  = the gas phase mass transfer coefficient.

$F_2$  = flux through the oxide layer

$$F_2 = -D\frac{dC}{dx} \tag{Eq 3.2}$$

where D is the diffusivity of the oxidant molecule in  $SiO_2$  and C is the concentration.

Assumed a linear concentration gradient inside the oxide layer, then:

$$F_2 = D \frac{(C_o - C_i)}{v}$$

(Eq 3.3)

where y is the current value of the oxide thickness.

Finally:

$$F_3 = K_s \times C_i \tag{Eq 3.4}$$

where  $K_s$  = the rate constant for the surface chemical reaction.

Now let's look at  $F_1$  more closely. By Henry's Law:

$$C_o = H \times P_s$$

and

$$C^* = H \times P_s$$

(Eq 3.5)

where H is Henry's Law constant,  $C^*$  is the equilibrium concentration of oxidant molecules in the bulk SiO<sub>2</sub>, and  $P_s$  and  $P_g$  are the partial pressures of the oxidant molecules adjacent to the SiO<sub>2</sub> surface and in the bulk gas, respectively. From the Ideal Gas Law:

$$C_g = \frac{P_g}{kT}$$

and

$$C_s = \frac{P_s}{kT}$$

(Eq 3.6)

where k is Boltzman's constant and T is the temperature in degrees K. Therefore,  $F_I$  can be re-written as:

$$F_{1} = H_{g}(C_{g} - C_{s}) = H_{g}(\frac{P_{g}}{kT} - \frac{P_{s}}{kT})$$

$$F_{1} = \frac{H_{g}}{kT}(P_{g} - P_{s}) = \frac{H_{g}}{kT}(\frac{C^{*}}{H} - \frac{C_{o}}{H})$$

$$F_{1} = h(C^{*} - C_{o})$$

(Eq 3.7)

where  $h = H_g/HkT$ . At steady state, all three fluxes should be equal. In other words,

$F_1 = F_2 = F_3$  under these conditions:

$$C_i = \frac{C^*}{(1 + \frac{K_s}{h} + \frac{K_s * y}{D})} \quad \text{and}$$

$$C_o = \frac{(1 + \frac{K_s * y}{D})C*}{(1 + \frac{K_s}{b} + \frac{K_s * y}{D})}$$

(Eq 3.8)

If the oxidation growth rate depends only on the supply of oxidant to the  $Si/SiO_2$  interface, it is said to be diffusion controlled. Under this condition, D is close to zero. Therefore:

$$C_i \approx 0$$

and  $C_o \approx C^*$

If, on the other hand, there is plenty of oxidant at the interface, the growth rate depends only on the reaction rate. This situation is called "reaction-controlled." In this case, *D* approaches infinity, and:

$$C_i = C_o = \frac{C^*}{(1 + \frac{K_s}{h})}$$

(Eq 3.9)

To compute the growth rate itself, let  $N_I$  be the number of oxidant molecules per cubic cm incorporated into the oxide layer. Then, the differential equation can be written as below:

$$\frac{d}{dt}N_1(y) = F_3 = K_s \times C_i = \frac{K_s C^*}{(1 + \frac{K_s}{h} + \frac{K_s^* y}{D})}$$

(Eq 3.10)

Under the boundary condition that y = 0 when t = 0, first order differential equation can be solved as:

$$y^2 + Ay = B(t+T)$$

(Eq 3.11)

Where

$$A = 2d\left(\frac{1}{K_s} + \frac{1}{h}\right)$$

$$B = \frac{2DC^*}{N_1}$$

$$T = \frac{(yi^2 + Ayi)}{B}$$

and yi is the initial oxide thickness. For short times, the growth rate is reaction limited, and the oxide thickness is approximately:

$$y = \frac{B}{A}(t+T) \tag{Eq 3.12}$$

For longer times, growth is diffusion-limited, and the approximation used is:

$$v = \sqrt{Bt}$$

(Eq 3.13)

A and B are constants which correspond to the oxidation conditions (i.e. - temperature and wet or dry) (Puchner, 1996).

### 3.1.1.2 Oxidation Reactor

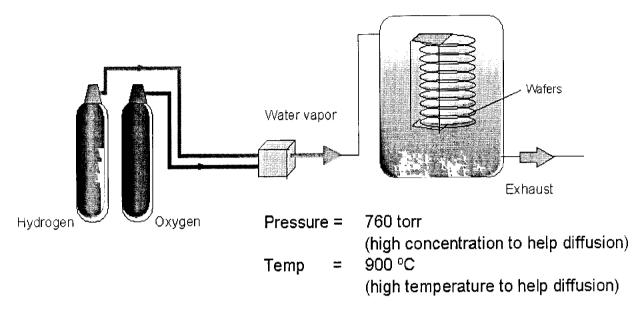

Figure 3.3 shows a simple oxidation reactor system. Here the wafers were held in a vertical holder with pure water being pumped through. The water vapour was made from the reaction of hydrogen and oxygen gases. The temperature of the furnace was increased to 750°C to let the reaction of the water vapour on the wafer surface to form surface oxygen and hydrogen gas. Nitrogen gas will purge into the oxidation reactor after the formation of SiO<sub>2</sub>. The wafer will be annealed to let the nitrogen to react with oxygen layer, forming an oxynitride layer.

Figure 3.3. Simple diagram of oxidation reactor.

# 3.1.2 Chemical Vapour Deposition (CVD)

CVD is an extremely popular way to deposit thin film layers in integrated circuit manufacturing. The process is controlled by two factors namely the diffusion of gases to wafer surfaces and the reaction of the gases on the wafer surfaces. Typically the CVD process is designed in such a way that deposition is limited by only one of the two factors, and is independent of the other. The mathematics of gaseous diffusion and chemical reactivity in furnaces are very difficult and not fully understood. Therefore it is critical for integrated circuit manufacturers to develop standard, repeatable recipes (gas flows, temperatures, deposition time, etc.) and avoid deviating from them.

For better uniformity, LPCVD is used. Deposition rate in an LPCVD process is limited by gaseous diffusion. For uniformity, it is critical to have uniform gas flow to all wafers in an LPCVD furnace. LPCVD typically operates at a much higher temperature (up to 1000°C) than atmospheric pressure CVD (hereafter abbreviated as

APCVD). Polysilicon and most dielectrics are deposited by LPCVD. Typical LPCVD process pressures are from 0.1 to 1.0 torr.

# 3.1.2.1 Polysilicon Deposition Mechanism

Polysilicon is deposited by pyrolyzing silane between 575°C and 650°C in a low-pressure reaction:

$$SiH_4(g) \rightarrow Si(s) + 2H_2(g)$$

Either pure silane or 20 to 30% silane in nitrogen is bled into the LPCVD system at pressure of 0.2 to 1.0 torr. For practical use, a deposition rate of about 10 to 20 nm/min is required. The properties of the LPCVD polysilicon films are determined by the deposition pressure, silane concentration, deposition temperature and dopant content. The deposition rate is defined as below

Deposition Rate =

$$\frac{\text{Thickness of Film}}{\text{Time to grow}} \left( \frac{\mathring{A}}{\text{Min}} \right)$$

### 3.1.2.2 LPCVD Furnace

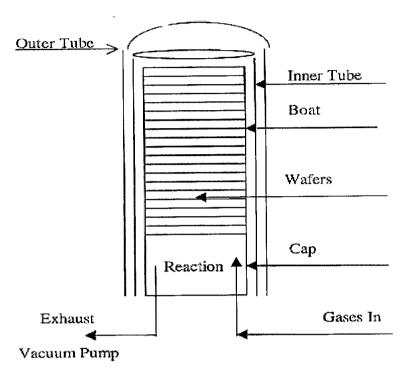

An LPCVD furnace is shown in Figure 3.4. A typical LPCVD system composes of a chamber and vacuum pump, source gas inlet controls, heating and temperature controls. The source gas is depleted (consumed) as it travels the length of the tube, often the temperature is increased toward the rear of the tube to help compensate for the decreased gas concentration.

Figure 3.4. LPCVD Furnace for polysilicon deposition.

### 3.1.3 Ion Implantation

Ion implantation is the introduction of ionized dopant atoms into a substrate with enough energy to penetrate beyond the surface. The most common application is substrate doping. The common dopants that are used in the ion implantation are shown in Table 3.1. The use of 3 to 500 KeV implant energy for dopant ions is sufficient to implant the ions from 100 to 10,000 Å below the silicon surface. These depths place the atoms beyond any surface layers of 30 Å native SiO<sub>2</sub>, and therefore any barrier effect of the surface oxides during impurity introduction is avoided. The depth of implantation, which is proportional to the ion energy, can be selected to meet a particular application.

The major advantage of ion implantation technology is the capability of precisely controlling the number of implanted dopant atoms. Upon annealing the target (heating to elevated temperatures of approximately 600-1000°C), precise dopant

concentrations between  $10 \times 10^{14}$  to  $10 \times 10^{21}$  atoms/cm<sup>3</sup> in the silicon are obtained. Furthermore, the dopant's depth distribution profile can be well controlled. Some common dopants for silicon are listed in the Table 3.1 below.

Table 3.1: List of dopants commonly used in semiconductor doping.

| Donors (Electron-increasing Dopants) | Acceptors (Hole-increasing Dopants) |  |  |

|--------------------------------------|-------------------------------------|--|--|

| Group V elements                     | Group III elements                  |  |  |

| D                                    | В                                   |  |  |

| As<br>Sb                             | Ga                                  |  |  |

|                                      | In                                  |  |  |

|                                      | Al                                  |  |  |

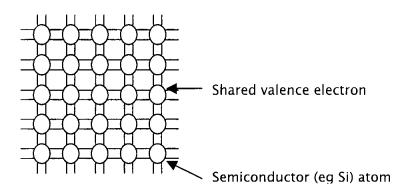

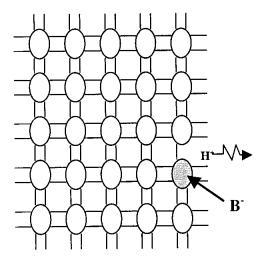

Silicon, being an element from Group IV of the Periodic Table of the Elements (Appendix A), has four valence electrons. In an undoped silicon crystal, each atom shares these electrons with its four nearest neighbours via covalent bonding (see Figure 3.5). Dopant atoms can be either as "donors" or "acceptors." Donors normally elements from Group V increase the electron concentration in the silicon, whereas acceptors normally elements from Group III increase the hole concentration.

Figure 3.5. Atoms bonding diagram for an undoped silicon crystal.

When Group V elements such as arsenic or phosphorus are introduced into the silicon crystal lattice, four of the five valence electrons fit into the silicon bonding structure.

The fifth electron, however, is weakly bound, and at room temperature is free to move through the crystal (Figure 3.6). It is thus said to be "donated" to the semiconductor.

Figure 3.6. N-type dopant in the silicon crystal causes an excessive electron in the lattices.

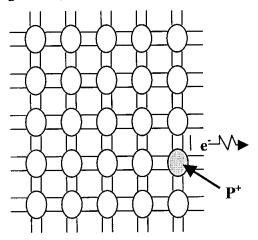

Likewise, Group III elements such as boron have only three valence electrons, and therefore cannot complete all four of the available bonds when substituted for a silicon atom. These elements, however, readily "accept" an electron from a nearby silicon-silicon bond. This creates a hole, which is also free to wander through the crystal lattice at room temperature (Figure 3.7).

Figure 3.7. P-type dopant in the silicon crystal cause a hole in the lattice.

# 3.1.3.1 Ion Implanter

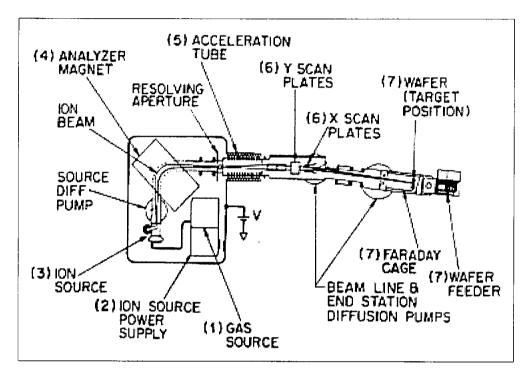

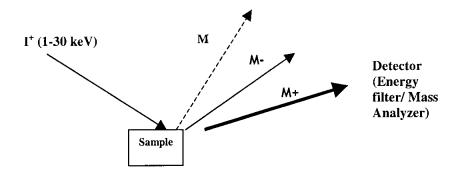

**Figure 3.8.** Basic diagram of ion implanter. (Reproduced from Silterra, 2000)

Figure 3.8 shows a simplified diagram indicating the major elements of a medium-current ion implanter system. In the ion implanter system, the ion source will start with selected molecular species from the gas source and converts it into ion. The ions are accelerated, and then enter the analyser magnet for ion selection. The exit beam of desired implant ions are chosen based on the charge-to-mass ratio of the ions, and the analyser is generally sensitive enough to discriminate against adjacent mass numbers. The ions are then given a final acceleration at the acceleration tube, after which the ion beam will be slightly electrostatically deflected to separate it from any neutral atoms that may have formed.

The beam is then scanned over the wafer surface, either electrostatically, mechanically, or by a combination of the two controlled X- and Y-scan plates. In addition, an electron source may be near the wafer to "flood" the surface with electrons and prevent a charge build-up on insulating surfaces such as SiO<sub>2</sub> or silicon nitride. If not eliminated, this kind of charge build-up can be severe enough to cause gate oxide failure because of electrical breakdown from the gate to the substrate through the oxide.

### 3.1.4 Annealing and Diffusion

Basically, annealing in the CMOS processes is for the purpose of activation and dopant diffusion. After a dopant is implanted in silicon an annealing step has to be performed to activate the introduced dopant atoms and to repair the damage caused by the ion implantation. In modern process, the technology of RTA processes is the method of choice with typical annealing times of several seconds. Diffusion can be defined as the random walk of an ensemble of particles from regions of high concentration to regions of lower concentration. In integrated circuit fabrication, diffusion is used to introduce dopants in controlled amounts into the semiconductor substrate.

According to the First Law of Diffusion (Puchner, 1996), the transfer of solute atoms per unit area in a one-dimensional flow can be described by the following equation:

$$J = -D\frac{\partial C(x,t)}{\partial x}$$

(Eq 3.14)

where J is the particle flux, C is the concentration of the solute, D is the diffusion coefficient, x is the distance into the substrate, and t is the diffusion time. The negative sign indicates that the diffusing mass flows in the direction of decreasing concentration.

From the Conservation of Mass, we also know that:

$$\frac{\partial C}{\partial t} = -\frac{\partial J}{\partial x} \tag{Eq 3.15}$$

If we combine this relationship with the 1st Law of Diffusion, then we have derived the 2nd Law of Diffusion (otherwise known as Fick's Law), which states:

$$\frac{\partial C}{\partial t} = D \frac{\partial^2 C}{\partial x^2}$$

(Eq 3.16)

In order to solve Fick's Law, one initial condition and two boundary conditions are required. Two solutions to Fick's Law are generally encountered in Integrated Circuit (hereafter abbreviated as IC) fabrication: infinite-source and limited-source diffusion. Both solutions are described below.

# 3.1.4.1 Infinite-source Diffusion (Pre-deposition)

Infinite-source diffusion requires a constant surface concentration of diffusing atoms. This generally corresponds to the process step known as "pre-deposition." In this case, the initial condition and boundary conditions are:

$$C(x,0) = 0$$

$$C(0,t) = C_s$$

$$C(\infty,t) = 0$$

(Eq 3.17)

where  $C_s$  is the surface concentration. The solution to Fick's Law (Puchner, 1996) under these conditions is:

$$C(x,t) = C_s \quad erfc \left[ \frac{x}{2\sqrt{Dt}} \right]$$

(Eq 3.18)

where "erfc" is the complementary error function.

# 3.1.4.2 Limited-source Diffusion (Drive-in)

Limited-source diffusion requires a constant amount of total dopant per unit area of the diffusing surface. This corresponds to the process step known as "drive-in" or any subsequent heat cycles. In this case, the initial condition and boundary conditions are:

$$C(x,0) = 0$$

$$\int C(x,t)dx = S$$

$$C(x,\infty) = 0$$

(Eq 3.19)

where S is called the "dose." The solution to Fick's Law under these conditions is:

$$C(x,t) = \frac{S}{\sqrt{\pi Dt}} \exp\left[\frac{-x^2}{4Dt}\right]$$

(Eq 3.20)

### 3.1.4.3 Diffusion Mechanism

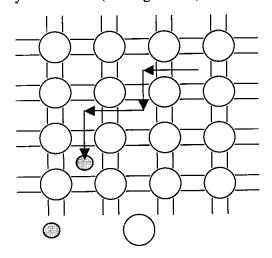

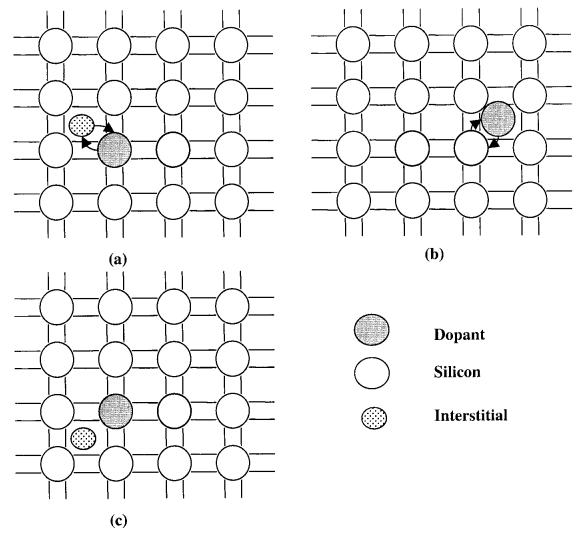

From the past literatures (Sze, 1988, Fahey et. al., 1989, Taylor et. al., 1993), three possible atomic diffusion mechanisms have been established. The first one is the direct mechanism. In this mechanism, the impurities, which have small ionic radii, can travel directly interstitial. (see Figure 3.9).

Figure 3.9. Direct diffusion mechanism within crystal targets. The diffuser can travel exclusively on interstitial sites.

The second possible mechanism is vacancy mechanism. In this mechanism, the substitutional dopants migrate through the host lattice by moving via adjacent vacant lattice sites. (see Figure 3.10a). To avoid oscillations of this exchange procedure, the vacancy must move at least to a third-neighbour site away from the dopant. Thus, the vacancy or another vacancy within the diffusion regime can return on a different path within the silicon's diamond lattice. Then long-range migration of the dopant will take place (see Figure 3.10b). Energetic details of this complicated exchange can be found in Fahey et. al, 1989.

Figure 3.10. Dopant diffusion by vacancy mechanism.

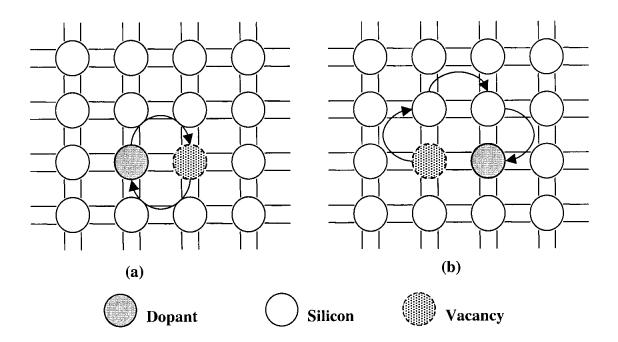

The third one is the interstitial mechanism (see Figure 3.11). In this mechanism, dopant diffusion takes place when a dopant at a substitutional site is approached by a silicon interstitial (Figure 3.11a). The dopant is kicked out by the interstitial to reside at interstitial position (Figure 3.11b), while the original self-interstitial has disappeared by occupying the regular lattice site. Now this interstitial dopant is able to move towards an adjacent lattice site to re-form a silicon interstitial by the same "kick-out" process, like the interstitial dopant itself was generated (Figure 3.11c).

Figure 3.11. Dopant diffusion via a substitutional-interstitialcy interchange.

# 3.1.4.4 Diffusion in Polysilicon

Polysilicon shows extraordinary high diffusivity for dopants. This fact allows the dopants to diffuse even longer distances within the polysilicon material in reasonable short time periods.

Dopant transport within polysilicon involves four major mechanisms:

• fast diffusion in grain boundaries

- segregation between grain interior and grain boundaries

- grain boundary motion

- grain interior diffusion

A crystal structure of a grain bulk/grain boundary network can be used to understand the dopant/grain boundary system and the according diffusion mechanisms. From the tetrahedral bonding network for two polysilicon grains separated by a grain boundary (see Figure 3.12), it can be seen that the number of bonds crossing from one grain into the neighbouring grain is reduced at the interface. This can cause a corresponding high density of dangling bonds due to the fracture of the crystal along the interface. Therefore, this boundary area may be a preferred low energy local minimum for dopants. This outstanding energetic properties in combination with the irregularity of the tetrahedral bonding at the interface makes the grain boundary to be the fast diffusion path for dopants.

The second transport mechanism is segregation between grain interior and grain boundaries. This mechanism happened if the dopant and the grain boundary are a closed system and there is enough space in the grain boundary that had occupied by other dopant. The segregation of dopants into the grain boundary can be described by trapping and emission mechanisms. The capture and emission rates depend on the number of occupied and free states in the grain boundary, where the total number of states is limited by the grain boundary area.

The third transport mechanism is related to the grain growth phenomenon. In the grain growth process, the grain boundaries are moving. During moving of the grain boundaries, the dopants are incorporated in the grain boundaries. This movement results in a net dopant transport.

Figure 3.12. Three-dimensional perspective drawing of a grain/grain boundary network. (Reproduced from Puchner, 1996)

If the crystal structure of the polysilicon grain bulk region shows a regular silicon lattice, the diffusion of dopants within the grain interior regions will be treated like normal diffusion in silicon. Moreover, effects like dopant activation and clustering play an important role in the grain bulk and have to be considered for a complete description of the polysilicon diffusion problem.

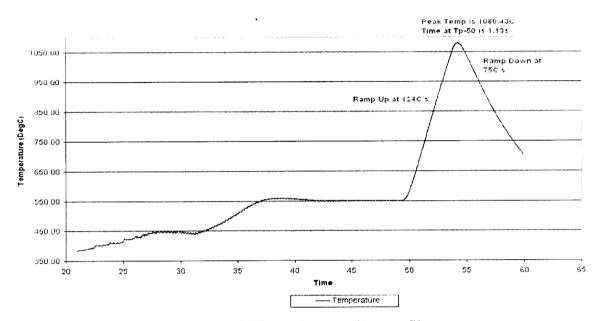

# 3.1.4.5 Annealing Profile

Annealing profiles in this experiment are both spike annealing and normal RTA. Figure 3.13 shows an example of the spike annealing profile. The process started with slow ramp at 25°C/s from 450°C to 550°C. The temperature is then stabilized for 2 seconds before the high ramp up. There is zero dwell time for spike anneal. So, after reaching the peak temperature, the wafer is treated with high ramp down rate at 75°C. Spike annealing has high peak temperature that can maximize the dopant activation,

aggressive ramp-up that can minimize the dopant diffusion and aggressive ramp-down that can minimize the dopant deactivation.

Figure 3.13. Spike annealing profile.

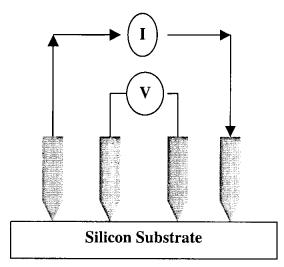

# 3.2 Characterization Techniques