## Development of an 8-bit CPU using TTL logic

by

Muhamad Aidil b Jazmi, 3534

Dissertation submitted in partial fulfilment of the requirements for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

#### **DECEMBER 2006**

Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

### CERTIFICATION OF APPROVAL

#### Development of an 8-bit CPU using TTL logic

by

Muhamad Aidil b Jazmi

Dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfillment of the requirement for the BACHELOR OF ENGINEERING (Hons) (ELECTRICAL & ELECTRONICS ENGINEERING)

Approved by,

du

(Dr. Yap Vooi Voon)

UNIVERSITI TEKNOLOGI PETRONAS

TRONOH, PERAK

December 2006

i

## CERTIFICATION OF ORIGINALITY

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

MUHAMAD AÍDIL B JAZMI

#### ABSTRACT

Computer is an integral part of human life nowadays and the complexity of computers grows in parallel with their processing capability. This project will build the basis of understanding the operation of the central processing unit of a computer by developing an 8-bit central processing unit from discrete TTL logic ICs. This CPU will also be used as a teaching aid for Computer System Architecture class in UTP. By building the CPU discretely, detailed operation of a computer can be understood from the hardware up to software level. The project discusses detailed electrical operation of blocks in the central processing unit mainly the processor. At the end of the project, a fully working microcomputer was constructed and studied in detail.

# **TABLE OF CONTENTS**

|     | CER  | TIFICATIONS                                 | i   |

|-----|------|---------------------------------------------|-----|

|     | ABS  | ГКАСТ                                       | iii |

| 1.0 | INTF | RODUCTION                                   | 1   |

|     | 1.1  | Background                                  | 1   |

|     | 1.2  | Problem statement                           | 1   |

|     | 1.3  | Objective and scope of study                | 3   |

| 2.0 | LITE | ERATURE REVIEW                              | 4   |

|     | 2.1  | Page table                                  | 4   |

|     | 2.2  | Universal asynchronous receiver transmitter | 7   |

| 3.0 | MET  | HODOLOGY                                    | 10  |

|     | 3.1  | Overview                                    | 11  |

|     | 3.2  | Instruction set architecture                | 12  |

|     |      | 3.2.1 Operand addressing                    | 12  |

|     |      | 3.2.2 Addressing mode                       | 13  |

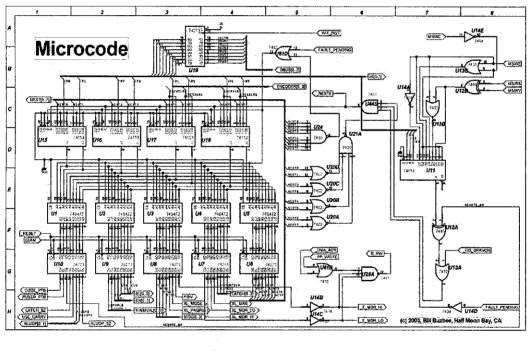

|     | 3.3  | Microcode                                   | 13  |

|     |      | 3.3.1 Microcode sequencer                   | 15  |

| 4.0 | RES  | ULTS AND DISCUSSIONS                        |     |

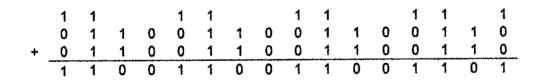

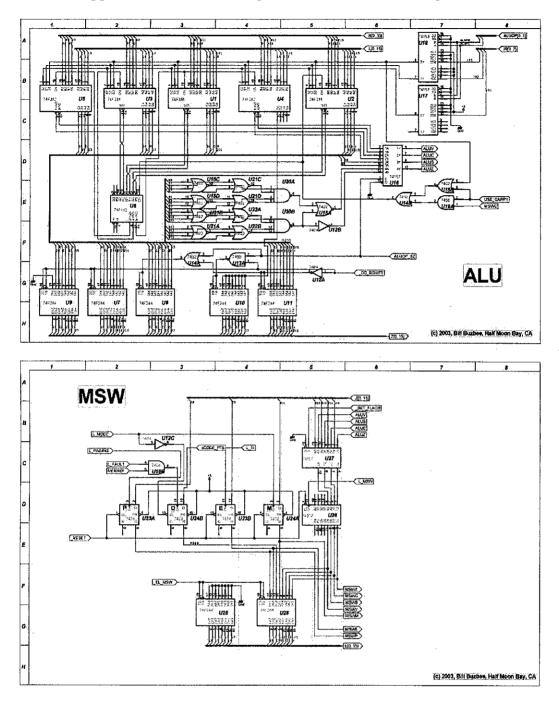

|     | 4.1  | ALU card construction and testing           | 17  |

|     |      | 4.1.1 Results                               | 23  |

|     | 4.2  | Control card study                          | 24  |

|     | 4.3  | Clocks                                      | 27  |

|     | 4.4  | Microcode sequencing example                | 28  |

|     | 4.5  | Construction diary                          | 31  |

|     | 4.6  | Fibonacci counter test                      | 32  |

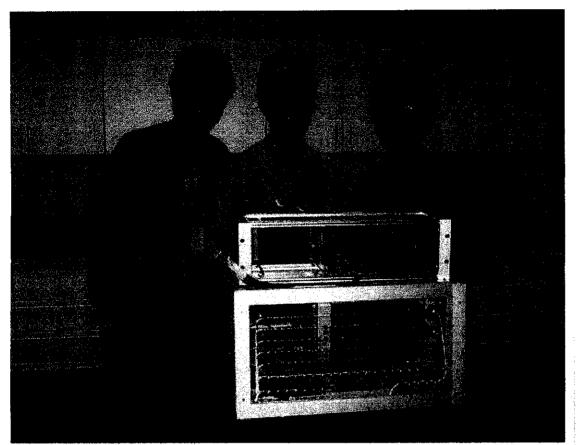

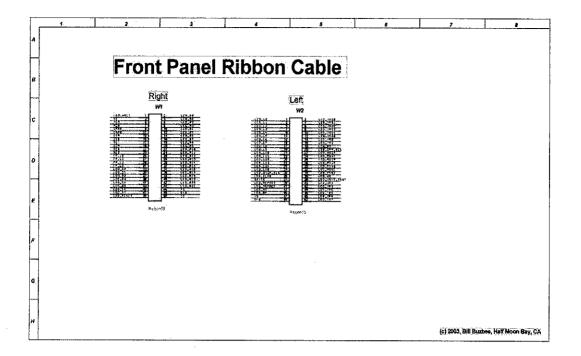

|     | 4.7  | Case and front panel construction          | 35 |

|-----|------|--------------------------------------------|----|

|     | 4.8  | Machine validation suite                   | 35 |

|     | 4.9  | Serial port and terminal interfacing       | 38 |

|     | 4.10 | Performance                                | 40 |

| 5.0 | CON  | CLUSION AND FUTURE WORK                    | 41 |

|     | REFI | ERENCES                                    | 42 |

|     | APPI | ENDICES                                    | 43 |

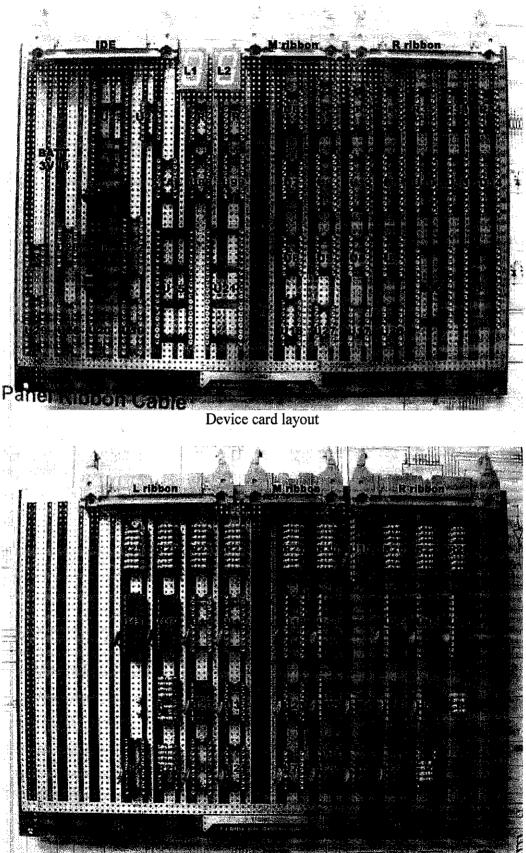

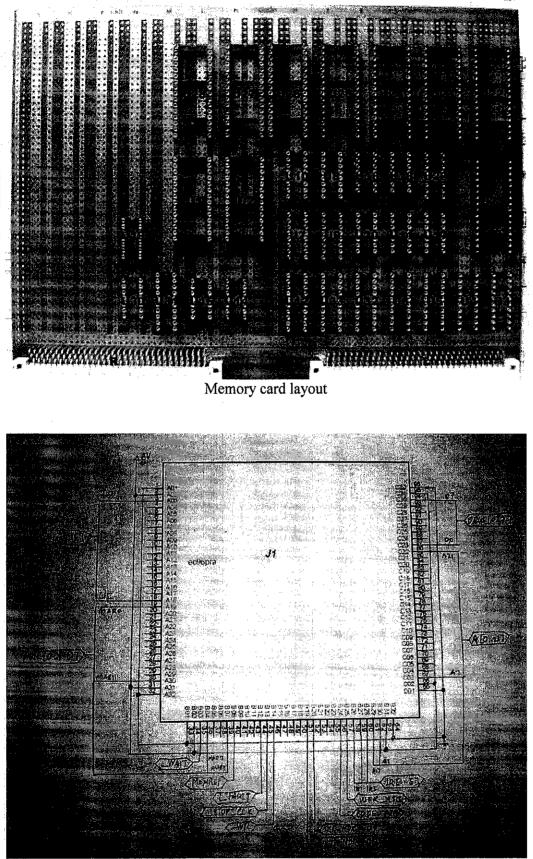

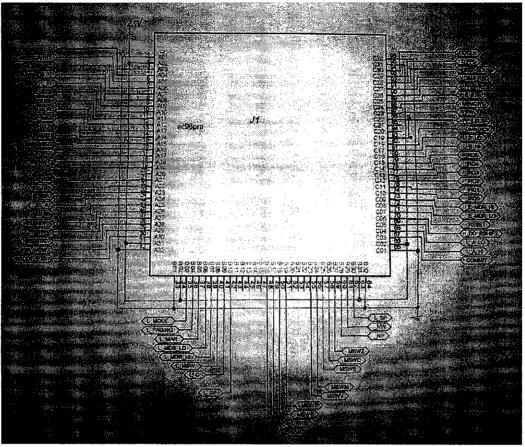

|     | APPE | NDIX I – Board layout and backplane pinout | 51 |

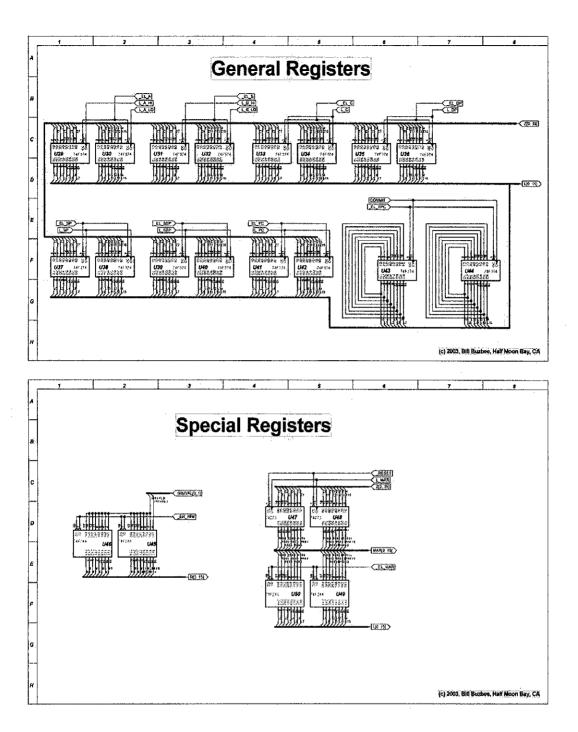

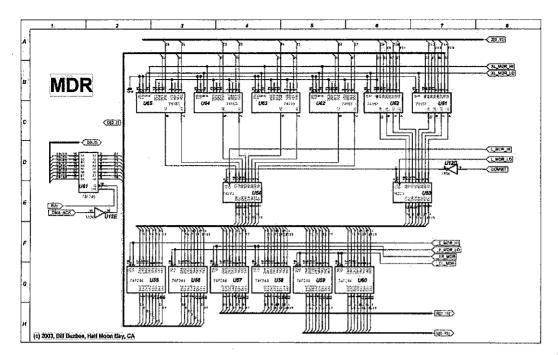

|     | APPE | NDIX II – Schematic diagram                | 54 |

|     | APPE | NDIX III – Microcode listing               | 65 |

v

# LIST OF FIGURES

| Figure 1  | Literature review, Page table                      | 6  |

|-----------|----------------------------------------------------|----|

| Figure 2  | Basic block diagram of the CPU                     | 11 |

| Figure 3  | Control line outputs from the microcode ROM        | 14 |

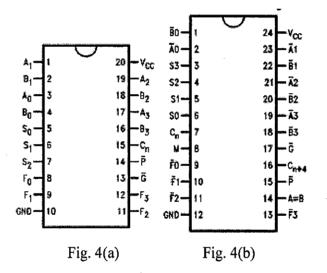

| Figure 4  | Pinout of 74381 and 74181                          | 17 |

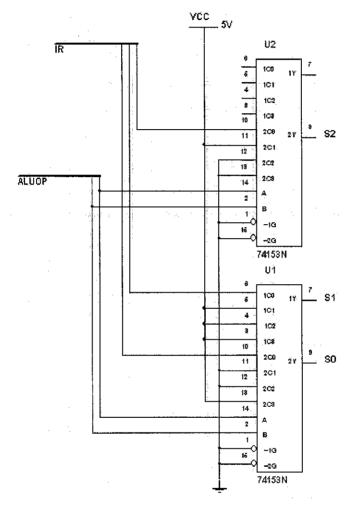

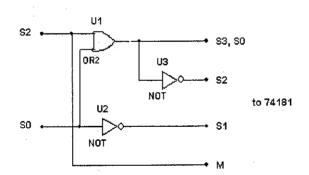

| Figure 5  | Multiplexer circuit to select function for the ALU | 18 |

| Figure 6  | Designed decoding circuit for 74181                | 19 |

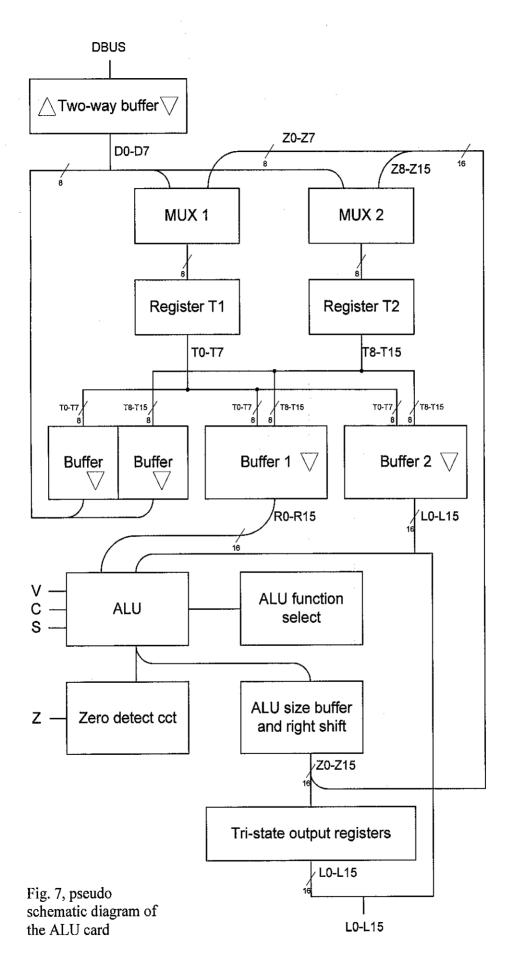

| Figure 7  | Block diagram of the ALU                           | 21 |

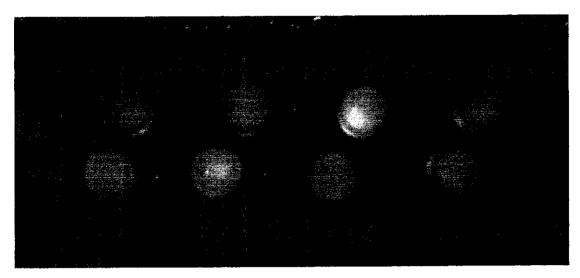

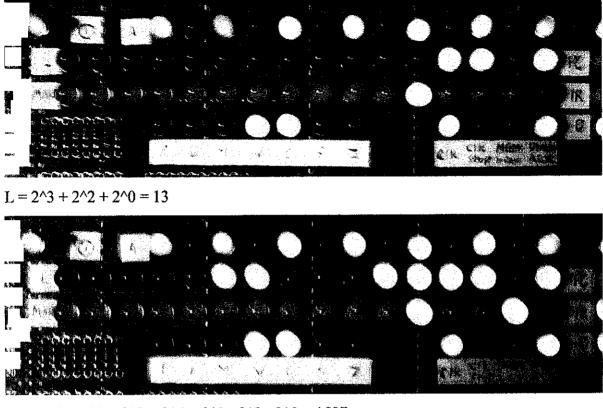

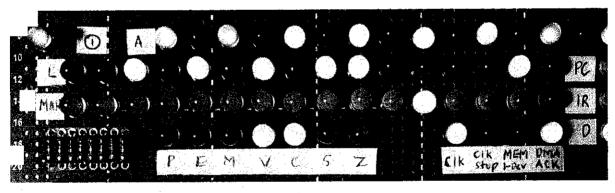

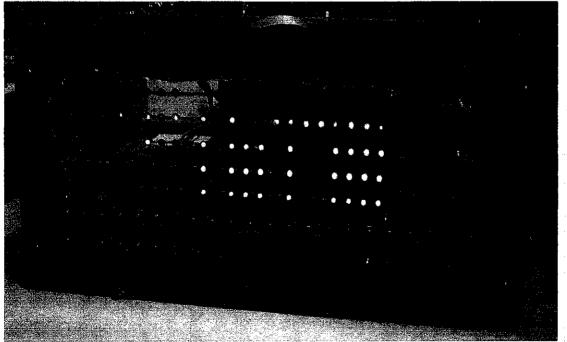

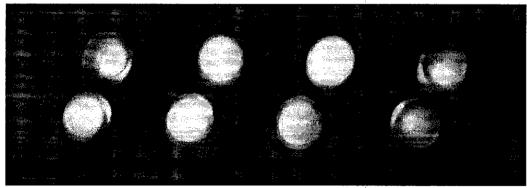

| Figure 8  | Result, LEDs showing L bus content                 | 23 |

| Figure 9  | Result, LEDs showing ALU result through bus L      | 23 |

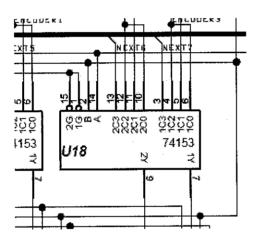

| Figure 10 | Instruction multiplexer                            | 24 |

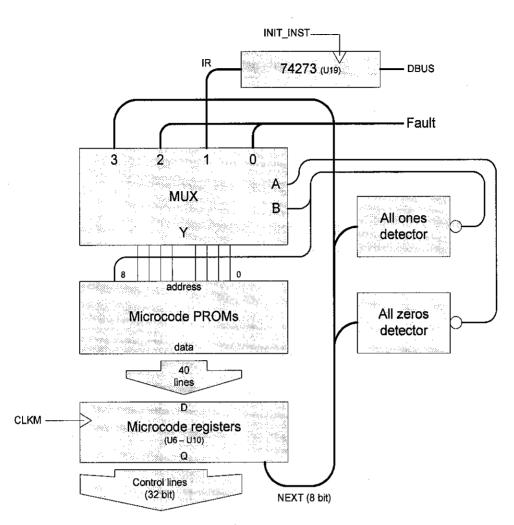

| Figure 11 | Simplified block diagram of microcode sequencer    | 25 |

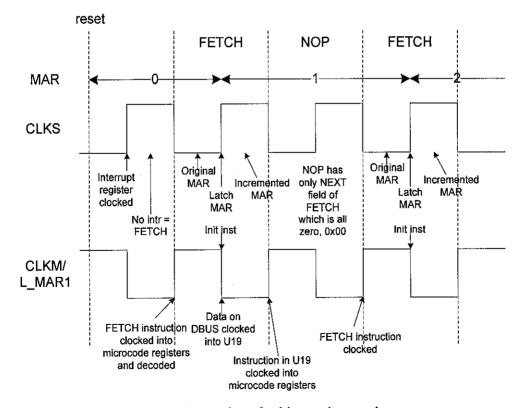

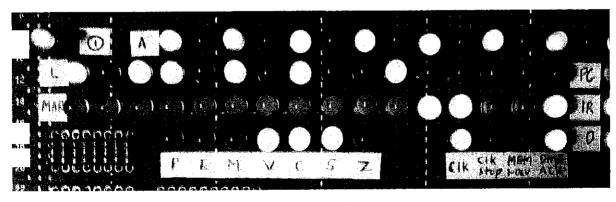

| Figure 12 | Instructions fetching and execution                | 26 |

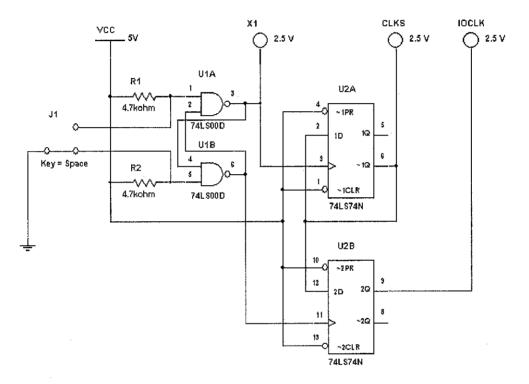

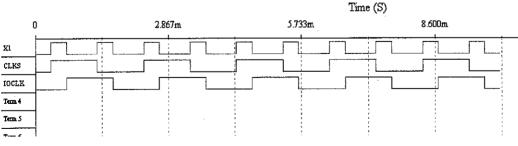

| Figure 13 | Simulated schematic of the clock generator         | 27 |

| Figure 14 | Clocks waveform                                    | 27 |

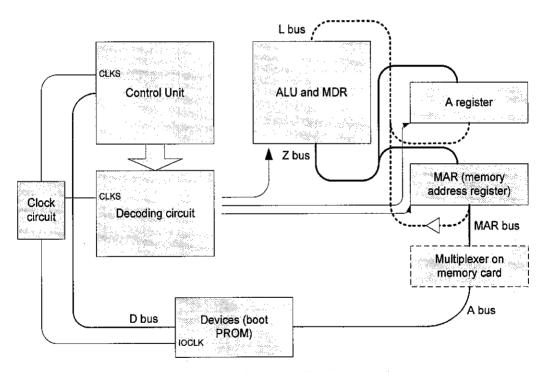

| Figure 15 | Simplified CPU for the given example               | 28 |

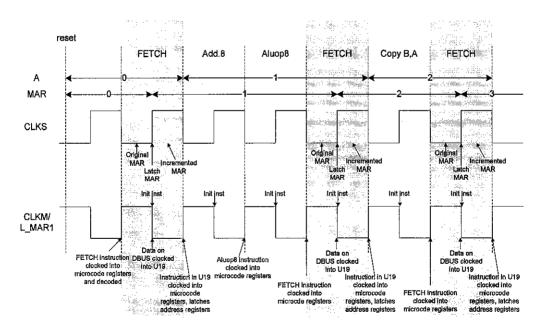

| Figure 16 | Timing diagram for the example                     | 30 |

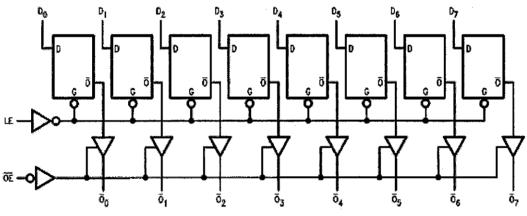

| Figure 17 | 74533 logic diagram                                | 31 |

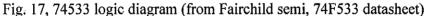

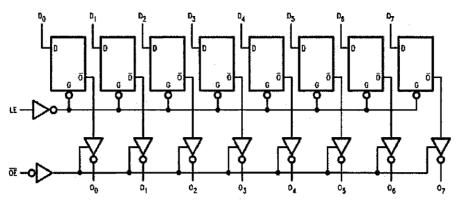

| Figure 18 | 74373 logic diagram                                | 32 |

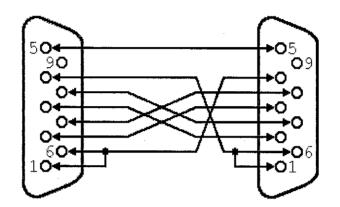

| Figure 19 | Full-handshaking null modem cable connection       | 39 |

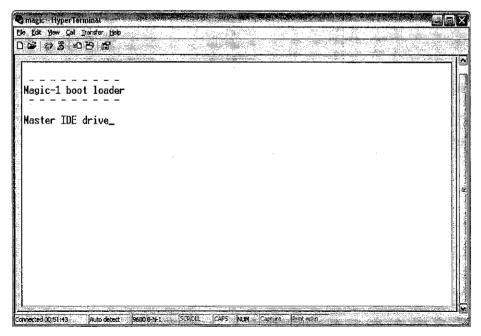

| Figure 20 | Terminal screenshot                                | 39 |

# LIST OF TABLES

| Table 1 | Core topics in computer architecture and organization | 2  |

|---------|-------------------------------------------------------|----|

| Table 2 | MISC field output decoding table                      | 14 |

| Table 3 | ALU operation select table                            | 18 |

| Table 4 | Truth table for decoding control lines for 74181      | 19 |

| Table 5 | Instruction multiplexing table                        | 24 |

| Table 6 | Validation suite summary                              | 35 |

| Table 7 | Magic-1 benchmark                                     | 40 |

# ABBREVIATIONS AND NOMENCLATURES

.

| CSA  | computer system architecture                |

|------|---------------------------------------------|

| UTP  | Universiti Teknologi Petronas               |

| TLB  | translation lookaside buffer                |

| UART | universal asynchronous receiver transmitter |

| TTL  | transistor-transistor logic                 |

| IC   | integrated circuit                          |

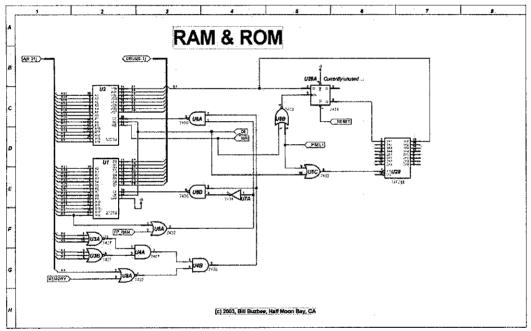

| ROM  | read only memory                            |

| PROM | programmable read only memory               |

| ALU  | arithmetic logic unit                       |

| CPU  | central processing unit                     |

| DMA  | direct memory access                        |

| CD   | compact disc                                |

| RAM  | random access memory                        |

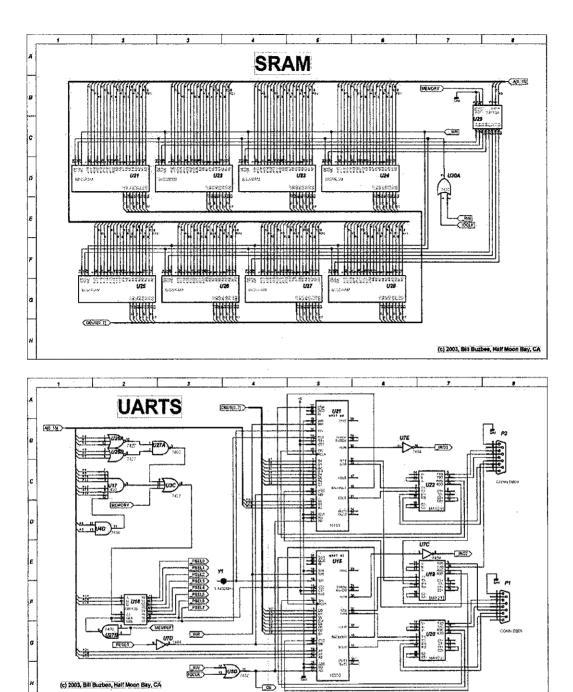

| SRAM | static random access memory                 |

| IR   | instruction register                        |

| MDR  | memory data register                        |

| PTB  | page table base                             |

| MSW  | machine status word                         |

| PC   | program counter                             |

| MAR  | memory address register                     |

| MUX  | multiplexer                                 |

viii

# CHAPTER 1 INTRODUCTION

To many end users, the internal workings parts of a CPU are difficult to comprehend. Computers accelerated economical development as they help to compute and process data in a way which is unachievable by humans. Societies are very dependent on computers that computers had become an essential part of human life. Due to this fact, computers are designed to be more helpful by cramping more features and increasing their capabilities.

#### 1.1 Background

Computer which is controlled by the central processing unit had been already available for years. The exact timeline of computers can be traced back to 1950s by the invention of instruction list which basically list down the operations for an automated machine.

Today, computers like PCs and Macs are capable of delivering high resolution graphics and surround sound which has been taken for granted. How many of the students fully understand the different components like ALU, registers and the controls which are put together for a computer to function correctly? These machines are highly complex and it is a challenge to show how all the different components are assembled to form a functional computer.

#### 1.2 Problem statement

In the view of the previous discussion, teaching Computer System Architecture (CSA) can be quite a challenge as it involves describing a lot of difficult technical details. Technical details in a computer systems course can be presented well by using a

1

suitable teaching platform. This project describes the development of an 8-bit computer using TTL logic gates as a platform to support the teaching of CSA at Universiti Teknologi Petronas (UTP).

One of the goals of the CSA course is to explain the role and interaction of the components of a computer system therefore the teaching platform should have the following features.

1. A simple model architecture, with an easy to teach and learn instruction set

2. An architecture that can easily be used to demonstrate the relationship between different components of a computer system.

3. In addition, the platform should be able to provide the students the opportunity to learn the "ins" and "outs" of a computer system at gate level, which programming simulators does not [1].

A major problem in teaching computer architecture courses is how to help students make the cognitive leap that connects their theoretical knowledge with practical examples [2]. Different educators involved in teaching computer architecture and organization have to resolve this problem using a variety of computer system simulation software [2]. Although these simulators are useful, they however, still do not provide the students the "ins" and "outs" of a computer system.

| , Fundamentals                  | Organization                   | Computer Arithmetic                   | Main Memory                      | Interfacing and                            |

|---------------------------------|--------------------------------|---------------------------------------|----------------------------------|--------------------------------------------|

|                                 | of the CPU                     |                                       |                                  | Communication                              |

| <ul> <li>Registers</li> </ul>   | <ul> <li>Single vs</li> </ul>  | <ul> <li>Representation of</li> </ul> | Memory                           | I/O fundamentals:                          |

| and register                    | multiple                       | integers (signed,                     | hierarchies                      | handshaking,                               |

| file                            | bus                            | unsigned)                             | <ul> <li>Main memory</li> </ul>  | buffering                                  |

| <ul> <li>Data types</li> </ul>  | datapaths                      | Basic arithmetic                      | organization                     | • I/O techniques:                          |

| Instruction                     | <ul> <li>Pipelined,</li> </ul> | algorithms for                        | <ul> <li>Latency,</li> </ul>     | programmed I/O,                            |

| types                           | non-                           | integer addition,                     | bandwidth, cycle                 | interrupt driven, DMA                      |

| <ul> <li>Addressing</li> </ul>  | pipelined                      | subtraction,                          | time, performance                | <ul> <li>Interrupt structures:</li> </ul>  |

| modes                           | Control                        | multiplication, and                   | Virtual memory                   | vectored and                               |

| <ul> <li>Instruction</li> </ul> | unit:                          | division                              | system                           | prioritized, interrupt                     |

| formats                         | hardwired                      | <ul> <li>Representation of</li> </ul> | <ul> <li>Cache memory</li> </ul> | overhead, interrupts                       |

| • Fetch,                        | vs.                            | real numbers                          | <ul> <li>Memory</li> </ul>       | and re-entrant code.                       |

| decode,                         | microprogr                     | Basic arithmetic                      | interleaving                     | <ul> <li>Buses: clock, control,</li> </ul> |

| execution                       | ammed                          | algorithms for                        | <ul> <li>Memory</li> </ul>       | address and data                           |

| cycles                          | realization                    | operations on real                    | technologies                     | busses, arbitration                        |

| • I/O         | <ul> <li>Arithmetic</li> </ul> | numbers                         | (SRAM,                          | DRAM, | <ul> <li>Parallel</li> </ul> | and | serial |

|---------------|--------------------------------|---------------------------------|---------------------------------|-------|------------------------------|-----|--------|

| techniques    | units                          | <ul> <li>Conversions</li> </ul> | EPROM, Fia                      | ash)  | interface                    | s   |        |

| and interrupt | implementa                     | between real and                | <ul> <li>Reliability</li> </ul> | and   | <ul> <li>Timers</li> </ul>   |     |        |

|               | tion                           | integer numbers                 | error corre                     | ction |                              |     |        |

Table 1, Core topics in computer architecture and organization

### 1.3 Objective and scope of study

As mentioned earlier, the objective of this project is to develop an 8-bit computer using TTL gates as a platform to support teaching CSA in UTP. This project is relevant as it only requires basic knowledge of digital systems and microprocessors. A good working knowledge on digital circuits and practical electrical issues is required though because circuits in a discrete processor may become complicated and requires a lot debugging.

In time frame point of view, the project is viewed feasible as there is no major designing involved. The scope of the project is to build and debug the CPU until it works as intended and in the process attaining full comprehension of it.

Scope of the project:

- Build and test

- The ALU and registers

- o The control and instruction sequencing circuit

- o Memory circuit

- o Clocks

- Devices (Boot ROM, serial ports)

- Optional

- Assembler and

- o C compiler

# CHAPTER 2 LITERATURE REVIEW

A microprocessor executes a collection of machine instructions that tell the processor what to do. Based on the instructions, a microprocessor performs three basic operations.

Using its ALU (Arithmetic/Logic Unit), a microprocessor can perform mathematical operations like addition, subtraction, multiplication and division. Modern microprocessors contain complete floating point processors that can perform extremely sophisticated operations on large floating point numbers. A microprocessor can move data from one memory location to another and a microprocessor can make decisions and jump to a new set of instructions based on those decisions.

There may be very sophisticated things that a microprocessor does, but those are its three basic activities. Other than that, microprocessor comprises of registers as temporary storage area, buses to transport data and select memory areas and control lines to control all the blocks inside the microprocessor so that the instruction are executed correctly [3].

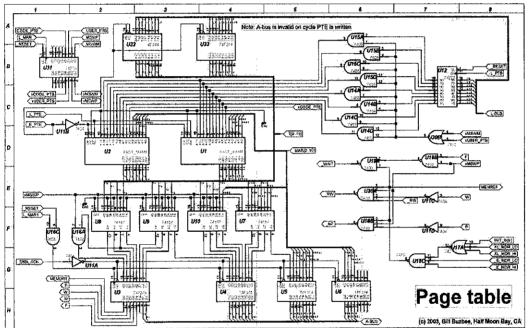

#### 2.1 Page table

A page table is the data structure used by a virtual memory system in a computer operating system to store the mapping between virtual addresses and physical addresses. Virtual addresses are those unique to the accessing process. Physical addresses are those unique to the CPU, i.e., RAM.

Say we have a computer architecture where the word size is 32 bits. This means we are able to form addresses from 0x00000000 to 0xffffffff - spanning 4GB. These

4

addresses form what is called as the *virtual address space*. These addresses have no physical meaning - if we only have 16MB of memory, all addresses above 0x01000000 would be invalid. However, as mentioned, almost all programs do not use all 4GB of memory when a program runs, but only parts of it at a time. For example, the text, data, and stack segments may only be used and together only take 1 megabyte in total over the time where it runs.

The chunks as mentioned above are called special names. This 4GB virtual address space is split up into chunks, commonly 4K in size, called *pages*. The physical memory is also split up into chunks, also commonly 4K in size, called *frames*. A program's text segment might start at the virtual address 0x00000004 - page number 0x0, and offset 0x4, but in reality, this may correspond to the physical address 0xff0e0004 - frame number 0xff0e, and offset 0x4. What the virtual memory system does is convert virtual addresses into physical addresses, essentially, mappings between pages and frames. The page table is used for this purpose.

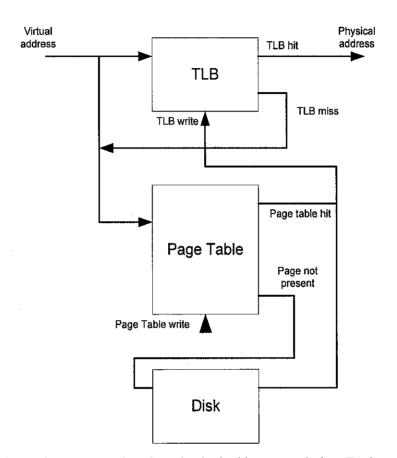

Many architecture also have direct hardware support for virtual memory, providing what is known as a translation lookaside buffer (TLB), which is filled with page-frame mappings initially, and instead of having the virtual memory system entirely in software, when the hardware looks up a memory address and does the page-frame translation, which gains us a performance increase.

However, the TLB can only hold a fixed number of page-frame mappings. It is the job of the virtual memory system to extend this into software, and to hold extra page-frame mappings. The virtual memory system does so by means of a page table [4].

#### 2.1.1 Role of the page table

Assuming a program is running and it tries to access memory in the virtual address 0xd09fbabe. The virtual address is broken up into two: 0xd09f is the page number and 0xbabe is the offset, within the page 0xd09f.

With hardware support for virtual memory, the address is looked up within the TLB. The TLB is specifically designed to perform this lookup in parallel, so this process is extremely fast. If there is a match for page 0xd09f within the TLB (a TLB hit), the physical frame number is retrieved, the offset replaced, and the memory access can continue. However, if there is no match (called a TLB miss), the second port-of-call is the page table.

Fig. 1, Actions taken upon a virtual to physical address translation. Each translation is restarted if a TLB miss occurs, so that the lookup can occur correctly through hardware [4].

When the hardware is unable to find a physical frame for a virtual page, it will generate a processor interrupt called a page fault. Hardware architectures offer the chance for an interrupt handler to be installed by the operating system to deal with such page faults. The handler can look up the address mapping in the page table, and can see whether a mapping exists in the page table. If one exists, it is written back to the TLB, as the hardware accesses memory through the TLB in a virtual memory system, and the faulting instruction is restarted, with the consequence that the hardware will look in the TLB again, find the mapping, and the translation will succeed.

However, the page table lookup may not be successful for two reasons:

- there is no translation available for that address the memory access to that virtual address is thus bad or invalid, or

- the page is not resident in physical memory (it is full).

In the first case, the memory access is invalid, and the operating system must take some action to deal with the problem. On modern operating systems, it will send a segmentation fault to the offending program. In the second case, the page is normally stored elsewhere, such as on a disk. To handle this case, the page needs to be taken from disk and put into physical memory. When physical memory is not full, this is quite simple, one simply needs to write the page into physical memory, modify the entry in the page table to say that it is present in physical memory (see the next section), write the mapping into the TLB and restart the instruction.

However, when physical memory is full, and there are no free frames available, pages in physical memory may need to be swapped with the page that needs to be written to physical memory. The page table needs to be updated to mark that the pages that were previously in physical memory are no longer so, and to mark that the page that was on disk is no longer so also (and to of course write the mapping into the TLB and restart the instruction). This process of swapping pages between physical memory and disk is known sometimes as, obviously, swapping (though the term is sometimes used to describe swapping entire processes). This process however is extremely slow in comparison to memory access via the TLB or even the page table, which lies in physical memory. Which page to swap is the subject of page replacement algorithms [4].

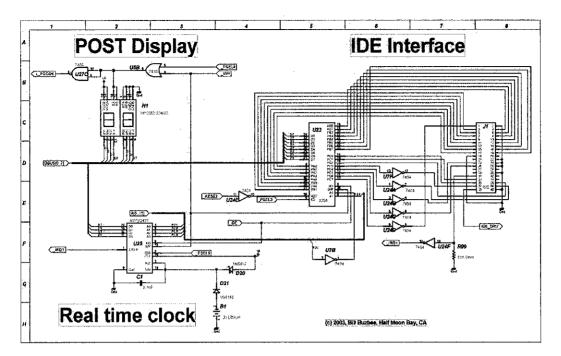

#### 2.2 Universal asynchronous receiver transmitter

A UART or Universal Asynchronous Receiver-Transmitter is a piece of computer hardware that translates between parallel bits of data and serial bits. A UART is

usually an integrated circuit used for serial communications over a computer or peripheral device serial port. UARTs are now built into some microcontrollers (for example, PIC16F877).

Bits have to be moved from one place to another using wires or some other medium. Over many miles, the expense of the wires becomes large. To reduce the expense of long communication links carrying several bits in parallel, data bits are sent sequentially, one after another, using a UART to convert the transmitted bits between sequential and parallel form at each end of the link. Each UART contains a shift register which is the fundamental method of conversion between serial and parallel forms.

By convention, teletype-style UARTs send a "start" bit, five to eight data bits, leastsignificant-bit first, an optional "parity" bit, and then a "stop" bit. The start bit is the opposite polarity of the data-line's normal state. The stop-bit is the data-line's normal state, and provides a space before the next character can start. In mechanical teletypes, the "stop" bit was often stretched to two bit times to give the mechanism more time to finish printing a character. A stretched "stop" bit also helps resynchronization. The parity bit can either make the number of bits odd, or even, or it can be omitted. Odd parity is more reliable because it assures that there will always be a data transition, and this permits many UARTs to resynchronize.

Speeds for UARTs are in bits per second (bit/s or bps), although often incorrectly called the baud rate. Standard mechanical teletype rates are 45.5, 110, and 150 bit/s. Computers have used from 110 to 230,400 bit/s. Standard speeds are 110, 300, 1200, 2400, 4800, 9600, 19,200, 28,800, 38,400, 57,600, and 115,200 bit/s.

The UART usually does not directly generate or receive the voltage levels that are put onto the wires interconnecting different equipment. An interface standard is used, which defines voltage levels and other characteristics of the interconnection. Examples of interface standards are EIA, RS 232, RS 422 and RS 485. Depending on the limits of the communication channel to which the UART is ultimately connected, communication may be "full duplex" (both send and receive at the same time) or "half duplex" (devices take turns transmitting and receiving). Beside traditional wires, the UART is used for communication over other serial channels such as an optical fiber, infrared, wireless Bluetooth in its Serial Port Profile (SPP) and the DC-LIN for power line communication.

Today (2006), UART is commonly used with RS232 for embedded systems communications. It is useful to communicate between microcontrollers and also with PCs. Many chips provide UART functionality in silicon, and low cost chips exist to convert UART to RS232 signals (for example, Maxim MAX232) [4].

#### 2.2.1 Synchronous

The word "asynchronous" indicates that UARTs recover character timing information from the data stream, using designated "start" and "stop" bits to indicate the framing of each character. In synchronous transmission, the clock data is recovered separately from the data stream and no start/stop bits are used. This improves the efficiency of transmission on suitable channels; more of the bits sent are data. An asynchronous transmission sends nothing over the interconnection when the transmitting device has nothing to send; but a synchronous interface must send "pad" characters to maintain synchronism between the receiver and transmitter. The usual filler is the ASCII "SYN" character. This may be done automatically by the transmitting device.

Some chips have both synchronous and asynchronous modes. These are called USARTs (for "universal synchronous asynchronous receiver-transmitters") [4].

# CHAPTER 3 METHODOLOGY

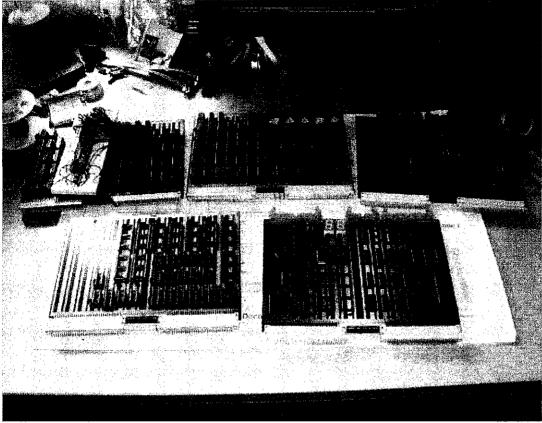

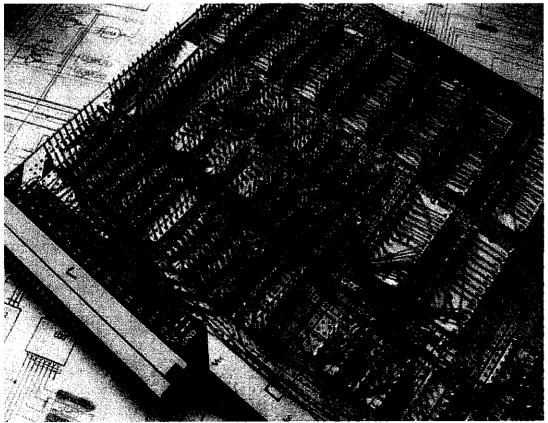

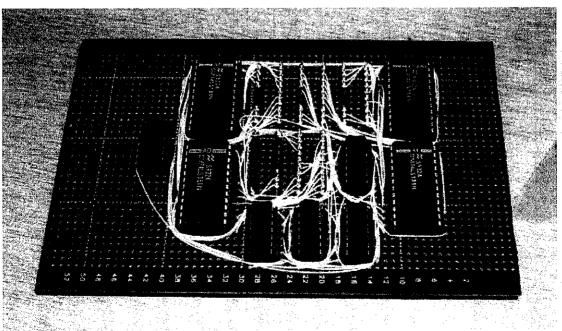

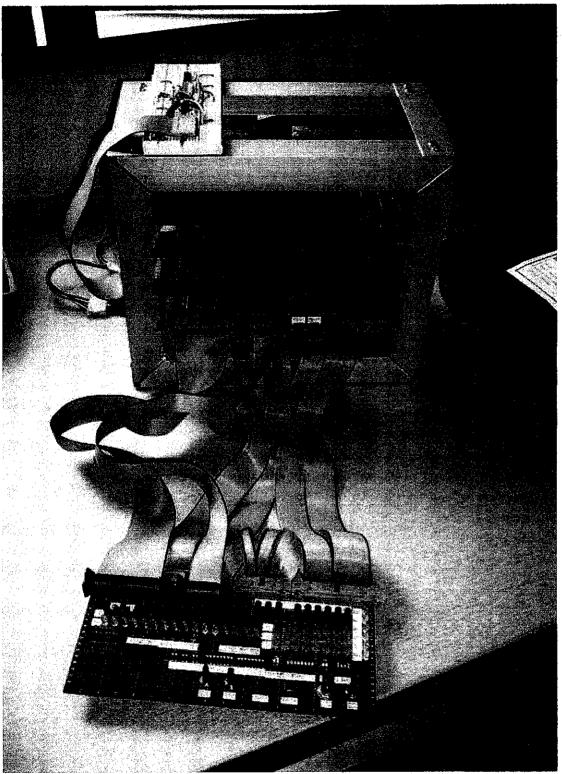

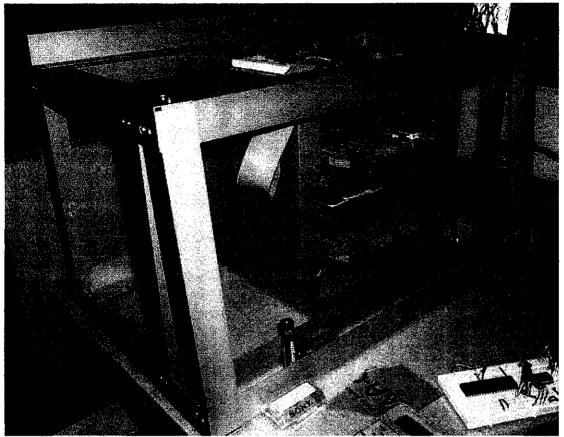

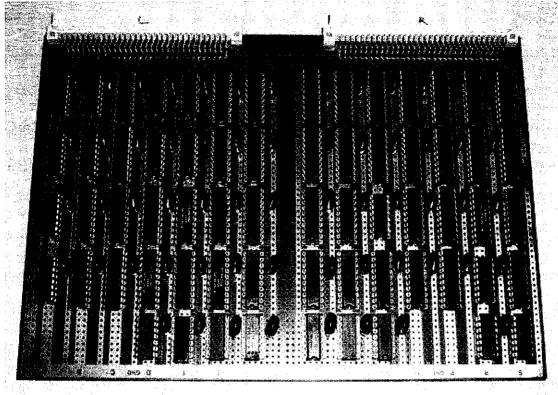

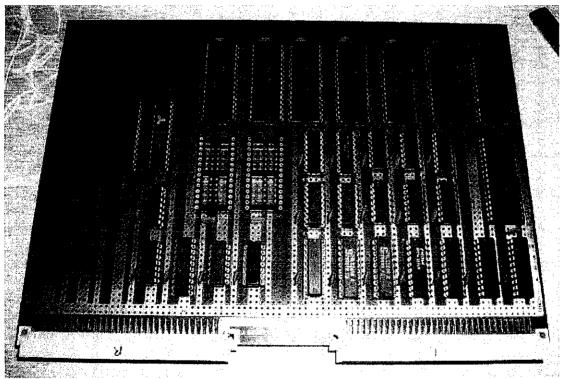

Identified this project as a development project following the scheme created by the CPU designer, the CPU will solely be developed using TTL logic ICs. These logic ICs are the common digital ICs which are available at the everyday electronic stores. As the project will need hundreds of digital ICs, wire wrapping technique is viewed as the most feasible technique because it offers flexibility in construction and it can be easily reworked during debugging. Wire wrapping is also preferred because it is a fast prototyping method for circuit without the time required for designing printed circuit board.

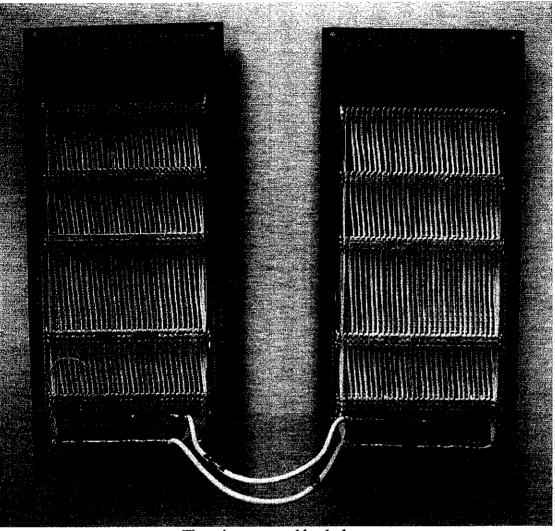

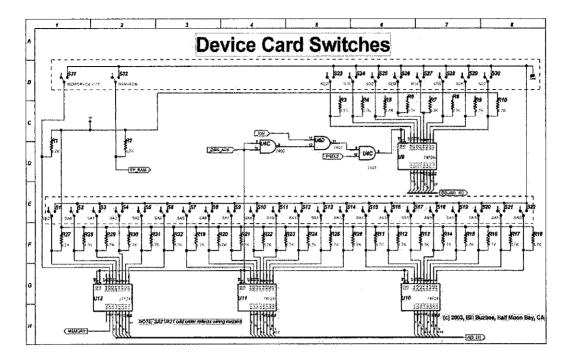

Parts of the CPU will be divided into functional parts to be mounted on several boards and later combined on a rack allowing easy access to panels and input output ports for extension. As was designed, the CPU is concatenated to a few parts installed in cards form; there are the ALU/register, control, memory, device and front panel card. These cards not only simplifies construction process but also help to ease project management as construction can be done card by card ensuring all developed cards are working before merging them together to be the CPU.

On the software side of the CPU, the assembler is needed to assemble program written for the machine and ROM burner would be needed to write PROM which stores the microcode for instruction execution. Other required hardware would be external hard disk to store larger program and a power supply to power up the CPU.

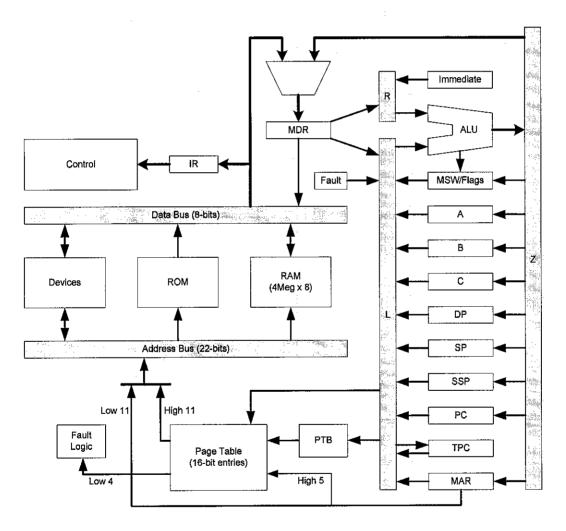

#### 3.1 OVERVIEW

Designed machine is an 8-bit machine with the ability to run 8-bit or 16-bit arithmetic and logic operation. The 8-bit specification comes from the 8-bit data bus width. Two length of operation are supported indicates that the ALU can run two different operand word sizes.

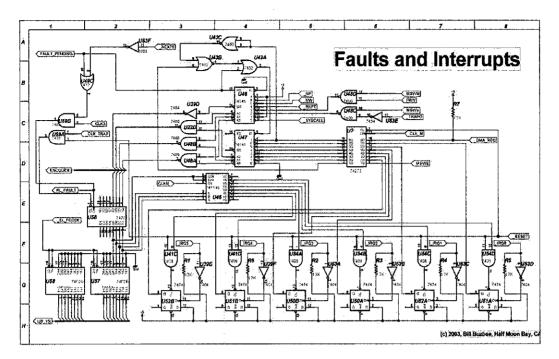

Bit and byte order of the machine is big endian where most significant bit is numbered as zero and stored first in the memory. External interrupts and DMA is supported.

(redrawn from: www.homebrewcpu.com)

Fig. 2, Basic block diagram of the CPU

#### 3.2 INSTRUCTION SET ARCHITECTURE

#### 3.2.1 Operand Addressing

The machine was initially designed to be a pure one address computer. But in the design process, the operand addressing mode was slowly converted into a mixed mode with registers from accumulator was renamed to register A and other smaller details for easier compiling. So the operand addressing is not consistent throughout making this computer not an orthogonal machine.

There are nine visible register in the machine which are:

A - Accumulator. Can be addressed as 8 or 16 bits. Implied target of most operations and also used as a general load/store base register and memop operand.

B - General load/store base register, plus source operand of ALU ops and memops and target of some loads. Can also addressed as 8 or 16 bits

C - Special-purpose count register for block moves and variable shifts.

MSW - (machine status word/flags) Alu flags: Carry, Zero, Sign and oVerflow. Control flags: Mode (0 for supervisor, 1 for user), Paging enable and EI (Enable Interrupts). Also, following a memory fault, a status bit, Data, will appear in the saved MSW describing whether the faulting address was referencing the code or data portion of the page table.

DP - Global data pointer. Most data references are relative to a base.

SP - Stack pointer. Always pushes and pop 16 bits at a time (though doesn't need to be aligned).

SSP - Supervisor stack pointer. Used when in supervisor mode.

PC - Program Counter

PTB - Base of page table for current process in user mode. Supervisor mode base is hardwired to 0x0000. Note that the address refers to the special page table memory - not main memory.

#### 3.2.2 Addressing mode

The available memory addressing modes are:

Register Indirect with offset - uint8(A) and uint8(B) Frame local with offset - uint8(SP) and uint16(SP) Global with offset - uint16(DP) Immediate - (PC++) Push - (--SP) Pop - (SP++)

#### 3.3 Microcode

The microcode is stored in five 512x8 bit ROM. The lower half will store the starting microcode while the upper half contains the continuation microcode. Since this machine is not a single cycle computer, there will be a continuation or more instructions after an initial instruction. The redirection to the next microcode index in the microcode ROM is control by the first eight bit of the microcode store. This eight bit contains exact memory location where the next instruction is positioned.

With 5 ROMs with each having a byte to contribute to the control line, there is a total of 40 control lines out from the microcode store. There are a total of 256 different instructions available as the lower half is filled with initial microcode and the ROM is 512 words in size. Full microcode listing can be found in Appendix III. The continuation microcode address of nine bits is made possible by an encoding circuit which detects the contents of NEXT field. When the NEXT field contains value but not all ones, it will become the most significant bit for the full 9-bit microcode address.

Some encoding circuit is responsible for the redirection of fetch instruction that is when the NEXT field is all ones. The circuit selects the buffering of IR (instruction register) from the DBUS into the address of the ROMs – study in further chapter.

| U1                                                                                  | U2                                      | U3                                                               | U4                                                                             | U5                                                          |

|-------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|

| aluop sz<br>aluop 1<br>aluop0<br>cany<br>L_size<br>br_sense<br>user_ptb<br>code_ptb | e_1<br>e_1<br>e_1<br>numval1<br>immval0 | e_mdrhi<br>priv<br>L_mode<br>L_paging<br>misc3<br>misc2<br>misc1 | iatch3<br>iatch2<br>latdh1<br>latch0<br>l_mar<br>L_mdrlo<br>L_mdrlo<br>L_mdrlo | next7<br>next6<br>next5<br>next4<br>next2<br>next2<br>next1 |

Fig. 3, Control lines (output) from the five ROMs

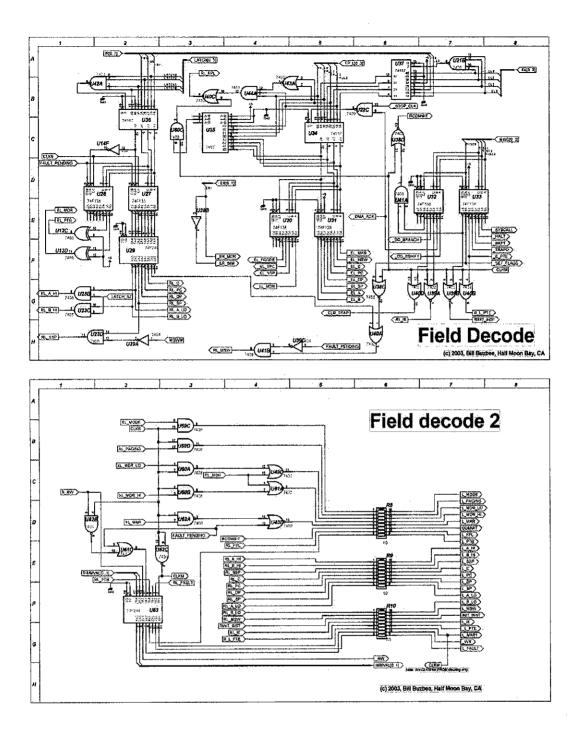

Outputs from the ROMs as in Figure 3 feed directly to a field decoding logic circuit decoding the outputs to discrete control lines. This is best as the registers are tri-state output registers so by encoding the controls we can keep a fairly safe bus driving scheme. As we know that no more than one driver should drive a bus. The decoding also minimizes amount of control lines as can be observed LATCH filed is a four bit output where we can select up to 16 registers to be latched.

Furthermore, some of the conditions do not occur at the same time. Such as a branch instruction does not need to do a right shift to the ALU result at the same time so does the right shift instruction. This furthermore reduces the number of control line width but with the cost of decoding circuit. Control field which adopt this concept is the MISC field which encode control signals which never occur at the same time.

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| Antes Sec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 H                       |

| attern 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | halt                      |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tran on overflow          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | trap on overflow          |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | latch PTE                 |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | set flags (from alu op)   |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | init_inst (clear          |

| 1. Solution of the second s | •                         |

| 8 ₹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | right shift ALU output    |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DMA acknowledge           |

| a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | latch MSW [le] (interrupt |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | enable)                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                         |

| <b>9</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | do branch                 |

| Contraction of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | latch MSW[in_trap]        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | commit state              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Comme State               |

| e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |