# EVALUATION ANALYSIS OF CONTROL LOOP FEEDBACK SYSTEMS IN RESONANT NETWORK OF THE ISOLATED DC-DC CONVERTER DESIGN

By

#### **EMY AZLIZA BT ROPLI**

#### FINAL PROJECT REPORT

Submitted to the Electrical & Electronics Engineering Programme

in Partial Fulfillment of the Requirements

for the Degree

Bachelor of Engineering (Hons)

(Electrical & Electronics Engineering)

Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2006 by Emy Azliza bt. Ropli, 2006

### **CERTIFICATION OF APPROVAL**

# EVALUATION ANALYSIS OF CONTROL LOOP FEEDBACK SYSTEMS IN RESONANT NETWORK OF THE ISOLATED DC-DC CONVERTER DESIGN

by

Emy Azliza binti Ropli

A project dissertation submitted to the

Electrical & Electronics Engineering Programme

Universiti Teknologi PETRONAS

in partial fulfilment of the requirement for the

Bachelor of Engineering (Hons)

(Electrical & Electronics Engineering)

Approved:

Project Supervisor

UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

December 2006

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Emy Azliza bt Ropli

#### **ABSTRACT**

The existing output of the isolated DC-DC Converter requires a good switching device and needs to be controlled in order to achieve the desired output voltage with less output ripple voltage. However, this converter cannot maintain the output voltage with good efficiency in high power application. Currently, any semiconductor devices need greater efficiency in switching such as high power switching power supply, motor drives for electrical vehicle (EV), communication systems and others. A new DC-DC Converter modified via resonant network and controlled with the application of controller and gate circuit is proposed. The PWM Controller technique is used to control the output voltage and duty cycle of the switches. The paper will cover studies on the Zero-Current Switching circuit design and PWM controller in isolated DC-DC Converter. Then, the simulation using Cadence Pspice is carried out. The performance of the design will be evaluated based on parameters such as input ripple current, output ripple voltage and efficiency. A control loop feedback systems in resonant network of the FB-ZCS with better efficiency, less input ripple current of 1.94% and less output ripple voltage of 0.47% are obtained from this project. But, the results obtained cannot be compared with the conventional scheme because of big differences and suggestions have been made for the improvement.

#### **ACKNOWLEDGEMENTS**

My utmost gratitude and appreciation goes to my supervisor, for being there to guide me throughout the semester as supervisor. He worked hard to get me through the researching process, results of stimulation and also for his effort to review and verify this report. Without his help and suggestions, this research will not possibly achieve this far.

My appreciation to other lecturers, who gave some opinions towards this project. Also to our lab technician, my thankfulness goes to you for being kind enough to provide effort and guidance during my familiarization stage of Cadence software.

Though works still have to be done in order to complete this research and design, without help and support from these people and blessing from God, the project might not even be completed.

# TABLE OF CONTENTS

| LIST OF TABLES    |                             | ix  |

|-------------------|-----------------------------|-----|

| LIST OF FIGURES   | •••••                       | x   |

| LIST OF ABBREVIAT | IONS                        | xii |

| CHAPTER 1 INTRODU | JCTION                      | 13  |

| 1.1 Backg         | round of Study              | 13  |

| 1.2 Proble        | em Statement                | 14  |

| 1.2.1 H           | Problem Identification      | 14  |

| 1.2.2 \$          | Significance of Project     | 15  |

|                   | tives and Scope Of Study    |     |

|                   | Objectives                  |     |

| 1.3.2 \$          | Scope of Study              | 16  |

|                   | URE REVIEW/THEORY           |     |

| 2.1 DC-D          | C Converter                 | 17  |

| 2.2 Full-F        | Bridge Boost Converter      | 19  |

| 2.2.1 1           | Resonant Network            | 20  |

| 2.2.2 1           | Modes of Operation          | 21  |

| 2.3 Feedb         | ack Controller              | 25  |

| CHAPTER 3 METHOL  | OOLOGY/PROJECT WORK         | 30  |

| 3.1.1             | Research and Study          | 31  |

| 3.1.2             | Design and Simulation       | 32  |

| 3.1.3             | Performance Analysis        | 34  |

| 3.1.4             | Data Comparison             | 34  |

| CHAPTER 4 RESULTS | S/DISCUSSION                | 35  |

| 4.1 Findi         | ng and Discussion           | 35  |

| 4.2 Evalu         | ation                       | 39  |

| 4.2.1             | % output ripple voltage     | 39  |

| 4.2.2             | % input ripple current      | 41  |

| 4.2.3             | Efficiency and power losses | 42  |

| 4.2.4             | Load Current                | 45  |

| 4.3 Discu         | ssion                       | 46  |

| CHAPTER 5 CONCLU  | ISION AND RECOMMENDATION    | 47  |

| 5.1 Conclusion                                                            | 47 |

|---------------------------------------------------------------------------|----|

| 5.2 Recommendation                                                        | 47 |

| HAPTER 6 REFERENCES                                                       | 48 |

| Appendix A Conventional Scheme (DC-DC Converter with Feedback Controller) |    |

| Appendix B DC-DC Converter with PWM Controller                            | 52 |

| Appendix C Gantt Chart for First Semester                                 | 53 |

| Appendix D Gantt Chart for Second Semester                                | 54 |

| Appendix E Datasheet for MOSFET (IRF 520)                                 | 55 |

| Appendix F Datasheet for POWER DIODE (D1N5402)                            | 57 |

| Appendix G Datasheet for POWER DIODE (BAL74)                              | 58 |

# LIST OF TABLES

| Table 1 Expected result for the project | 34 |

|-----------------------------------------|----|

| Table 2 Component Rated                 | 34 |

# LIST OF FIGURES

| Figure 1 DC-DC converter connected with PWM controller                                                                                                             | 14   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2 Buck Converter                                                                                                                                            | 17   |

| Figure 3 Boost Converter                                                                                                                                           | 18   |

| Figure 4 Buck-Boost Converter                                                                                                                                      | 18   |

| Figure 5 Conventional Full-Bridge Boost Converter                                                                                                                  | 19   |

| Figure 6 LC Circuit Diagram                                                                                                                                        | 20   |

| Figure 7 Resonant Boost Converter                                                                                                                                  | 21   |

| Figure 8 Operation of Mode I                                                                                                                                       | 22   |

| Figure 9 Operation of Mode II                                                                                                                                      | 23   |

| Figure 10 Operation of Mode III                                                                                                                                    | 24   |

| Figure 11 Operation of Mode IV                                                                                                                                     | 24   |

| Figure 12 Operation of Mode V                                                                                                                                      | 25   |

| Figure 13 Power Circuit of the single phase PFC rectifier [16]                                                                                                     | 26   |

| Figure 14 Ripple Detection Control Method [19]                                                                                                                     | 28   |

| Figure 15 Flowchart of the methodology use in this project                                                                                                         | 30   |

| Figure 16 Block diagram of the design                                                                                                                              | 31   |

| Figure 17 Isolated DC-DC Converter                                                                                                                                 | 32   |

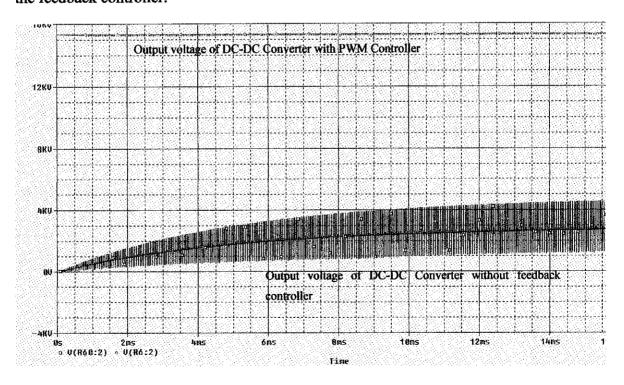

| Figure 18 Waveform of $V_{out}[V(R60:2)]$ of conventional scheme and $V_{out}[V(R6:2)]$ the design                                                                 |      |

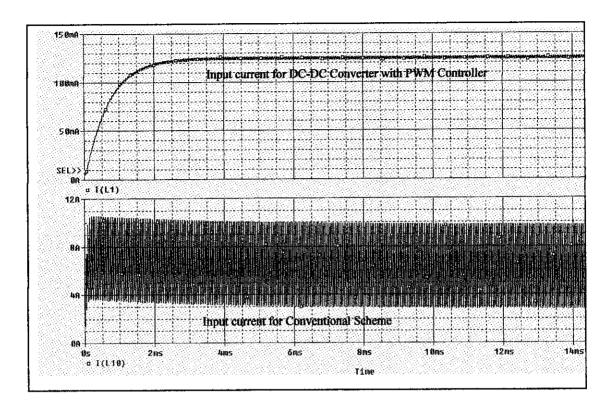

| Figure 19 Waveform of I [I(L1)] of DC-DC Converter with feedback controller waveform of I [I(L10)] of conventional scheme                                          |      |

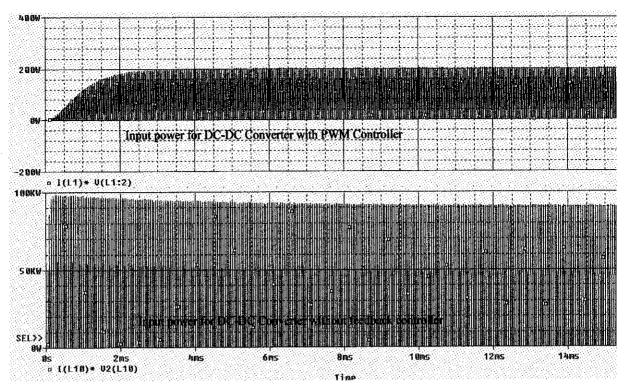

| Figure 20 Maximum and minimum value of $P_{in}[I(L1)*V(L1:2)]$ of convention scheme $P_{in}[I(L10)*V(L10)]$ of DC-DC Converter with feedback controller            |      |

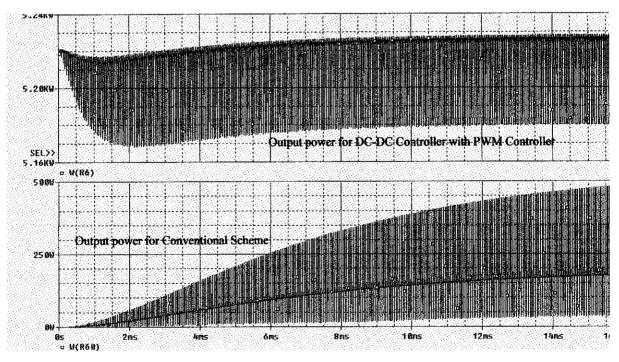

| Figure 21 Maximum and minimum value of P <sub>out</sub> [W(R60)] of conventional sch<br>P <sub>out</sub> [W(R6)] of DC-DC Converter with feedback controller       |      |

| Figure 22 Waveform of V <sub>out</sub> [V(R60:2)] of conventional scheme and V <sub>out</sub> [V(R6:2) DC-DC Converter with PWM controller                         |      |

| Figure 23 Waveform of I [I(L1)] of DC-DC Converter with PWM controller waveform of I [I(L10)] of conventional scheme (DC-DC Converter with feedback controller).   | hout |

| Figure 24 Maximum and minimum value of P <sub>in</sub> [I(L1)*V(L1:2)] of convention scheme P <sub>in</sub> [I(L10)*V(L10)] of DC-DC Converter with PWM Controller |      |

| Figure 25 Maximum and minimum value of Pout [W(R60)] of conventional sch                                                                                           |      |

| Pout [W(R6)] of DC-DC Converter with PWM Controller                                                                                                                | 43   |

| Figure 26 Waveform of load current of DC-DC Controller with PWM Controller | and  |

|----------------------------------------------------------------------------|------|

| waveform for load current of conventional scheme                           | . 45 |

### LIST OF ABBREVIATIONS

ZVS Zero-Voltage Switching

ZCS Zero-Current Switching

PWM Pulse Width Modulation

DC Direct Current

MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor

FB-ZCS Full-Bridge Zero-Current Switch

FB-ZVS Full-Bridge Zero-Voltage Switch

IEEE International Electrical Electronic Engineering

RC Network Resistor Capacitor Network

# CHAPTER 1 INTRODUCTION

### 1.1 Background of Study

High voltage DC-DC converters are widely used in different types of electronic equipment [1]. However, the design of high voltage DC-DC converters is problematic because the output of these converters cannot be controlled to its desired output. Basically, this project is designing a control loop feedback system in resonant network of the isolated DC-DC Converter. Currently, high voltages DC-DC Converters are widely used in different types of electronic equipment. However, the design of high voltage DC-DC Converters is problematic because the output of these converters cannot be controlled to its desired output. So, there is a need to control the output voltage and the duty cycle of the switch by using the Pulse-Width Modulation (PWM) control technique.

The choice of a converter topology for high-frequency and high-voltage applications is severely limited by the characteristics of high voltage transformer, component stresses, switching losses, efficiency, etc [2], [3]. It is well known that the use of current-mode control in PWM converters have significant advantages with respect to the more basic voltage-mode control [4]. In voltage-mode control, the feedback gain is limited by the presence of the secondary resonance [5], [6]. The FB-ZCS-PWM converter was observed to behave in chaotic manner.

This paper presents a comprehensive study of a high voltage version FB-ZCS PWM converter, analog study, power electronics study and PWM controller. The FB-ZCS has received significant focus, the converter's dual, the full-bridge zero-current-switch (FB-ZCS) converter, has not, even though it shares many of the same

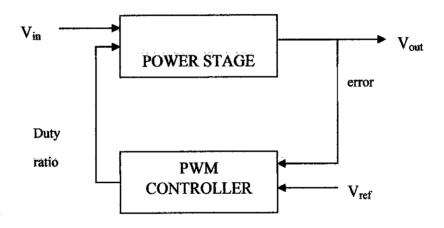

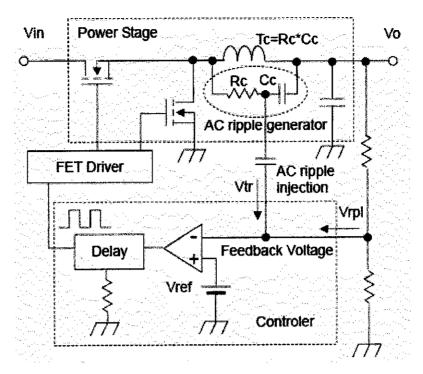

preferable attributes [7]. The semiconductor devices experience voltage and current stresses during turn-on and turn-off transitions. As a result, the resonant technique allows analyzing the FB-ZCS converter through the use of an average model. Control loop is functioning as a feedback circuit, which will monitor the output voltage and compares it with a reference voltage, using PWM technique [8]. The pulse-width-modulation (PWM) technique is praised for its high power capability and ease of control. A power stage, which is a DC-DC converter, is connected to PWM controller as shown in Figure 1.

Figure 1 DC-DC converter connected with PWM controller

#### 1.2 Problem Statement

#### 1.2.1 Problem Identification

The DC-DC converter is used to change the system voltages from one DC level to another DC level. The semiconductor devices experience voltage and current stresses during turn-on and turn-off. The FB-ZCS-PWM converter was observed to behave in chaotic manner. The pulse-width-modulation (PWM) technique is praised for its high power capability and ease of control. The concept of the control scheme is shifting one or two-channel PWM driving signals close to the other. The PWM controller will

correspond to the width of the two switches duty cycles. If there is an error in output voltage, the feedback controller compensates by adjusting the timing with which the switches are switched on and off.

Without feedback controller, the system cannot maintain the output voltage to the desired value and system cannot control the switch. Let's take an application of Traveling Wave Tube (TWT) as an example. TWT is a specialized vacuum tube used in wireless communication, especially in satellite system. The DC-DC Converter system is used to supply high electrons with high speed in the tube over a greater distance [9].

The application of TWT in which electrons are accelerated to a velocity at which they have a kinetic energy that is equivalent to the maximum voltage that was used to accelerate them. So, without the feedback controller, the electrons cannot maintain their acceleration at which they have the high kinetic energy equivalent to the maximum voltage and this will lead to decrease the system's performance.

#### 1.2.2 Significance of Project

The significant of this project is to improve the performance of the DC-DC Converter by applying the PWM controller to the system. The DC-DC Converter with high power is very useful in the communication system, especially for satellite system. Besides that, this high power application also used in electrical vehicle (EV) and for the medical apparatus, which is used for X-Ray imaging.

This project will help those applications to maintain their performance and can be used for high power application.

#### 1.3 Objectives and Scope Of Study

#### 1.3.1 Objectives

The objectives to implement this project are:

- Research and study on existing isolated DC-DC converter design based on the voltage and current mode PWM controller system, in terms of behaviors of the dynamic and circuit performance.

- To propose the new control scheme and compared to the conventional scheme

- To develop a step-by-step approach to develop the new system based on the study.

- To do simulation work on the selected design. This is to design a control loop feedback system in resonant network of an isolated DC-DC Converter by using the PWM controller, in order to control the output voltage.

#### 1.3.2 Scope of Study

The scope of study is presented in this report. There are several topics and issues that must be considered before proceeding any further in the design of the system. The scope of study depends mainly on these few areas:

- Study on isolated DC-DC Converter and the conceptual of voltage and current mode PWM controller system with the intention of having a view on how the system works.

- The mathematical modeling and control system equation are expected in driving the design, which relates the converter and feedback controller.

- The design methods for the improvement of the system in terms of the system's efficiency, switching frequency, reduce switching loss, input ripple current, output ripple voltage in order to achieve better performance.

Next section will review the literature about the project, including the concept of the controller.

# CHAPTER 2 LITERATURE REVIEW/THEORY

#### 2.1 DC-DC Converter

The main purpose of DC-DC Converter is to supply a regulated DC output voltage to a variable-load resistance from an unstable DC input voltage. Currently, there are Three (3) types of converters today, which are linear converters, switched capacitor converters (also known as charge pumps), and switched converters.

Linear converters can only generate lower output voltage from higher input voltage [10]. Most linear converters operate with low conversion efficiencies. However, they are commonly used in analog circuits to ensure a constant (or nearly constant) power supply voltage. Switched capacitor converters implement switches and capacitors to perform voltage conversion. For switched converters, the output voltage can be higher, lower or inverted compared to the input voltage. There are three main topologies of switched DC-DC Converters used today:

1. Buck (step-down converter) is used to produce an output voltage between ground and the input voltage. Figure 2 below shows a buck converter circuit.

Figure 2 Buck Converter

2. Boost (step-up converters) operates in the opposite manner compared to the step-down converter generating higher voltage output than at the input. Boost Converter circuit is shown in Figure 3 below.

Figure 3 Boost Converter

3. Buck-boost converter is used in applications where the output voltage required having levels both higher and lower than the input voltage. Figure 4 shows a buck-boost converter circuit.

Figure 4 Buck-Boost Converter

#### 2.2 Full-Bridge Boost Converter

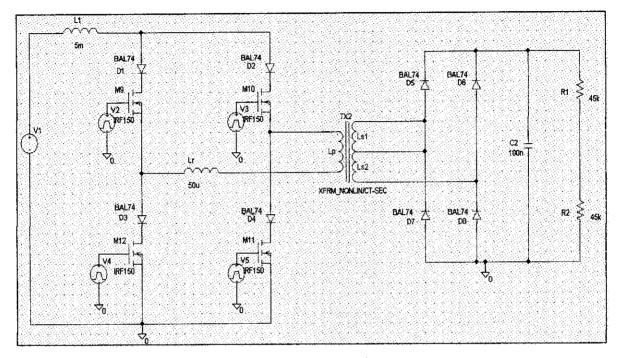

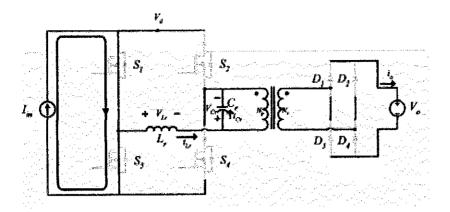

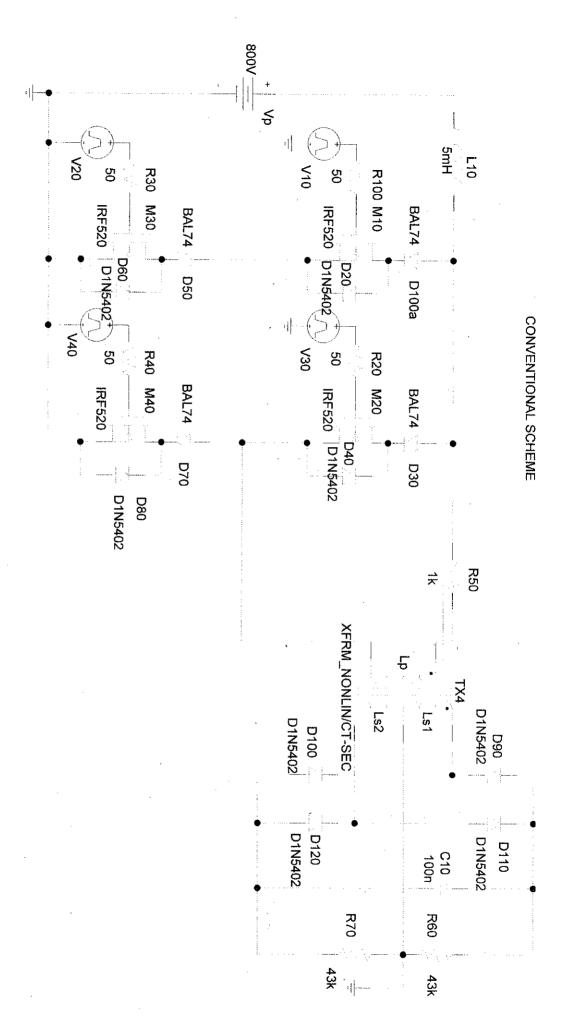

In this project, full-bridge boost-derived converter has been chosen as the basic converter before applying the controller circuit as shown in Figure 5 below:

Figure 5 Conventional Full-Bridge Boost Converter

The transformer in the isolated switch-mode converter, serves as a step-up/step-down voltage, reverses output voltage polarity, provides electrical isolation, and provides energy storage during the operation. Since all the energy obtained from the source is first stored in the transformer and then passed on to the load, this converter also known as an energy storage converter. The full-bridge boost-derived converter with full-wave rectifier in the output side is also known as a double-ended converter. The main advantage of the full-bridge configuration is that its core material is better utilized compare to the single-ended case [11].

In high voltage, DC-DC Converter, output filtering inductors cannot be used on the high voltage side due to high voltage drop. Only output capacitors can be used at the secondary side and thus, the converter should be current fed [12]. To obtain safe operation of transformer and high output voltage, multiple secondary rectifier circuits

are needed in series to feed the high voltage load. The proposed FB-ZCS PWM converter also uses phase-shift control to obtain fixed frequency operation.

#### 2.2.1 Resonant Network

An LC circuit (Figure 6) consists of an inductor and capacitor. When connected together, an electrical current can alternate between them at an angular frequency of

$$\omega = \sqrt{\frac{1}{LC}}$$

Where L is the inductance in henries, and C is the capacitance in farads. The angular frequency has units of radians per second.

Figure 6 LC Circuit Diagram

The resonance effect occurs when inductance and capacitive reactances are equal. The resonance refers to a class of phenomena in which a small driving perturbation gives rise to a large effect in the system. LC circuits are often used as filters [13].

A need to increase switching frequencies and to reduce EMI led to augmenting the controllable switches in certain basic switch-mode topologies by a simple LC resonant circuit, thereby shaping the switch voltage and current in order to yield zero-voltage and/or zero-current switching. Similarly, the inductor (such as the transformer leakage inductance) and the capacitors (such as the output capacitance of the semiconductor switch), which appear as undesirable parasitic in switch-mode topologies, can be utilized to provide the resonant inductor and the capacitor needed for the resonant-switch circuit [14].

$L_r$  is the resonant inductance that incorporates in the junction capacitance of the rectifier diodes and the reflected winding capacitance from the secondary side of the power transformer. The insertion  $L_I$  between input and inverter is to achieve a current-fed source.

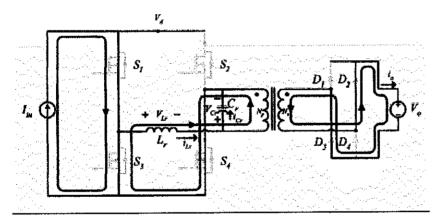

#### 2.2.2 Modes of Operation

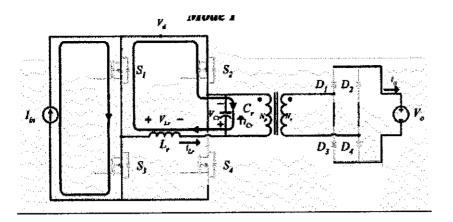

The full-bridge boost converter has ten (10) operation intervals during a single switching cycle. The equivalent circuit for each interval during the half-cycle is shown in Figure 7.

Figure 7 Resonant Boost Converter

#### Mode I $[t_0-t_1]$

Switch 3 (M3) and Switch 4 (M4) overlap. Operation begins with M1, M3, M4 and D9/D11 on. During this mode, M4 current is transferred to M3 in a nonresonant, linear fashion so that M4 can turn off with ZVS. During this mode, energy is transfer to the output. Mode I ends when the current in M4 reaches zero and M4 is turned off. Figure 8 shows the operation of Mode I.

$$i_{Lr}(t_o) = I_{in}$$

$$n = \frac{N_p}{N_s}$$

$$i_{Lr} = i_{M4} = \frac{nV_o}{L}.(t = t_o 0 \neq i_{Lr}(t_o))$$

$$v_{cr}(t) = nV_o$$

Figure 8 Operation of Mode I

# Mode II [t<sub>1</sub>-t<sub>2</sub>]

Input inductor charging interval. With M1 and M3 both on, the input inductor stores energy. No energy is transferred from the input to the load, which is supported by C<sub>o</sub>. This interval duration is assigned/controlled for nominal operation and ends when M2 is turned on. Figure 9 shows the operation of this mode.

$$i_{Lr}(t) = 0$$

$$v_{cr}(t) = n.V_o$$

Figure 9 Operation of Mode II

#### Mode III [t2-t3]

Figure 10 shows the resonant period for this mode. This mode begins when M2 is turned on. M1 current is transferred to M2 in a resonant fashion. M1 and M2 overlap during this mode for the transfer. Specifically, by allowing inductor current to resonant to  $-I_{in}$  M1 current goes to zero allowing ZCS. Mode III ends when M1 is turned off at  $t=t_3$ .

$$i_{Lr}(t) = -\frac{nV_o}{Z_o}\sin(\omega_o(t-t_2))$$

$$v_{Cr}(t) = nV_o\cos(\omega_o(t-t_2))$$

Where the resonant frequency,  $\omega_0$ , and the characteristic impedance,  $Z_0$  are defined by

$$\omega_o = \frac{1}{\sqrt{L_r C_r}}$$

$$Z_o = \sqrt{L_r C_r}$$

$$\gamma = \omega_o (t_3 - t_2) = \sin^{-1} \frac{I_m Z_o}{n V_o}$$

Figure 10 Operation of Mode III

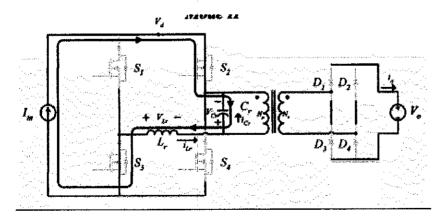

# Mode IV [t<sub>3</sub>-t<sub>4</sub>]

Figure 11 shows the discharge interval for this mode. This mode begins when M1 is turned off at  $t=t_3$ . During this mode, the resonant capacitor discharges linearly to  $-nV_0$ . Mode IV ends at  $t=t_4$  when capacitor is discharge allowing D1/D4/ to conduct

$$i_{Lr}(t) = -I_{in}$$

$$v_{Cr}(t) = -\frac{I_{in}}{C_r}(t - t_3) + nV_o \cos \gamma$$

Figure 11 Operation of Mode IV

#### Mode V $[t_4-t_5]$

Energy transferred to output, as shown in Figure 12 below. During this mode, D1/D4 is on and energy will be transferred from input inductor to output in a boost like fashion. The  $i_{Lr}$  and  $v_{Cr}$  equations are given by

$$i_{Lr}(t) = -I_{in}$$

$$v_{Cr}(t) = -n.V_{o}$$

$$I_{M} \bigoplus V_{i} \qquad V_{i} \qquad V_{i}$$

$$I_{N} \bigoplus V_{i} \qquad V_{i} \qquad V_{i}$$

Figure 12 Operation of Mode V

#### Modes VI-X

Modes VI through X are symmetric with respect to the first five modes.

#### 2.3 Feedback Controller

There are Two (2) types of feedback loops, an analog feedback loop and a digital feedback loop. The analog feedback loop is well understood and provides some advantages over the other type of feedback loop, the digital feedback loop. Each of the feedback loops has associated therewith a voltage sense input for sensing the supply output voltage and a pulse-width modulator (PWM) for generating switching pulses for driving switches [15]. The sensed voltage is compared in the analog domain to a desired operating DC voltage to generate an error voltage that is reduced to essentially zero volts at regulation. To compensate for loop phase shift, there is provided a compensator. This provides some phase lead in the feedback loop for the purpose of loop stability.

For the digital controller, its portion of the digital feedback loop is similar to the analog feedback loop. The voltage signal sense input utilizes an analog-to-digital converter (ADC) to convert the output voltage to a digital value and then compare this to a desired voltage to determine the difference voltage as an error voltage. A digital compensator then provides some phase lead to the feedback to maintain stability in the control loop. This digital error voltage is then converted into a varying pulse width for output to the driving switches on the switching converter. This in effect is a digital-to-analog converter.

Besides that, analog controllers do not have the ability to independently control the dead time for control signals for complementary switchers. For analog controllers the rising edge of a second control signal is based upon a falling edge of a first control signal. Thus, the second control signal is completely dependent on the falling edge of the first control signal. Some manner for independently controlling a rising edge of a second control signal with respect to a falling edge of the first control signal would provide much greater control of the operation of the switched power supply.

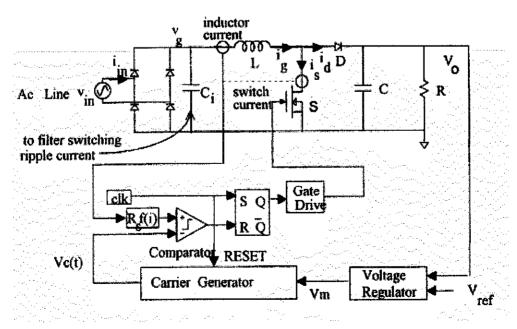

Based on Dr. Souvick Chattopadhyay, the used of PFC (Power Factor Boost) should shape the input current  $(i_{in})$  and to follow the same waveshape as in the input voltage  $(v_{in})$  [16].

Figure 13 Power Circuit of the single phase PFC rectifier [16]

The approach advocated in the design is to develop the average value of the differential voltage across system inductors and current through system capacitors. The method used in this design ensures the correct average, differential voltage appears across each inductor and the correct average current flows through each system capacitor in the model. Small-signal analysis forms the basis for effective control loop design. The development of this design, with a control method will delivers a single control signal to the bridge (switches) for the necessary switch conduction overlap as well as adjusts the phase shift to regulate the output.

The most common control method is Pulse-Width Modulation (PWM). This method takes a sample of output voltage and compares it with the reference voltage to establish a small error signal. A voltage mode is a method of closed loop of a switching converter where the pulse width is varied in response to changes in the output voltage to regulate the output [17]. The PWM (Pulse Width Modulation) is a modulation technique that generates variable-width pulses to represent the amplitude of an analog input signal [18]. A controller controls the output voltage of the converter based on regulating the duty-cycle of the switch. The feedback circuit monitors the output voltage and compares it with a reference voltage, in order to achieve the desired output. If there is an error in the output voltage, the feedback circuit compensates by adjusting the timing with which the MOSFETs are switched on and off.

A new feedback control method named 'ripple detection control' [19], a response delay can be made very small because an output voltage is directly compared with the reference voltage (as shown in Figure 14). There is a large feedback delay in principle in voltage-mode pulse-width modulation (PWM) control system, because the differential voltage between the output voltage and reference voltage is detected using an integrating circuit.

Figure 14 Ripple Detection Control Method [19]

From the derivations for the boost converter, it can be seen that changing the duty cycle controls the steady-state output with respect to the input voltage. The output voltage is controlled by the duty cycle of the switches [20]. A feedback and control circuitry can be carefully nested around the DC-DC Converter circuit to regulate the energy transfer and maintain a constant output within normal operating conditions. The feedback will regulate the output voltage. The most widely used method for controlling the output voltage through the switch is PWM. The PWM control technique maintains a constant switching frequency and varies the ratio of the charge cycle (time when the switch is on) and the discharge cycle (time when the switch is off) as the load varies. This technique affords high power efficiency. In addition, because the switching frequency fixed, the noise spectrum is relatively narrow, allowing simple low-pass filter techniques to greatly reduce the peak-to-peak voltage ripple at the output.

The concept of the new control scheme is shifting one of the two-channel symmetric PWM driving signals close to the other, while keeping the PWM control mode. All the corresponding components work at the conditions with even stresses as the case in the symmetric control scheme because the width of the two switches duty cycles is kept equal. The converter operates with Phase-Shifted PWM control at slightly

variable frequency with very strong variations in the operating point, but can operate at constant frequency if this behavior is more desirable than operation in a optimum switching line (with no reactive energy returned to the input source) [21].

For small-signal characteristic, the conventional compensation techniques would include current-mode control for fast response. A single voltage-mode controller is used in this design as the intent, which is not to design optimized control schemes but to validate the accuracy of the power stage model. The design of the controller accounts for stability at both operating points in anticipation of the step load changes performed in the transient simulations. A part from that, there is a converter which is controlled by the modulation of the lagging and leading leg, in order to achieve the ZVS [22], [23].

Control loop gain can be designed to be relatively insensitive to line voltage variation for current mode control and voltage mode control. For voltage mode control, loop gain is sensitive to line voltage variation of the converter [24]. However, with voltage-mode control, the problem with the transformer volt-second unbalance appeared [25]. From the analysis above, it can be conclude that the PWM technique is very effective to afford high power efficiency. This technique can used to control the output voltage by regulating the duty cycle of the switches. So, the PWM feedback controller is applied to the DC-DC Converter in this project and the performance of this system is evaluated.

# CHAPTER 3 METHODOLOGY/PROJECT WORK

#### 3.1 Procedures

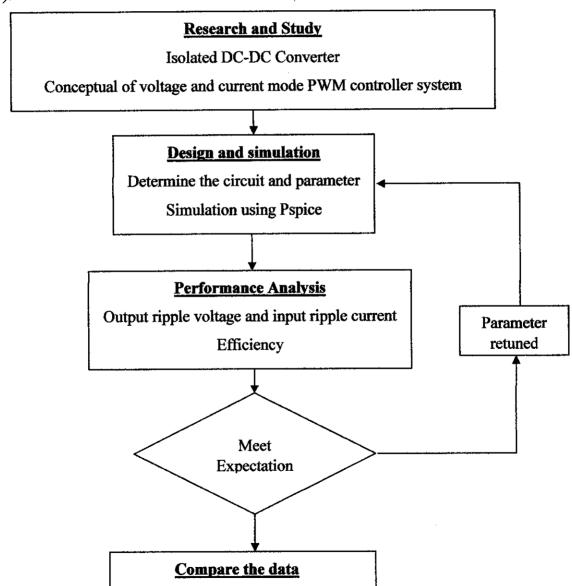

Below are the steps or methods to be taken to implement this project (refer Figure 15):

Figure 15 Flowchart of the methodology use in this project

The methodology of this project has been changed and limited to the simulation using Cadence only, as the output voltage of the converter is 15 kV and unable to come out with the prototype. So, this project will present only with the simulation between Two (2) sets of circuit and the data between them will be compared.

#### 3.1.1 Research and Study

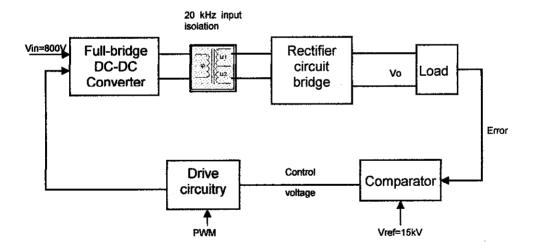

The first phase of this project is to search the information about isolated DC-DC Converter and understand the functionality. Besides that, the journal related to the project through has been searched IEEE Database and the conceptual of voltage and current mode PWM controller system has been studied. The system need to be analyzed, in terms of its efficiency, leakage spike in current and voltage and all the applicable waveforms. Any development should be made to the system and thus enhanced for a better performance. Below is the block diagram of the design, which is a combination of DC-DC Converter and feedback controller with PWM.

Figure 16 Block diagram of the design

Besides that, the software used also need to be mastered, in term of the setting of component's specification.

#### 3.1.2 Design and Simulation

The second phase is to determine the circuit and parameter before simulating using Cadence Software. All the component parameters will be calculated using basic equations and once upon understanding the whole concept; the simulation of the design can only be start. The performance of the simulation will be evaluated in order to satisfy the objective of the project.

#### 3.1.2.1 DC-DC Converter circuit

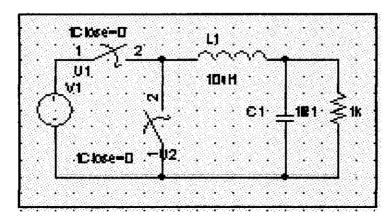

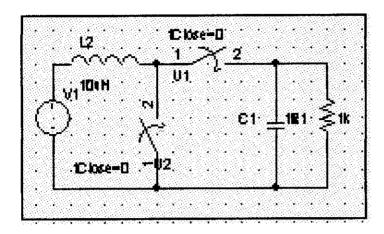

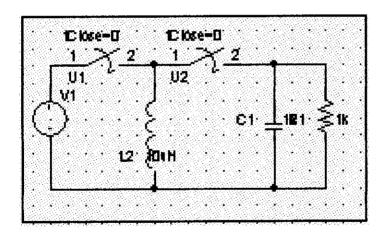

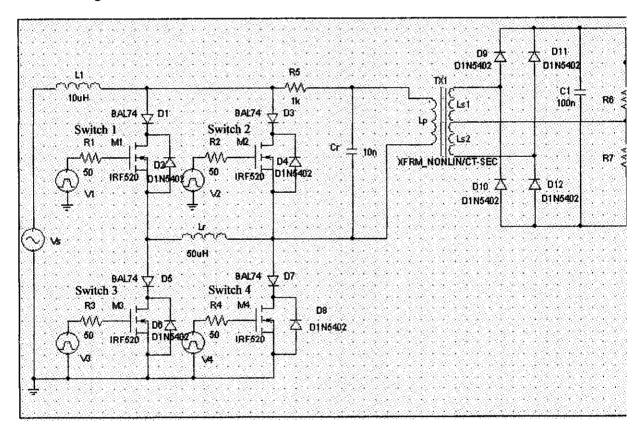

For the first stage, simulation has been done on the isolated DC-DC Converter as shown in Figure 17:

Figure 17 Isolated DC-DC Converter

Switch 1 (M1) and switch 4 (M4) will ON at the same time, and switch 2 (M2) and switch 3 (M3) will OFF at that time. These switches will operate simultaneously depending on the signal sent by the controller. From the high voltage transformer, the

leakage inductance is used as resonant inductor,  $L_r$  and its capacitance is integrated into the resonant capacitor,  $C_r$ .

All the component parameters have been calculated using the following equations:

$$T = \frac{1}{f}$$

$$\frac{V_o}{V_{in}} = \frac{n_2}{n_1} \frac{1}{2(1-D)}$$

$$PW = \frac{1}{f_s} xD$$

$$PER = \frac{1}{f_s}$$

### Basic settings:

- 1. Frequency, f=20 kHz so that T=50 us

- 2. Output voltage, V<sub>o</sub>=15 kV

- 3. Duty ratio, D = 0.833

# Components used in simulation:

- 1. Switch Power MOSFET (N-channel) type IRF520

- i. Period = 50 us

- ii. Pulse Width = 41.64 us

- iii.  $T_D = 0$

- iv.  $T_R = 0$

- v.  $T_F = 0$

- vi.  $V_I = 0$

- vii.  $V_2 = 20 \text{ V}$

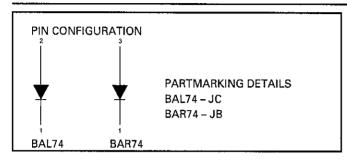

- 2. Power diode type BAL74 (D1. D2, D3, D4)

- 3. Power diode type D1N5402 (D5, D6, D7, D8, D9, D10, D11, D12)

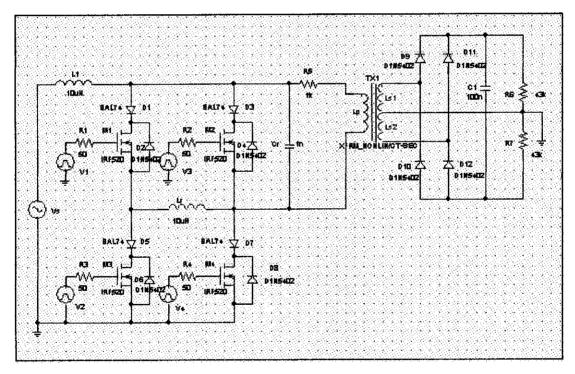

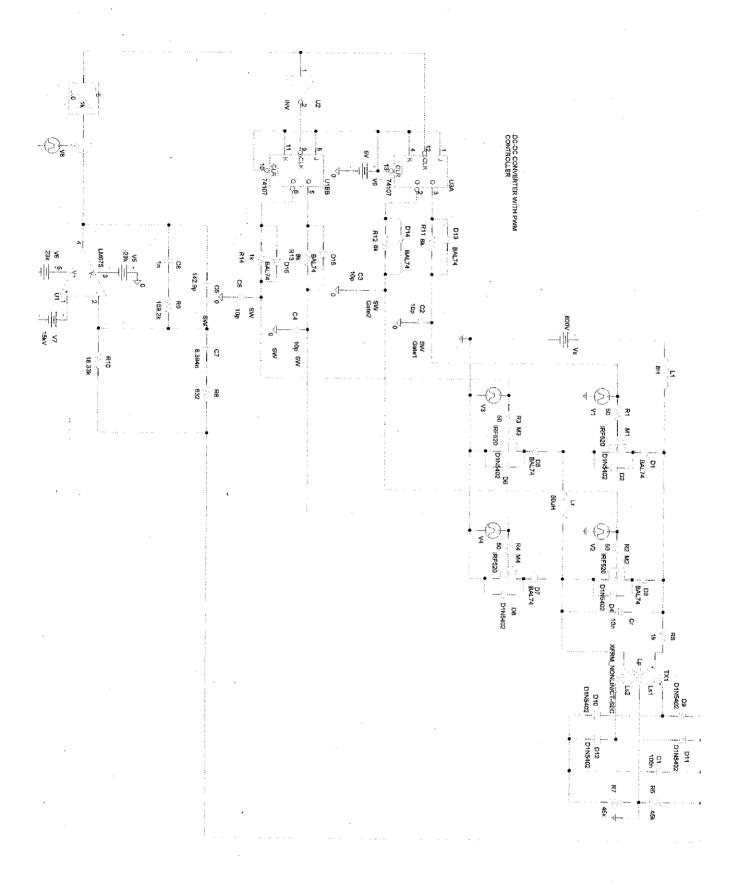

#### 3.1.2.2 DC-DC Converter with PWM feedback controller circuit

Refer Appendix B

# 3.1.3 Performance Analysis

The output waveform for voltage across the switch, the current across the load and the output voltage will be focused and analyzed.

# 3.1.4 Data Comparison

The data obtained from the simulation will be compared with the expected results, as listed in the table below.

| Criterions              | Conventional Scheme                  | DC-DC Converter with |

|-------------------------|--------------------------------------|----------------------|

|                         | (DC-DC Converter without controller) | PWM Controller       |

| % ripple input current  | 109%                                 | Reduce               |

| % ripple output voltage | 113%                                 | Reduce               |

| Efficiency              | 0.282%                               | Better               |

| Power losses            | 90.21kW                              | Reduce               |

Table 1 Expected result for the project

# 3.2 Tools Required

#### 1. Cadence Pspice software

#### 3.3 Component Rated

| Component | Maximum   | Maximum | Power       |

|-----------|-----------|---------|-------------|

|           | Voltage   | Current | Dissipation |

| IRF520    | 20V (Vgs) | 8 A     | 40 W        |

| D15402    | 200 V     | 3 A     | -           |

| BAL74     | 50 V      | 215 mA  | 250 mW      |

Table 2 Component Rated

# CHAPTER 4 RESULTS/DISCUSSION

#### 4.1 Finding and Discussion

For this project, full-bridge boost derived converter with full-wave output rectifier has been used. The main advantage of the full-bridge configuration is that its core material is better utilized compared to the single-ended case. Voltage and current flow on the design is show in appendixes A.

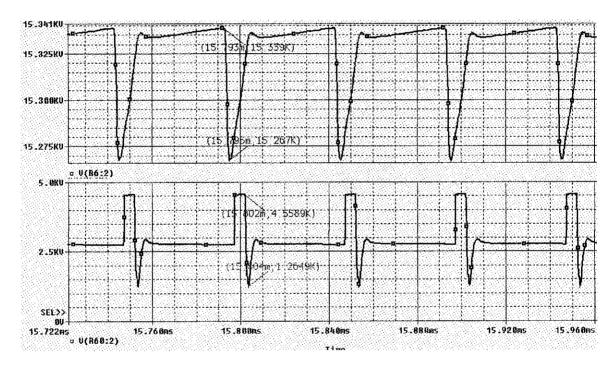

Figure 18 shows the output voltage of the conventional scheme and the design with the feedback controller.

Figure 18 Waveform of  $V_{out}[V(R60:2)]$  of conventional scheme and  $V_{out}[V(R6:2)]$  of the design

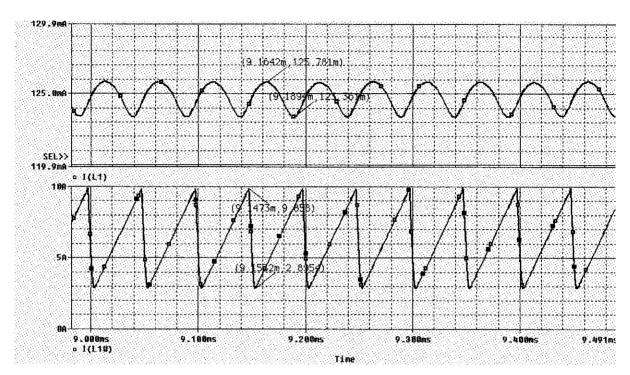

The waveform in Figure 19 below shows an input current for both conventional scheme and DC-DC Converter with feedback controller.

Figure 19 Waveform of I [I(L1)] of DC-DC Converter with feedback controller and waveform of I [I(L10)] of conventional scheme.

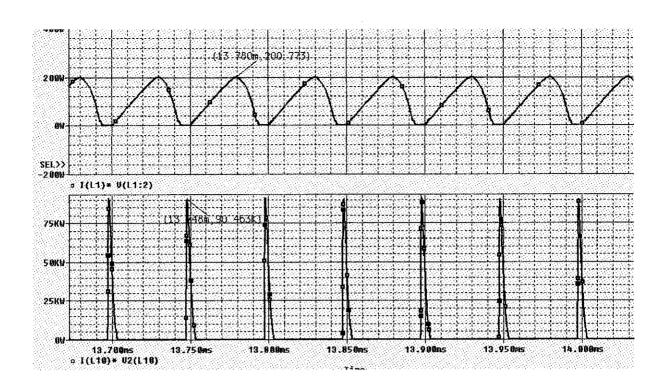

The waveforms in Figure 20 and Figure 21 below show the comparison between  $P_{in}$  and  $P_{out}$  in order to calculate the efficiency of the converter. The smaller  $P_{out}$  has produced the good efficiency for this system. The smaller  $P_{out}$  from the  $P_{in}$  shows that the system has small power loss and has good efficiency. The difference between  $P_{in}$  and  $P_{out}$  indicates the power loss of the system.

Figure 20 Maximum and minimum value of  $P_{in}[I(L1)*V(L1:2)]$  of conventional scheme  $P_{in}[I(L10)*V(L10)]$  of DC-DC Converter with feedback controller

Figure 21 Maximum and minimum value of  $P_{out}[W(R60)]$  of conventional scheme  $P_{out}[W(R6)]$  of DC-DC Converter with feedback controller

The transformer must be added between the power stage and the output for the purpose of voltage scaling. Transformer is used in switched-mode converter for electrical isolation between the input and output, reduction of stresses in switching devices and provision of multi-output connections. With the isolation transformer, the output voltage polarity reversal does not become a design restriction.

MOSFET has been chosen as a switch because its capability of high frequency operation. Besides that, MOSFET can withstand simultaneously application of high current and voltage without undergoing destructive failure due to second breakdown.

Ideal op amp is used as a comparator for the controller, which will compare the output voltage with the requirement that we need. If there is any difference, the feedback control loop will play its role to make sure we get the expectation output voltage. The controller that will be design is a power stage controller, which will control all the switches in the circuit that produce the output. But, the parameter should be determined first. The simulation is done part by part or phase by phase in order to choose the accurate setting and component [26].

The full-bridge circuit with four switches has been chosen to be the power stage circuit. Power Mosfets (IRF 520) have been chosen as a switches and the power diode located at the secondary part of the circuit functioning as a rectifier, to convert the ac voltage to dc output voltage.

The output waveform reached a steady state of 15.33 kV and this output voltage will be compared with the reference voltage at comparator. If there is an error, the pulse-width modulation (PWM) will generate its pulse and will go to the negative-edge triggered, J-K Flip-Flops, to generate complementary drive signals and relative phase shift between upper and lower switches. The RC network on the flip-flop output is used to set a fixed overlap time for both upper and lower switch sets.

#### 4.2 Evaluation

#### 4.2.1 % output ripple voltage

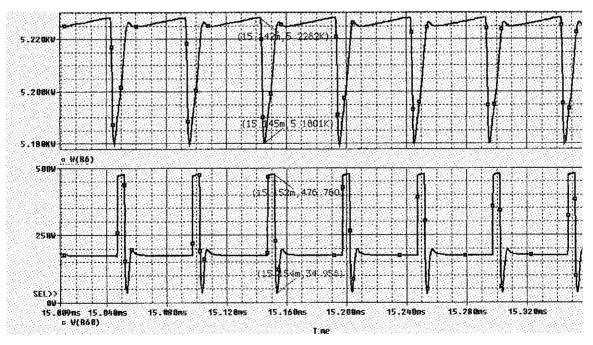

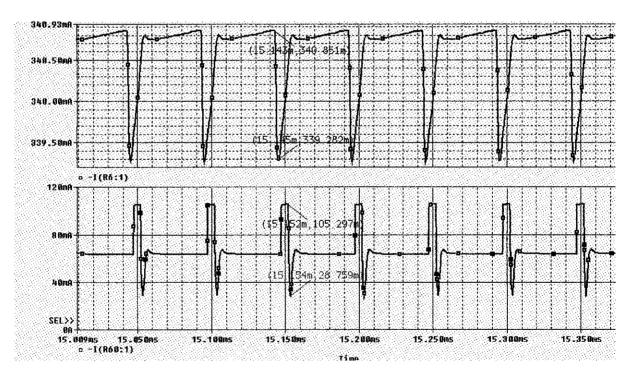

From the output voltage waveform (Figure 22), the ripple output voltage has been calculated as below: The calculations show the % output ripple voltage for the conventional scheme and % output ripple voltage for DC-DC Converter with PWM controller.

Figure 22 Waveform of  $V_{out}$  [V(R60:2)] of conventional scheme and  $V_{out}$  [V(R6:2)] of DC-DC Converter with PWM controller

#### 1. Calculation of % ripple voltage for DC-DC Converter with PWM Controller

$$V_{\text{max}} = 15.339kV$$

$V_{\text{min}} = 15.267kV$

$V_{o(dc)} = (15.339 + 15.267)/2$

$= 15.303kV$

$\Delta V_{R6} = 15.339 - 15.267 = 0.072$

$\text{"oripple} = \Delta V_{R6} / V_{o(dc)} \times 100\% = 0.47\%$

#### 2. Calculation of % ripple voltage for conventional scheme

$$V_{\text{max}} = 4.5589kV$$

$V_{\text{min}} = 1.2649kV$

$V_{o(dc)} = (4.5589 + 1.2649)/2$

$= 2.9119kV$

$\Delta V_{R6} = 4.5589 - 1.2649 = 3.294$

%ripple =  $\Delta V_{R6}/V_{o(dc)}x100\% = 113\%$

% ripple voltage for both systems cannot be compared as the output waveforms produced are not in the same axis. The difference of the output voltage for both systems is too large. For the conventional scheme, the % ripple voltage has given the value of 113% which has been exceeding 100%. This was due to the transformer that is not functioning as a step up voltage and has produced the output voltage of 2.9119kV. The secondary part of the system cannot function as in the Mode I, where only a little bit value of energy is transferred to the output. The output capacitor, C<sub>0</sub> cannot support the energy transferred from the input to the load. For the conventional scheme, it is better to put the high rated output capacitor to support the energy transfer to the load. But, the design has gives less output ripple voltage.

#### 4.2.2 % input ripple current

Figure 23 shows the maximum and minimum value of I<sub>in</sub> for calculation of input ripple current for both conventional scheme and DC-DC Converter with PWM Controller.

Figure 23 Waveform of I [I(L1)] of DC-DC Converter with PWM controller and waveform of I [I(L10)] of conventional scheme (DC-DC Converter without feedback controller).

Calculation of % ripple of input voltage for DC-DC Converter with PWM Controller

$$\begin{split} I_{\text{max}} &= 125.781 \text{mA} \\ I_{\text{min}} &= 123.361 \text{mA} \\ I_{o(dc)} &= (125.781 + 123.361) / 2 \\ &= 124.571 \text{mA} \\ \Delta I_{L1} &= 125.781 - 123.361 = 2.42 \\ \% \textit{ripple} &= \Delta I_{L1} / V_{o(dc)} x 100\% = 1.94\% \end{split}$$

#### 2. Calculation of % ripple of input voltage for conventional scheme

$$\begin{split} I_{\text{max}} &= 9.858A \\ I_{\text{min}} &= 2.8954A \\ I_{o(dc)} &= (9.858 + 2.8954)/2 \\ &= 6.9626A \\ \Delta I_{L10} &= 9.858 - 2.8954 = 6.3767 \\ \% ripple &= \Delta I_{L1}/V_{o(dc)} x 100\% = 109\% \end{split}$$

The input ripple current for the conventional scheme has exceed 100% which is very big value and this may be influenced by the value of the input inductor (L10) that functioning to store the current. For the conventional scheme, the value of input inductor of 5mH has influenced the energy stored for the system and has produced the big difference for the maximum and minimum value of the input current. To overcome this situation, high rated of input inductor is encouraged to use in order to support the high input voltage source. It can be say that the design has less input ripple current.

#### 4.2.3 Efficiency and power losses

From the Figure 24 and Figure 25, the efficiency and power losses of both systems can be calculated. Figure 24 shows comparison of input power for both systems and Figure 25 shows comparison of output power for both systems.

Figure 24 Maximum and minimum value of  $P_{in}[I(L1)*V(L1:2)]$  of conventional scheme  $P_{in}[I(L10)*V(L10)]$  of DC-DC Converter with PWM Controller

Figure 25 Maximum and minimum value of P<sub>out</sub> [W(R60)] of conventional scheme P<sub>out</sub> [W(R6)] of DC-DC Converter with PWM Controller

1. Calculation of efficiency for conventional scheme

$$P_{O\text{max}} = 476.760W$$

$$P_{O\text{min}} = 34.958W$$

$$P_{o(dc)} = (476.760 + 34.958)/2$$

$$= 255.859W$$

$$P_{in} = 90.463kW$$

$$\eta = \frac{255.859}{90.463k} \times 100\% = 0.282\%$$

2. Calculation of power losses for conventional scheme

$$P_{loss} = P_{in} - P_{out}$$

= 90.463k - 255.859

= 90.21kW

3. Calculation of efficiency for DC-DC Converter with PWM Controller

$$P_{O_{\text{max}}} = 5.2282kW$$

$$P_{O_{\text{min}}} = 5.1801kW$$

$$P_{o(dc)} = (5.2282 + 5.1801)/2$$

$$= 5.20415kW$$

$$P_{in} = 200.773W$$

$$\eta = \frac{5.20415k}{200.773} \times 100\% \ge 100\%$$

4. Calculation of power losses for DC0DC Converter with PWM Controller

$$P_{loss} = P_{in} - P_{out}$$

= 200.773 - 5.20415k

= -5kW

From the calculation above, it can be seen that the efficiency of the design exceed 100% and it not give the undesirable efficiency. This efficiency is undesirable as the output power and input power for both conventional scheme and DC-DC Converter

with PWM Controller is quite difference and cannot be compared. This unacceptable efficiency may be influenced by the energy stored in the primary side of the system, where much of the energy is transferred to the output and cannot be supported by C<sub>o</sub>. Besides that, the power losses for the DC-DC Converter with PWM Controller also gives the value of power gain, that should not be get in this experiment. But, for the conventional scheme, the power loss is quite large because the circuit used low rated inductor to store the energy. It is better to use the high rated output capacitor in order to support the energy transfer from the input to the load.

#### 4.2.4 Load Current

Figure 26 shows the waveform of the load current for conventional scheme and DC-DC Converter with PWM Controller.

Figure 26 Waveform of load current of DC-DC Controller with PWM Controller and waveform for load current of conventional scheme

From the waveform, the load current for conventional scheme is 67.028 mA and the load current for DC-DC Converter with PWM Controller is 340.0665 mA. Because of the big difference, the comparison cannot be made for the load current of both systems. The load current is influenced by the input current. As mention before, the

large difference in the input current has made the load current is unacceptable for the system.

#### 4.3 Discussion

The comparison between Two (2) systems cannot be made as the results obtained from the simulation are unacceptable. The reasons for the undesirable results have been identified and the suggestion to make the systems better has been made. Because of the time constraint, the simulation cannot be preceded with the suggestion made. However, the conclusion of the results obtained has been explained below, even though these results are not unacceptable for the systems.

Observation from the waveforms achieved from the simulation shows that DC-DC Converter with PWM Controller has produced the high output voltage of 15.33kV and less output ripple voltage. Besides that, it can be seen that the input ripple current also reduced to 1.94% compared to the conventional scheme. It was due to the rated inductor used to store the energy in the circuit.

The undesirable efficiency for DC-DC Converter with PWM Controller which has exceeded 100% is caused by the smaller input power and produced the desirable output power of 5kW. Apart from that, this situation has brought to the objectionable power loss that is a power gain of the system, as the circuit do not used any of power gain components. It may be influenced by the high power output that was produced by the step-up transformer.

Furthermore, the design cannot be implemented with the prototype as it produced the high output voltage that may give a good reliability since the system used the high rated components.

#### **CHAPTER 5**

#### CONCLUSION AND RECOMMENDATION

#### 5.1 Conclusion

As a conclusion, it is possible to design the resonant network of the isolated DC-DC converter with feedback controller based on small signal analysis and simulation. It is difficult to get or maintain the output voltage of the converter; the possible result can be obtained if the suitable components with the correct setting/range are used as the design is the high voltage circuit. The data obtained from the performance of the circuit will be compared and analyzed. Troubleshooting using the concept of phase by phase simulation has been done in order to know better the operation of the circuit and at the same time, to know the problem of the circuit. However, the results obtained from the simulation are undesirable and the suggestions have been made to overcome the unacceptable results. Because of the time constraint, the author did not come out with the suggestion results and has maintained the existing result.

#### 5.2 Recommendation

Recommendation made based on simulation and evaluation result, which may produce the good system.

- 1. Design combination with snubber circuit, which can reduce the input ripple current and output ripple voltage.

- 2. Choose the high power component which can support the high input voltage, since the design required high rated component in order to produce the desired output voltage.

- 3. Adding more parameters in evaluation such as diode reverse recovery, energy recovery, energy losses and others.

#### **CHAPTER 6**

#### REFERENCES

- [1] Iannello, C.; Shiguo Luo; Batarseh, I, A full-bridge ZCS-PWM converter for high voltage and high power applications, *IEEE PESC*, 2000.

- [2] Lin J.L.; Chang C. H.; Small-signal modeling and control of ZVT-PWM Boost converters, *IEEE PESC*, 2003.

- [3] Pereira A. A.; Alves Coelho E. A.; Farias V. J.; A lossless commutation PWM full-bridge DC-DC converter using phase shift control, *IEEE PESC*, 1996.

- [4] J. M. F. Dores Costa; M. Medeiros Silva; Small-Signal Models and Dynamic Performance of Quasi-Resonant Converters with Current-Mode Control, *IEEE PESC*, 1994.

- [5] Choi B.; Lim W.; Current-mode control to enhance closed-loop performance of asymmetrical half-bridge DC-DC converters, *IEE Proc. Electr. Power Appl.*, Vol 152, NO. 2, March 2005.

- [6] Zhu L.; Wang K.; Lee F. C.; Lai J. S.; New start-up schemes for isolated full-bridge boost converters, *IEEE PESC*, 2003.

- [7] Iannello, C.; Shiguo Luo; Batarseh, I, Small-signal and transient analysis of a full-bridge, zero-current-switched PWM converter using an average model, *IEEE Transactions on Power Electronic*, Vol. 18, No. 3, May 2003.

- [8] http://en.wikipedia.org/switched-mode\_power\_supply (June 2006)

- [9] http://en.wikipedia.org/wiki/traveling wave tube (November 2006)

- [10] Interim Report, Mohd Hasanul Arifin b Masahod, Universiti Teknologi Petronas, 2005

- [11] Power Electronic Circuits, Issa Batarseh, University of Central Florida, John Wiley & Sons, Inc., 2004.

- [12] Kim E. S.; Joe K. Y.; Kye M. H.; Kim Y. H.; Yoon B. D.; An improved soft-switching PWM FB DC/DC Converter for reducing conduction lossess, *IEEE PESC*, 1996.

- [13] http://en.wikipedia.org/wiki/resonant\_circuit (December 2006)

- [14] Power Electronics Converters, Applications and Design, Ned Mohan; Undeland; Robbins, John Wiley & Sons, Inc., 2003.

- [15]www.freshpatents.com/Digital\_pwm\_controller\_for\_digital\_supply\_having programmable dead times (December 2006)

- [16] Souvik Chattopadhyay, V. Ramanarayanan, and V. Jayashankar; A Predictive Switching Modulator for Current Mode Control of High Power Boost Rectifier; *IEEE Transc.* Vol 13; No 1; January 2003.

- [17] www.snaptec.com.au/technicalnotes/glossary.htm (June 2006)

- [18] www.answer.com/pwm.htm (June 2006)

- [19] <u>www.murata-northamerica.com/murata/murata.nsf/ripple\_detection\_control.pdf</u> (December 2006)

- [20] V. Garcia; M. Rico; J. Sebastih; M. Ma. Hernando; J. Uceda; An optimized DC-to-DC converter topology for high voltage pulse-load applications, *IEEE PESC*, 1994.

- [21] Mao, H.; Abu-Qahouq, J.A.; Deng, S.; Batarseh, I.; A new duty-cycle-shifted PWM control scheme for half-bridge DC-DC converters to achieve zero-voltage-switching, Applied Power Electronics Conference and Exposition, 2003. *APEC '03*. Eighteenth Annual IEEE, Volume 1, 2003.

- [22] Yan Y.; Soft-switching techniques for PWM full-bridge converters, *IEEE PESC*, 2000.

- [23] Soong T. T.; Huang N.; A novel zero-voltage and zero-current switching full-bridge PWM converter, *IEEE PESC*, 2005.

- [24] Chen Y. T.; Chen D. Y.; Wu Y. P.; Small-signal modeling of multiple-output forward converters with current-mode control, *IEEE PESC*, 1994.

- [25] Redl R.; Sokal N.; Balogh L.; A novel soft-switching full bridge DC-DC converter: Analysis, design considerations and experimental results at 1.5kW, 100 kHz, *IEEE PESC*, 1990.

- [26] www.seas.upenn.edu/~jan/spice/PSpicePrimer.pdf (June 2006)

# APPENDIX A CONVENTIONAL SCHEME (DC-DC CONVERTER WITHOUT FEEDBACK CONTROLLER)

# APPENDIX B DC-DC CONVERTER WITH PWM CONTROLLER

# APPENDIX C GANTT CHART FOR FIRST SEMESTER

Process

# APPENDIX D GANTT CHART FOR SECOND SEMESTER

| No. | No. Detail/ Week                      | 1 | 2    | 3 | 4    | S                   | 9       | 1  | 8 | 6  | 10 | 11 | 12 | 13 | 14 |

|-----|---------------------------------------|---|------|---|------|---------------------|---------|----|---|----|----|----|----|----|----|

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| -   | Research Work                         |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | -Project Planning                     | : |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | -Literature/methodology               |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| 7   | Project Work                          |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - Reference/Literature                |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - Simulation using Cadence            |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| ຕຸ  | Submission of Progress Report 1       |   |      | • |      |                     |         |    |   |    |    |    |    |    |    |

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| 4   | Project Work Continues                |   |      |   |      |                     |         |    |   | 44 |    |    |    |    |    |

|     | - Simulation using Cadence            |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - Reference/Literature                |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - Results and discussion              |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - References and abstract             |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     | - Technical Paper (IEEE Standard)     |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

|     |                                       |   | **** |   |      | :                   |         |    |   |    |    |    |    |    |    |

| 5   | Submission of Progress Report 2       | • |      |   |      |                     |         | •  |   |    |    |    |    |    |    |

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| 9   | Submission of Final Report Draft      |   |      |   |      |                     |         |    |   |    | •  |    |    |    |    |

|     |                                       |   |      |   |      |                     |         |    |   |    |    |    |    |    |    |

| 7   | Submission of Final Report Soft Cover |   |      |   |      |                     |         |    |   |    |    | •  |    |    |    |

|     |                                       |   |      | • | guS. | Suggested milestone | milesto | ne |   |    |    |    |    |    |    |

Process

#### **APPENDIX E**

## **DATASHEET FOR MOSFET (IRF 520)**

SUPERTEX INC

DE 8773295 0001582 0

IRF520 IRF521 IRF522 IRF523 R520 R521

N-Channel Enhancement-Mode Vertical DMOS Power FETs

| BV <sub>Dee</sub> / | R <sub>DMDM</sub> | Pictoria | Order Humbo | r / Padlage |

|---------------------|-------------------|----------|-------------|-------------|

| BV <sub>COS</sub>   | (Mess)            | (min)    | TO-220      | TO-82       |

| 100V                | 0.90              | 8.0A     | FHF520      | 8520        |

| 60V                 | 0.30              | B.OA     | IRF521      | R821        |

| 100V                | 0.40              | 7.0A     | FFF522      |             |

| ANV                 | 040               | 704      | IDEE00      |             |

#### **Features**

☐ Freedom from secondary break

**Ordering Information**

- ☐ Low power drive requirement

- ☐ Ease of paralleling

- D Low C<sub>les</sub> and test evitching a

- Excellent thermal stability

- ☐ Integral Source-Drain dipde

- High input impedance and high gain ☐ Complementary N- and P-Channel device

#### **Applications**

- D Motor control

- ☐ Converters

- □ 6w

- ☐ Power supply of

- Drivers (Relays, Hammers, Sciencide, Lamps, Memories, Displays, Bipotar Translators, etc.)

#### **Absolute Maximum Ratings**

| Drain-to-Source Voltage           | BV              |

|-----------------------------------|-----------------|

| Drzin-to-Gate Voltage             | BV              |

| Gute-to-Source Voltage            | ± 20V           |

| Operating and Storage Temperature | -55°C to +150°C |

| Soldering Temperature*            | 300°C           |

|                                   |                 |

#### **Advanced DMOS Technology**

These entrancement-mode (normally-of) power transi-tes a vertical DAGOS devoture and Supertex's well-prove gate merulacutring process. This combination produces with the power handling capabilities of bipoler translators

Superior Vertical DNOS Power FETs are ideally suited to a wide range of awtiching and amplifying applications where high breakdown voltage, high input impedence, low input capacitance, and last awtiching apeads are desired.

#### **Package Options**

#### SUPERTEX INC

O1 DE 8773295 0001583 1

IDEE SOURCES AND CONTRACT CONT

#### Thermal Characteristics

| Peckego        | l <sub>o</sub> (continuous)* | P (brised), | Power Diselection  OTa = 25°C | -CW | -åw  | len . | , mm, |

|----------------|------------------------------|-------------|-------------------------------|-----|------|-------|-------|

| IRF520, IRF521 | AO.8                         | 32.0A       | 40W                           | 80  | 3.12 | AD.8  | 32.0A |

| IRF822, IRF823 | 7.0A                         | 92.0A       | 40W                           | 80  | 3.12 | 8.0A  | 32.QA |

| R820, R621 .   | 1.0A                         | 9.DA        | 1W                            | 170 | 125  | 1.04  | 9.04  |

|                |                              |             |                               |     |      |       |       |

#### Electrical Characteristics (@ 25°C unless otherwise specific

T-39-//

| <b>Gymbol</b>       | Permineter               |                              |     | T)p         |      | Umit     | Conditions                                                                                    |                                              |

|---------------------|--------------------------|------------------------------|-----|-------------|------|----------|-----------------------------------------------------------------------------------------------|----------------------------------------------|

| BV <sub>max</sub>   | Drain-to-Source          | (RF620, IPF622,<br>F620      | 100 |             |      | v        | V <sub>101</sub> = 0, L <sub>1</sub> = 250µA                                                  |                                              |

|                     | Breakdown Voltage        | IRF521, IRF523,<br>R621      | 80  |             |      | •        | 493 = 41 P = 400/EX                                                                           |                                              |

| V <sub>anne</sub>   | Gets Threshold Voltage   |                              | 20  |             | 4.0  | ٧        | V <sub>G6</sub> = V <sub>C6</sub> I <sub>C</sub> = 250µA                                      |                                              |

| i comes             | Gate Body Lenkage        |                              |     |             | 500  | nA.      | V <sub>ee</sub> - ± 20V, V <sub>oe</sub> - 0                                                  |                                              |

| Des                 | Zero Gase Voltage Drain  | Current                      |     |             | 250  |          | V <sub>os</sub> = 0, V <sub>os</sub> = Max Flating                                            |                                              |

|                     | 1                        |                              |     |             | 1000 | μA       | V <sub>ee</sub> = 0, V <sub>bs</sub> = 0.5 Max Plating                                        |                                              |

|                     |                          |                              | 1   |             |      |          | T <sub>G</sub> = 126°C                                                                        |                                              |

| Dicen               | ON-State                 | IRF520, IRF521,              | 8.0 |             |      |          | V <sub>96</sub> = 10V                                                                         |                                              |

|                     | Drain Current            | R520, R521<br>IRF522, RF523  | 7.0 |             | -    | -        | V <sub>DB</sub> > I <sub>CHOND</sub> x: R <sub>CHHOND</sub> Macx Flash                        |                                              |

| Floatore            | Static Drain-to-Source   | IRF520, IRF521               |     |             | 0.3  |          |                                                                                               |                                              |

| natural             | ON-State Recistance      | R520, R521                   |     |             |      | <u> </u> | Ω                                                                                             | V <sub>06</sub> = 10V, L <sub>0</sub> = 4.0A |

|                     | <del> </del>             | PU-562, IRI-523              |     | <del></del> | 0.4  |          |                                                                                               |                                              |

| G <sub>FE</sub>     | Forward Transconductance |                              | 1.5 | 2.9         |      | Ø        | $V_{\text{Os}} > t_{\text{DERing}} \times H_{\text{Descrip}}$ Max Ration $t_0 = 4.0 \text{A}$ |                                              |

| Cien                | Input Capacitance        |                              |     |             | 600  |          | V <sub>ee</sub> + 0, V <sub>ee</sub> = 25V                                                    |                                              |

| Coss                | Common Source Output     | Capacitence                  |     |             | 400  | p₽       | f = 1 MHz                                                                                     |                                              |

| Cman                | Reverse Transfer Cope    | oltanos                      |     |             | 100  |          |                                                                                               |                                              |

| L <sub>econ</sub> . | Turn-ON Delay Time       |                              |     | Ĺ           | 40   |          | V <sub>00</sub> = 0.58V <sub>008</sub>                                                        |                                              |

| ζ.                  | Rise Time                |                              |     |             | 70   | -        | 1 <sub>00</sub> = 4.0A                                                                        |                                              |

| Seem.               | Turn-OFF Delay Time      |                              |     |             | 100  |          | V <sub>ms</sub> = 0.8 Mex Rating                                                              |                                              |

| ۱,                  | Fall Time                |                              |     | l           | 70   |          | •                                                                                             |                                              |

| V <sub>ee</sub> D   | Diode Forward            | IRF620, IRF621<br>RS20, RS21 |     |             | 2.5  | ٧        | V <sub>GS</sub> = CV, l <sub>SO</sub> = 1A                                                    |                                              |

|                     | Voltage Drop             | IPF522, IPF523               |     | L           | 2.3  |          | V <sub>600</sub> = UV, l <sub>50</sub> = BA                                                   |                                              |

| Ļ                   | Reverse Recovery Time    | •                            |     | 290         |      | res      | T, = 150°C, I, = 6.0A,<br>di <sub>pat</sub> = 100A/µB                                         |                                              |

Ploto 1: All D.C. parameters 100% tested at 25°C unless otherwise stated. (Pulse test: 200ps poles, \$% duty cycle.)

#### Switching Waveforms and Test Circuit

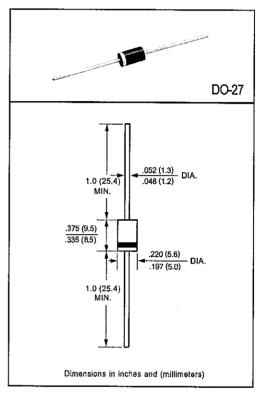

# APPENDIX F DATASHEET FOR POWER DIODE (D1N5402)

## DC COMPONENTS CO., LTD.

RECTIFIER SPECIALISTS

1N5400 THRU 1N5408

TECHNICAL SPECIFICATIONS OF SILICON RECTIFIER VOLTAGE RANGE - 50 to 1000 Volts CURRENT - 3.0 Amperes

#### **FEATURES**

- \* Low cost

- \* Low leakage

- \* Low forward voltage drop

- \* High current capability

#### **MECHANICAL DATA**

- \* Case: Molded plastic

- \* Epoxy: UL 94V-0 rate flame retardant

- \* Lead: MIL-STD-202E, Method 208 guaranteed

- \* Polarity: Color band denotes cathode end

- \* Mounting position: Any

- \* Weight: 1.18 grams

#### MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

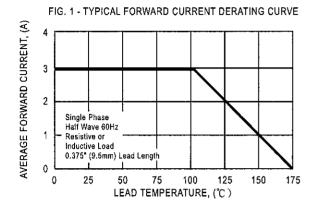

Ratings at  $25\,^{\circ}\text{C}$  ambient temperature unless otherwise specified. Single phase, half wave, 60 Hz, resistive or inductive load. For capacitive load, derate current by 20%.

| 170                                                                                                  | SYMBOL   | 1N5400 | 1N5401 | 1N5402 | 1N5404     | 1N5406 | 1N5407 | 1N5408 | UNITS |

|------------------------------------------------------------------------------------------------------|----------|--------|--------|--------|------------|--------|--------|--------|-------|

| Maximum Recurrent Peak Reverse Voltage                                                               | VRRM     | 50     | 100    | 200    | 400        | 600    | 800    | 1000   | Volts |

| Maximum RMS Voltage                                                                                  | VRMS     | 35     | 70     | 140    | 280        | 420    | 560    | 700    | Volts |

| Maximum DC Blocking Voltage                                                                          | Voc      | 50     | 100    | 200    | 400        | 600    | 800    | 1000   | Volts |

| Maximum Average Forward Rectified Current .375*(9.5mm) lead length at T L = 105°C                    | lo       |        |        | •      | 3.0        | ···    |        | '      | Amps  |

| Peak Forward Surge Current 8.3 ms single half sine-wave<br>superimposed on rated load (JEDEC Method) | [FSM     |        |        |        | 200        |        |        |        | Amps  |

| Maximum Instantaneous Forward Voltage at 3.0A DC                                                     | VF       | 1.1    |        |        |            |        |        |        | Volts |

| Maximum DC Reverse Current @TA = 25°C                                                                |          |        |        |        | 5.0        |        | 7743.0 |        | uAmps |

| at Rated DC Blocking Voltage @TA = 100°C                                                             | - IR     |        |        |        | 500        |        |        |        | umps  |

| Maximum Full Load Reverse Current Average, Full Cycle<br>.375*(9.5mm) lead length at T L = 75°C      | T IK     |        |        |        | 30         | •      |        |        | uAmps |

| Typical Junction Capacitance (Note)                                                                  | Cı       | 40     |        |        |            |        | pF     |        |       |

| Typical Thermal Resistance                                                                           | RθJA     | 30     |        |        |            |        |        | °C/W   |       |

| Operating and Storage Temperature Range                                                              | TJ, TSTG |        |        | -(     | 65 to + 17 | 5      |        | -      | °C    |

NOTES: Measured at 1 MHz and applied reverse voltage of 4.0 volts

BACK

**EXIT**

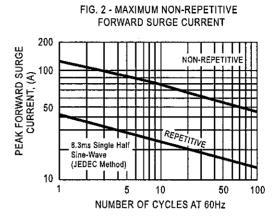

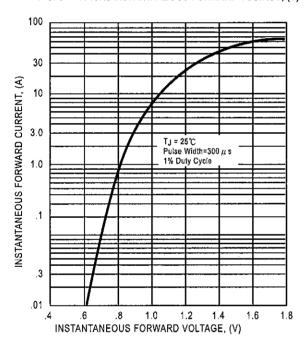

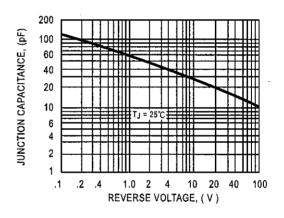

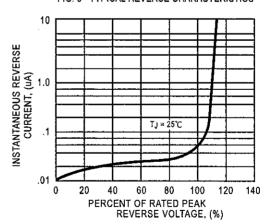

#### RATING AND CHARACTERISTIC CURVES (1N5400 THRU 1N5408)

FIG. 3 - TYPICAL INSTANTANEOUS FORWARD VOLTAGE, (V)

FIG. 4 - TYPICAL JUNCTION CAPACITANCE

FIG. 5 - TYPICAL REVERSE CHARACTERISTICS

**NEXT**

BACK

EXIT

### This datasheet has been download from:

## www.datasheetcatalog.com

Datasheets for electronics components.

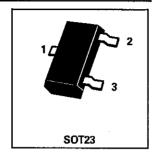

# APPENDIX G DATASHEET FOR POWER DIODE (BAL74)

#### **SOT23 HIGH SPEED SWITCHING DIODES**

BAL74 BAR74

#### ISSUE 3 - FEBRUARY 1997

#### ABSOLUTE MAXIMUM RATINGS.

| PARAMETER                                                 | SYMBOL                           | VALUE       | UNIT |

|-----------------------------------------------------------|----------------------------------|-------------|------|

| Continuous Reverse Voltage                                | V <sub>R</sub>                   | 50          | V    |

| Average Output Rectified Current (t <sub>av</sub> = 10ms) | I <sub>o</sub>                   | 100         | mA   |

| Continuous Forward Current                                | IF                               | 150         | mA   |

| Peak Forward Current (t = 15ms)                           | I <sub>FM</sub>                  | 200         | mA   |

| Forward Surge Current (t = 1μs)                           | I <sub>FS</sub>                  | 1           | Α    |

| Operating and Storage Temperature Range                   | T <sub>j</sub> :T <sub>stg</sub> | -55 to +150 | ° C  |

| Power Dissipation at T <sub>amb</sub> =25°C               | P <sub>tot</sub>                 | 330         | mW   |

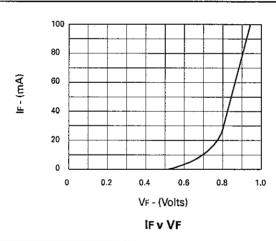

#### ELECTRICAL CHARACTERISTICS (at T<sub>amb</sub> = 25°C unless otherwise stated).

| PARAMETER             | SYMBOL          | MIN. | TYP. | MAX.       | UNIT                     | CONDITIONS.                                                                                          |

|-----------------------|-----------------|------|------|------------|--------------------------|------------------------------------------------------------------------------------------------------|

| Breakdown Voltage     | V <sub>BR</sub> | 51   |      |            | V                        | $I_R = 5\mu A$                                                                                       |

| Forward Voltage       | V <sub>F</sub>  |      |      | 1.0        | ٧                        | I <sub>F</sub> = 100mA                                                                               |

| Reverse current       | I <sub>R</sub>  |      |      | 0.1<br>100 | μ <b>Α</b><br>μ <b>Α</b> | V <sub>R</sub> = 50V<br>V <sub>R</sub> = 50V, T <sub>amb</sub> = 125°C                               |

| Capacitance           | Co              |      |      | 2.0        | pF                       | V <sub>R</sub> = 0                                                                                   |

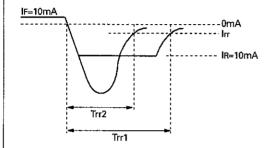

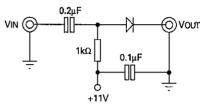

| Reverse Recovery Time | t <sub>rr</sub> |      |      | 4 2        | ns<br>ns                 | $I_F = I_R = 10\text{mA}, I_{RR} = 1\text{mA}$<br>$I_F = 10\text{mA}, V_R = 6V$<br>$R_L = 100\Omega$ |

Spice parameter data is available upon request for this device

## BAL74 BAR74

#### **Circuit For Measuring Switching Time**

Pulse is supplied by a generator with the following characteristics:

Output impedance =  $50\Omega$ Rise time <= 0.5ns Pulse width = 100ns Output is monitored on a sampling oscilloscope with the following characteristics:

Input impedance =  $50\Omega$ Rise time <= 0.6ns

### This datasheet has been download from:

# www.datasheetcatalog.com

Datasheets for electronics components.