# [ DESIGN AND IMPLEMENTATION OF A MOBILE ROBOT ]

by

[ TRUONG NGUYEN VU ]

#### FINAL YEAR PROJECT REPORT

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

DECEMBER 2004

Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2004 by [Truong Nguyen Vu], 2004

## [DESIGN AND IMPLEMENTATION OF A MOBILE ROBOT]

by

[TRUONG NGUYEN VU]

### FINAL YEAR PROJECT REPORT

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

DECEMBER 2004

Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2004 by [Truong Nguyen Vu], 2004

# **CERTIFICATION OF APPROVAL**

# [ DESIGN AND IMPLEMENTATION OF A MOBILE ROBOT ]

by

[Truong Nguyen Vu]

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved: am

Mr. MOHD HARIS MD KHIR Project Supervisor

UNIVERISITI TEKNOLOGI PETRONAS 31750 TRONOH, PERAK DECEMBER 2004

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

TRUONG NGUYEN VU

# ABSTRACT

Mobile robot nowadays has been used in various sectors of business ranged from sciences and industries to servicing and entertainment, and has posed very unique challenges to the researcher. Due to its autonomous nature, it requires an extensive sensing system to read the surrounding working environment, sufficient controller for data processing and decision-making, and also a very stable actuator system to actuate the robot response with respect to the working environment changes.

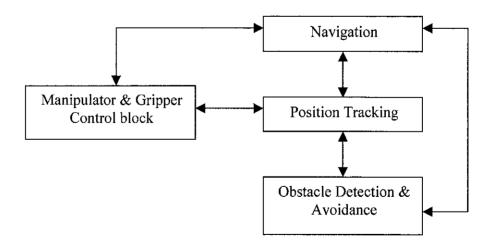

This report details the final year project of designing and implementing an autonomous wheel-based mobile robot, which has a capability to navigate according to a predetermined path while avoiding any obstacle on its route. It is also equipped with small manipulator to enable simple pick and place action: picking a small object from a predefined location and placing it at another predetermined location on the floor. Hence, in order for it to do all those task, the robot fundamentally consists of four main building functional blocks: (1) Navigation (2) Position tracking (3) Obstacle detection and avoidance (4) Manipulator & gripper control block (Since the robot movement is based on a predetermined plan, the path planner block is skipped in this project).

For further improvement, some fine-tuning on the manipulator structure and programming, as well as the development of a user interface to enable to user to select the robot movement path are highly recommended. In summary, the project has been successfully completed, providing a basement for future mobile robot development in UTP.

# ACKNOWLEDGEMENTS

First and foremost, I would like to show my greatest appreciation to Mr. Mohd Haris Md Khir, my direct academic supervisor for accepting me as his final year project student as well as being very supportive throughout the project. He spent so much time guiding me through the project, giving me the direction whenever I get stuck in any related problems from the beginning towards the completion of the project. Working under him is really a great pleasure since I have learnt a great deal of knowledge, skills as well as building up some necessary precious experiences.

Huge thanks to Dr Mohd Noh Karsiti, Head of Electrical Engineering program for his constant advises and support on non-academic matters.

My thankfulness is also extended to the EE lab technicians, especially Miss Hawa, Mr. Azhar, Mr. Musa as well as Mr. Isnani for their constant support. They have shared with me not only the engineering related knowledge but also their valuable experiences, which help me to successfully complete my final year project.

Besides, I would like to express my sincere thanks to Mr. Zuki and Ms Nascreen for their successful organizing of the Electrical engineering program final year project.

Thanks to all whose names that are not mentioned here for providing assistance, support and cooperation in any form.

Last but not least, I would like to dedicate my deepest gratitude to my parents for all the moral supports, concerns and understandings.

Best Wishes

Truong Nguyen Vu - 3188

# **TABLE OF CONTENTS**

| ABSTRACT                                         | V  |

|--------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                 | VI |

| LIST OF TABLES                                   | IX |

| LIST OF FIGURES                                  | X  |

|                                                  |    |

| CHAPTER 1: INTRODUCTION                          | 1  |

| 1.1 BACKGROUND                                   | 1  |

| 1.2 PROBLEM STATEMENT                            | 2  |

| 1.3 OBJECTIVE AND SCOPE OF THE STUDY             | 2  |

| CHAPTER 2: LITERATURE REVIEW AND THEORY          | 3  |

| 2.1 A SIMPLE INTRODUCTION TO MOBILE ROBOTICS     | 3  |

| 2.2 16F84 PIC MICROCONTROLLER                    | 4  |

| 2.3 DRIVE CIRCUIT                                | 6  |

| 2.4 MAPPING AND NAVIGATION                       | 8  |

| CHAPTER 3: METHODOLOGY AND PROJECT WORK          | 10 |

| 3.1 PROJECT METHODOLOGY                          | 10 |

| 3.2 COMPONENTS                                   |    |

| CHAPTER 4: RESULTS AND DISCUSSION                | 13 |

| 4.1 MECHANICAL STRUCTURE                         |    |

| 4.2 DRIVE CIRCUIT                                |    |

| 4.3 MANIPULATOR DESIGN AND IMPLEMENTATION        |    |

| 4.4 MOTOR SHAFT ENCODER                          |    |

| 4.5 OBSTACLE DETECTION                           | 25 |

| 4.6 PIC 16F84 MICROCONTROLLER AND ROBOT MOVEMENT |    |

| CHAPTER 5: CONCLUSION                            |    |

| REFERENCES                                       |    |

| APPENDIX A | Project General Schedule           | 38   |

|------------|------------------------------------|------|

| APPENDIX B | Mechanical Structure Drawings      | 39   |

| APPENDIX C | PIC 16F84 Data Sheet               | 41   |

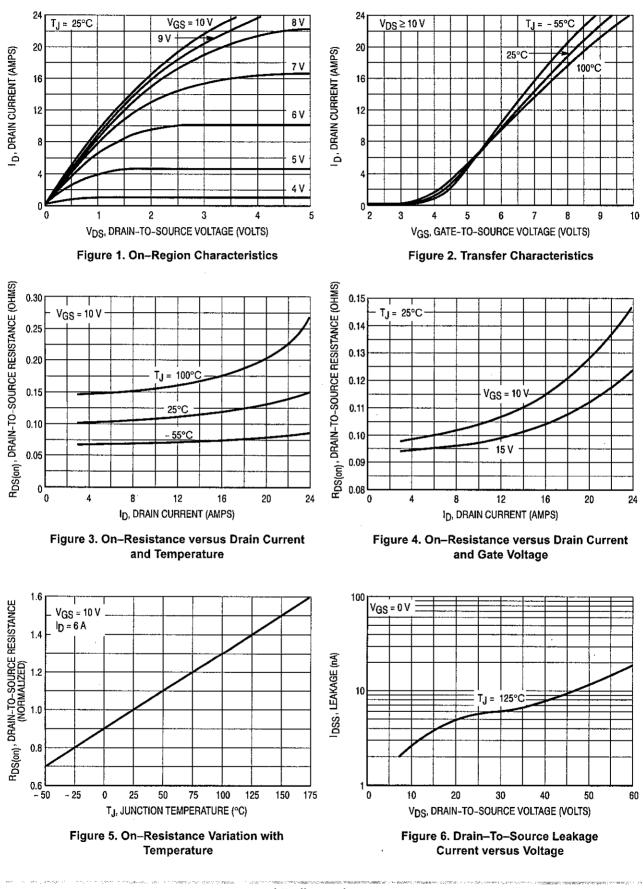

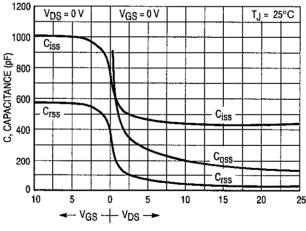

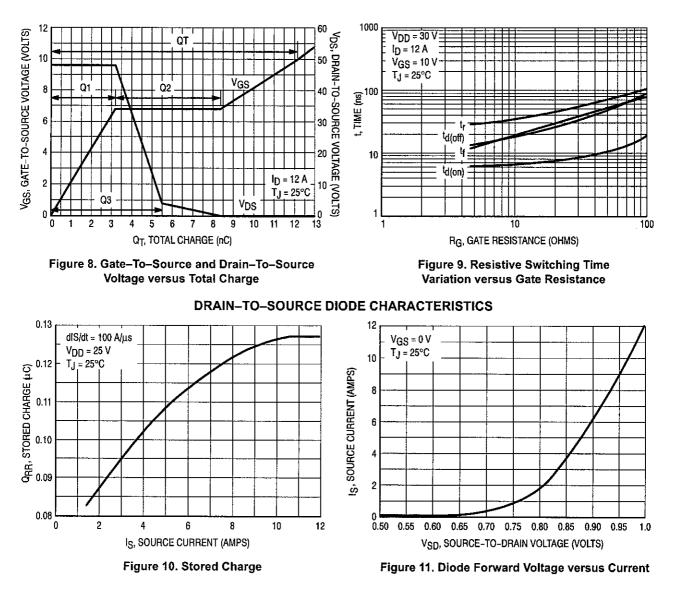

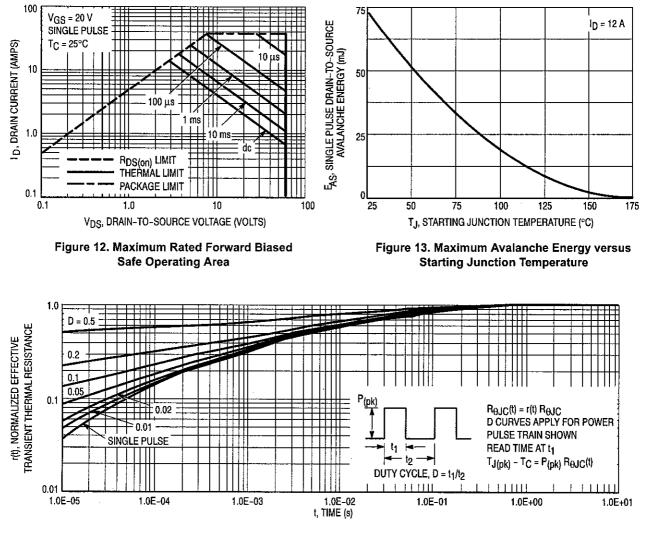

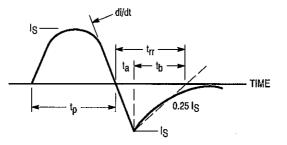

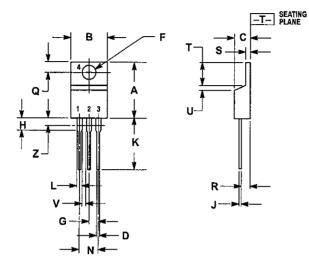

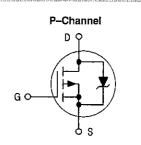

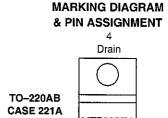

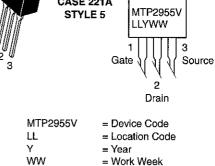

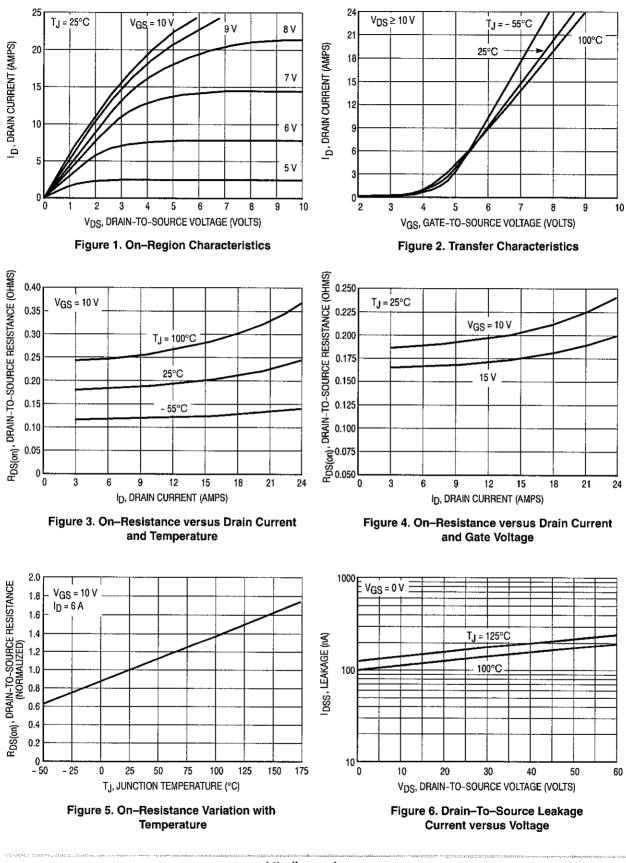

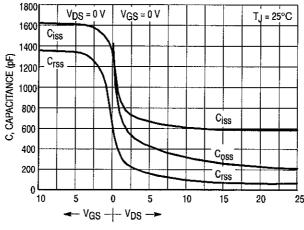

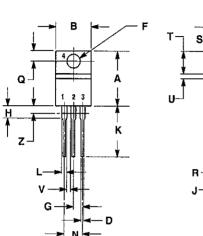

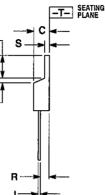

| APPENDIX D | N channel MOSFET Data Sheet        | . 57 |

| APPENDIX E | P channel MOSFET Data Sheet        | 65   |

| APPENDIX F | Microcontroller PIC C program code | 75   |

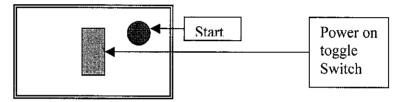

| APPENDIX G | How to operate the robot           | . 82 |

| APPENDIX H | I/O Assignment                     | 84   |

| :          |                                    |      |

# LIST OF TABLES

| Table 1 | H-Bridge Truth Table                                       | 6  |

|---------|------------------------------------------------------------|----|

| Table 2 | H-bridge operating true table                              | 16 |

| Table 3 | Induced voltage (Peak Voltage- mV) versus Sensing distance | 26 |

| Table 4 | Pre-amplified signal (peak value)                          | 28 |

| Table 5 | Rectified voltage versus sensing distance                  | 28 |

| Table 6 | Sensing Distance versus Output Voltage from the comparator | 29 |

# LIST OF FIGURES

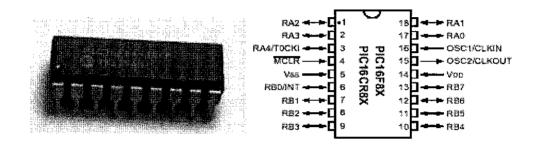

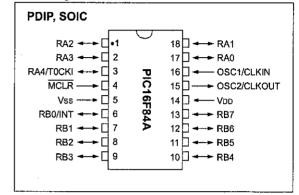

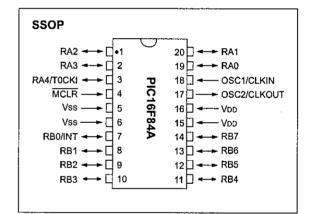

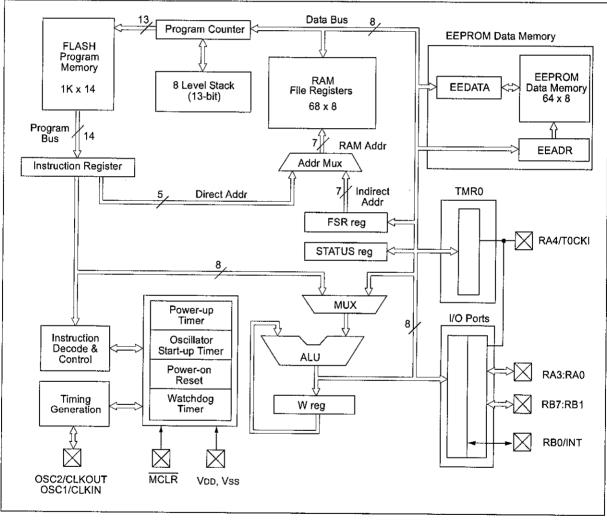

| Figure 1  | PIC 16F84 chip, IC pin out & block diagram                | 4  |

|-----------|-----------------------------------------------------------|----|

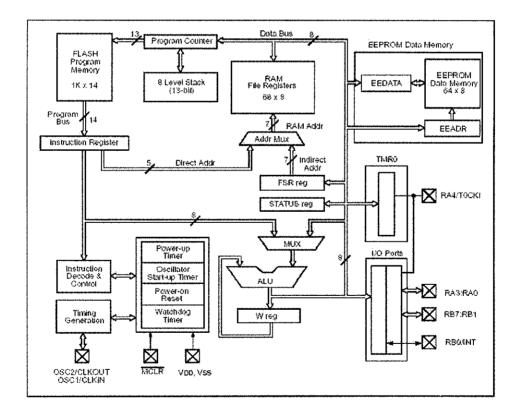

| Figure 2  | PWM pulse waveform for control servo motor positioning    | 5  |

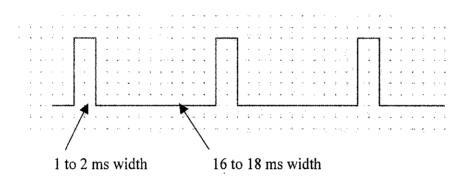

| Figure 3  | H-Bridge circuit                                          | 6  |

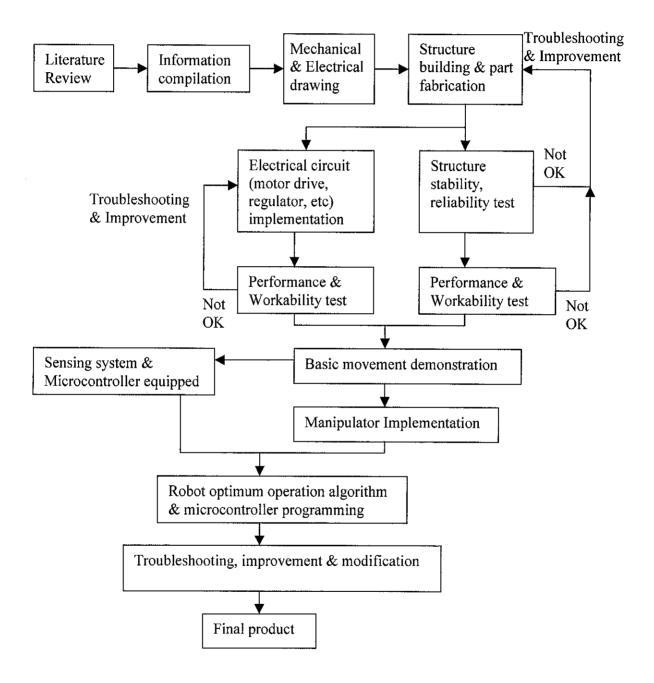

| Figure 4  | Project methodology                                       | 10 |

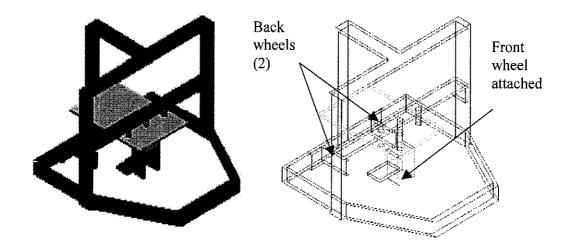

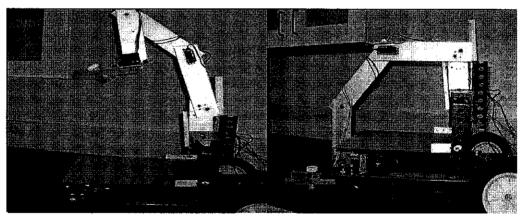

| Figure 5  | The first robot structure (without wheels)                |    |

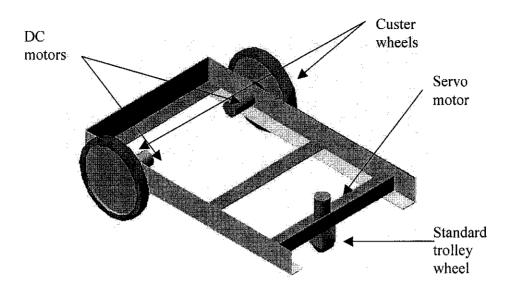

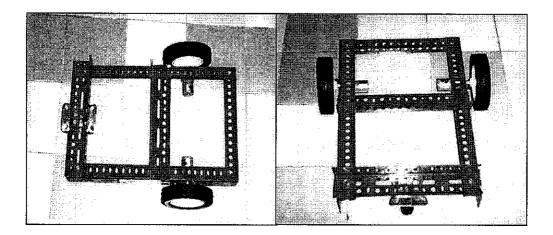

| Figure 6  | Base structure layout                                     | 14 |

| Figure 7  | Robot Base structure in implementation                    |    |

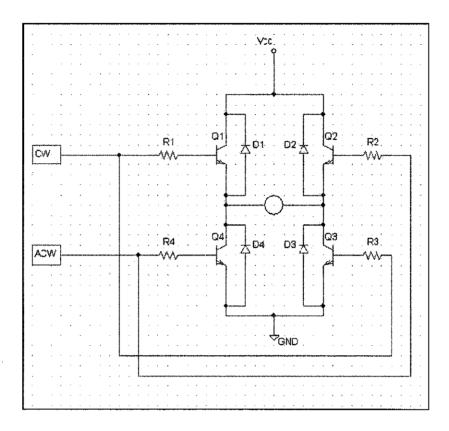

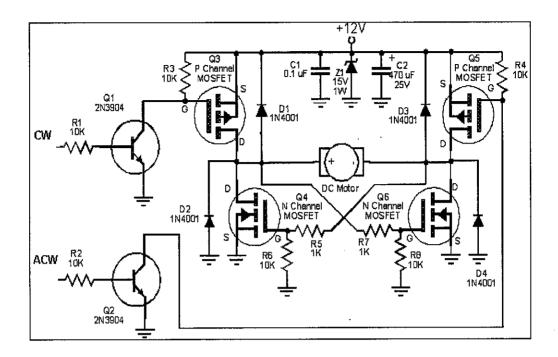

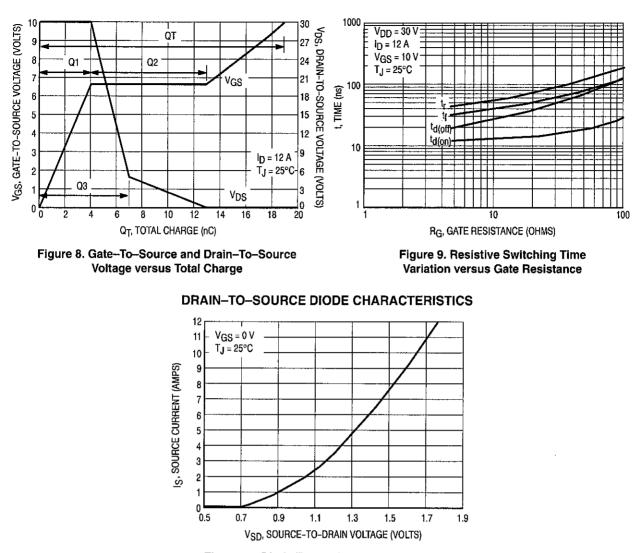

| Figure 8  | H-bridge employed MOSFET as switch                        | 16 |

| Figure 9  | Manipulator structure layout                              |    |

| Figure 10 | Joint #1 relay control circuit                            | 19 |

| Figure 11 | latching circuit                                          | 19 |

| Figure 12 | Manipulator in action                                     |    |

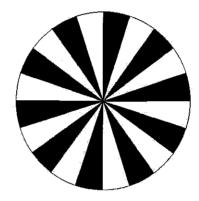

| Figure 13 | The wheel is equally divided into dark and bright section | 23 |

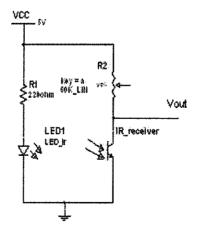

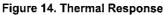

| Figure 14 | IR sensing circuit                                        | 23 |

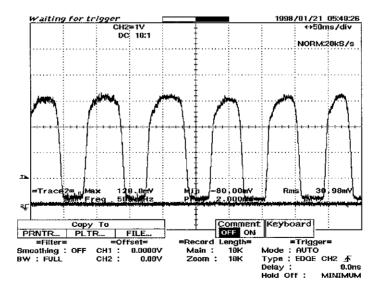

| Figure 15 | Wheel encoder output pulses                               | 24 |

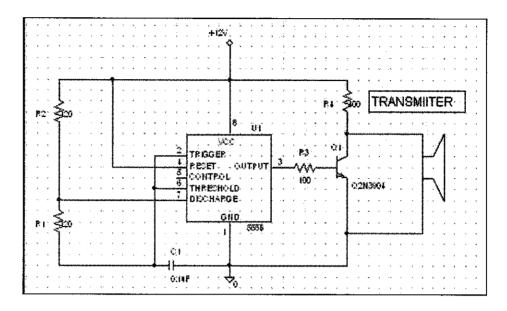

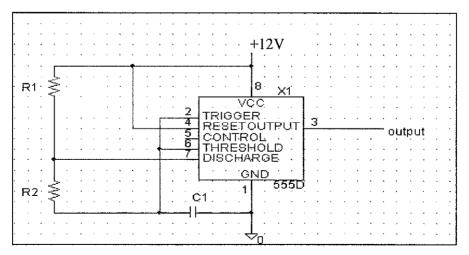

| Figure 16 | Ultrasonic transmitter (40 KHz)                           | 25 |

| Figure 17 | 555 timer network                                         | 25 |

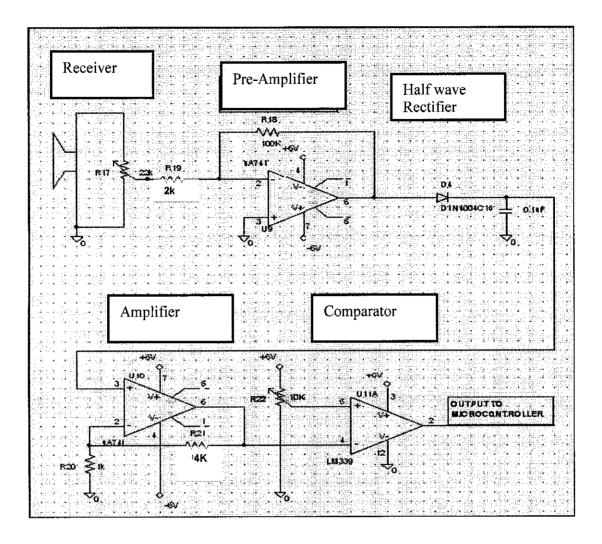

| Figure 18 | Ultrasonic receiver                                       | 27 |

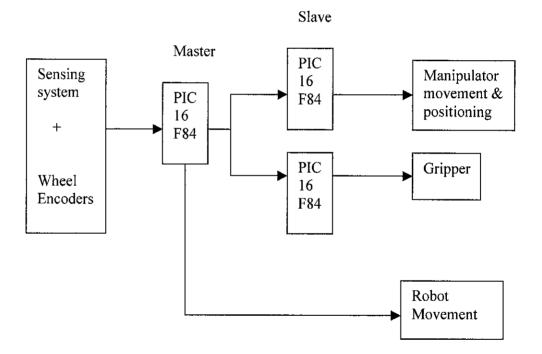

| Figure 19 | Microcontroller communication block diagram               |    |

| Figure 20 | Robot programming functional blocks                       |    |

| Figure 21 | Movement plan                                             |    |

| Figure 22 | A simple obstacle avoidance mechanism                     |    |

| Figure 23 | The robot grasps the object on the floor                  | 34 |

| Figure 24 | During picking up                                         | 34 |

| Figure 25 | The robot places the object into a predetermined location | 35 |

| Figure 26 | After placement                                           |    |

# CHAPTER 1 INTRODUCTION

# 1.1 BACKGROUND

For the last decades, many researchers have been dedicating their efforts in constructing revolutionary machines with embedded artificial intelligence to perform some risky, dangerous autonomous tasks (which were historically assigned to human beings). Among these machines, mobile robot is a typical example.

Mobile robot has constantly posed a unique challenge to artificial intelligence researchers. They are inherently autonomous, forcing the researchers to deal with those uncertainties (in both sensing and action), reliability as well as real time response. Hence, mobile robots require the integration of sensing, acting and planning within a single system. The sensing system critically helps the robot read the surrounding environment, enabling for path planning, finding, and navigation. It is really crucial in robot movement and acting to the changes of the environment.

Nowadays, mobile robots have been extensively used in various sectors of business ranged from industrial and scientific applications (i.e. petroleum path cleaning, underwater robot, space oriented robots, etc.) to servicing (i.e. patient assisting robot, trash collecting robot, etc). Although some of the researchers have successfully developed the legged-based robots, the most popular robot motion mechanism for the on-surface movement is wheeled based.

## **1.2 PROBLEM STATEMENT**

The project objective is to build a complete wheel-based mobile robot, which is able to work in an indoor environment. It should basically be able to navigate, avoid any obstacles along its movement towards to the preset target. This action is performed through the application of appropriate algorithms, which can compute the optimized path for the robot movement. Thus, it requires an active sensing system to measure the environment, input to a microcontroller for processing and decision making, as a powerful mean for algorithm implementation.

# 1.3 OBJECTIVES AND SCOPE OF THE STUDY

The objectives of the project are defined as below

- 1. Construct a stable wheel-based mechanical structure, which is enabled to support up to 20 kg of load.

- 2. Design a mobile robot, being able to navigate according to a predetermined path while avoiding any obstacles and return to the original route.

- 3. Design a robot which has the capability to go to a pre-determined location, pick an object and place it at another predefined location on the floor. This could be seen as an extra feature added to the robot.

Due to the nature of the project (one-year project), the tasks have been clearly divided into two parts for two semesters with manageable targets as follow:

- 1<sup>st</sup> semester: To develop the robot mechanical structure with motors and wheels mounted, drive circuit ready, so that the robot can perform some basic movements (i.e. forward, reverse or turning, etc)

- 2<sup>nd</sup> semester: To develop the sensing system together with the microcontroller equipped to the robot. With the artificial intelligence embedded, the robot is able to operate autonomously on just a single "start". A manipulator is an extra feature, enabling the robot to perform some pick and place tasks.

# CHAPTER 2 LITERATURE REVIEW AND THEORY

# 2.1 INTRODUCTION TO MOBILE ROBOTICS

Mobile robot has continuously achieved more importance in industrial and technical application, for its reliability (uninterrupted, reliable execution of autonomous task), accessibility (ability to access to sites that are inaccessible to humans such as tight spaces, hazardous environments, etc). It has been widely used for surveillance, inspection and transportation tasks as well as for some entertainment areas. However, before any level tasks to be executed, it is critical that the robot can operate safely, a void obstacles, and perform some fundamental activities such as contour following, door traversal, etc without posing any risk to the environment and people in it. In the past, to achieve that, people implemented the robot with "hard wired" control program designed by a human operator which has the major disadvantages as follows:

- Due to the rigid nature of the control program, the robot is not able to adapt with the changes in the environment (i.e. rough surface, surface color or texture) or to the robot itself (i.e. failure of some individual sensors).

- Beside, the design of fixed control program is costly as well.

As a result, learning controller has been developed to the extent that it allows the robots to acquire the competences to interact with the environment. The result is the control process based on the perception of the robot about the environment and the specific properties of the sensors. The robot now is able to learn through the entire period of operation, it has the capability to adapt well to the changes in the working environment. Actually, for the latter versions of mobile robot, CCD cameras, active sensors are u sually employed to capture advanced information about the working environment. That information will be then processed by a sufficiently strong processor (i.e. IBM base PC, laptop, etc) by the means of capable softwares (i.e. MATLAB). They are providing the computation platform for environment mapping construction and various optimal algorithms for robot navigation to be implemented.

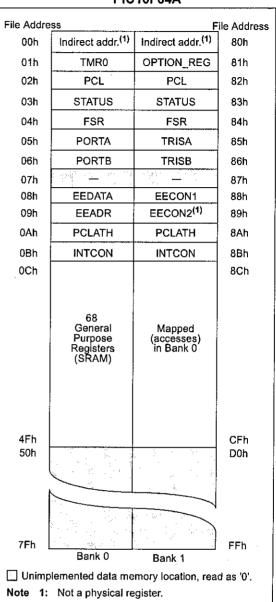

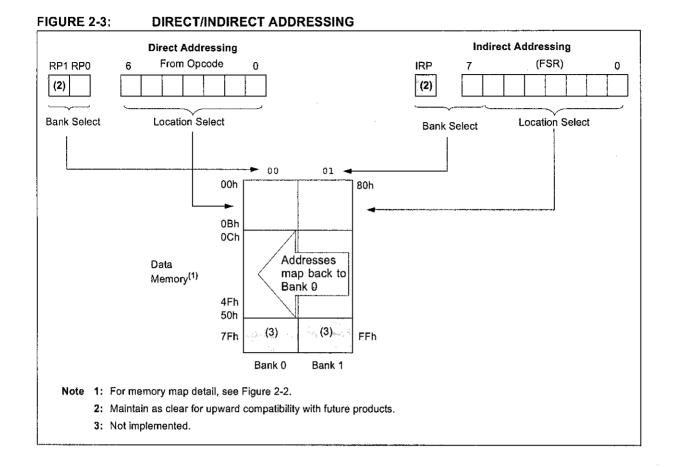

# 2.2 16F84 PIC MICROCONTROLLER

PIC 16F84 PIC chip is a versatile microcontroller with flash memory. The on board flash memory can endure a minimum of 1000 erase-write cycles; meaning that it can be reprogrammed and reused at least 1000 times. The 18-pin 16F84 devotes 13 of its pins for I/O. Each pin may be independently programmed as input or output. The pin status (I/O direction control) may also be changed via programming (assembly or C).

Figure 1 PIC 16F84 chip, IC pin out and block diagram

### 2.2.1 Programming 16F84 PIC to control servo motor

Servo motors are geared DC motors with a positional feedback control that allows the rotor to be accurately positioned. The motor shaft can be positioned through a minimum 90 degrees of rotation (from -90 to +90 degrees). To control the motor, the variable width pulse (PWM) needs to apply to the position control pin of the motor. The pulse is varied from 1 to 2ms. The width of the pulse controls the position of the shaft.

The 16F84 PIC can be programmed to control the servo motor. To be able to do so, a 1 to 2ms control pulse signal must be send from the microcontroller to the motor 50 to 60 times per second.

- 1ms pulse width will position the motor's shaft at the left position.

- 1.5 ms pulse for mid-position.

- 2ms pulse width for right position.

Figure 2 PWM pulse waveform for control servo motor positioning

# 2.3 DRIVE CIRCUIT

Normally when talking about motor directional rotation control, people refer to the H bridge circuit as shown below.

Figure 3 H- Bridge circuit

The operation of the circuit can be described through the following table.

Table 1H-Bridge Truth Table

| CW  | AW  | Q1  | Q2  | Q3  | Q4  | Motor rotating direction |

|-----|-----|-----|-----|-----|-----|--------------------------|

| On  | Off | On  | Off | On  | Off | Clockwise                |

| Off | On  | Off | On  | Off | On  | Anticlockwise            |

| Off                      |

| On  | On  | -   | -   | -   | -   | Not allowed              |

When CW and AW are both connected to 5 V, it is safe to have the motor at off state. The four diodes are to protect the transistor from the back EMF drawn back from the motor when it is rotating.

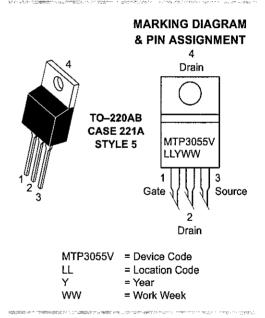

However, this circuit is not able to tolerate the large amount of current drawn from the motor under heavily loaded mode. Over-current can cause the driving transistors to be burnt. To overcome the problem, either power transistor or relay in place could be used. In the project, due to the very low on state resistance, which yields a quite high current rating (about 10 Amperes), MOSFET has been u sed to improve the efficiency of the bridge. The circuit schematic as well as operation is to be discussed in more details in the driving circuit section, **Chapter 4** (Results and Discussion).

# 2.4 MAPPING AND NAVIGATION

### 2.4.1 Mapping

Mapping refers to the construction of the environment model based on the measurements of sensors. This section describes two major map-constructing approaches: grid based and topological representation.

- Grid based map: represents the environment through the form of evenly spaced grids. Each grid cell contains a value, which indicates the presence or absence of an obstacle in the corresponding particular region of the environment. The grid-based map is considered easy to learn because they facilitate accurate localization and are easy to maintain.

- **Topological map**: represents the environment by graphs. The map consists of several nodes, which correspond to certain distinct location, situation on the robot navigating environment, connected by arcs if there is a direct path between them. The key advantage of the topological representation is its compactness, but requires fast planning.

There are few necessary concepts in map learning, and constructing:

- Thresholding: initially, each occupancy value in the grid is thresholded. Cells, whose occupancy values are less than the threshold, are considered free spaces (denoted as C). The others are considered occupied (denoted as D).

- Voronoi diagram: considering any point (x, y) ∈ C in free space, the basic points of (x, y) are the closest points (x', y') in the occupied space (C'). This is referring to all points that minimize the Euclidean distance to (x, y). Those points are called basic points of (x, y) and their distance to (x, y) are called the clearance of (x, y). Voronoi diagram (which are represented in a form of skeletonization) is the set of points in free space that have at least two different basic points.

- **Critical points**: are the points on the Voronoi diagram that minimize the clearance locally. Finding the critical points is the key idea for partitioning the free space.

• **Critical lines**: are obtained by connecting each critical point with its basic points.

#### 2.4.2 Localization

Localization is the process of aligning the robot local coordinate system with the global coordinate system of the map. It is really important for map-based approaches that lean their maps as the accuracy of the movement depends crucially on the alignment of the robot with its map. Traditionally, localization addresses two sub-problems: position tracking and global localization which are the two sides of the same coin: localization under uncertainty.

- **Position tracking**: is referred to the problem of estimating the location of the robot while it is moving with in its global map. It is particularly difficult to solve if the mapping is interleaved with localization.

- Global localization: is the problem of determining the position of the robot under global uncertainty. This problem is raised for instance when the robot uses a map that has been generated in the previous run, and is not informed about its initial location within the map.

#### 2.4.3 Navigation

Navigation consists of two different modules: path planning and reactive collision avoidance. The path planning generates the minimum cost path to the target using the map (grid based or topological map). As a result, it communicates with the intermediate sub-goals generated by the path planner to the collision avoidance module which controls the velocity and exact motion direction of the robot based on the most recent measurement of sensors to avoid collision with obstacles. Both modules adjust their plans and control continuously in response to the current situation.

# **CHAPTER 3**

# **METHODOLOGY AND PROJECT WORK**

# 3.1 PROJECT METHODOLOGY

Figure 4 Project methodology

- Literature Review & Information Compilation: Extensive research has been done on the current mobile robot technology. Various resources (i.e. internet, related book on robotics, etc) have been accessed. This step is very critical, since it collected necessary information to prepare for further implementation steps of the project.

- Electrical & Mechanical Drawing: At this step, all the related electrical circuit (i.e. Drive circuit, regulator, etc) as well as the mechanical structure need to be drawn out. The mechanical drawing includes the detail on the robot structure (i.e. 3D with detailed dimension, etc).

- Structure Building & Part Fabrication: This is when the structure is built; motors and wheels are mounted to the robot base. This is followed by testing to access its stability and reliability in movement. Besides, the electrical implementation needs to be carried out in parallel to equip the robot with the necessary electrical hardware for the basic movement.

- **Performance & Workability Test:** is to test whether or not the built model (including the electrical circuits) is able to work according to the expectation.

- **Basic movement demonstration:** is to enable the robot to perform some basic movement (i.e. moving forwardly / reversely or making a turn).

- Sensing System & Microcontroller equipped: is to equip the sensors and the controller to the robot. The sensing system could be seen as the eyes of the whole system to percept, and measure the environment. All these information will be processed by the microcontroller for decision making.

- Manipulator Implementation: is to develop a small manipulator, enabling the robot for the pick and placement action.

- Robot Optimum Operation Algorithm Implementation: This is when all the needed algorithms (i.e. obstacle avoidance, navigation, etc) are embedded to the system where the microcontroller is considered as the tool, the platform to be implemented on.

- **Troubleshooting & Improvement:** needs to be done regularly to ensure a good product eventually.

Besides, to ensure the project to be able to meet the target, a project schedule has been planed out. The detail can be referred at **APPENDIX A**.

# **3.2 COMPONENTS**

# 3.2.1 Mechanical Components

- 15cm diameter Custer wheels (2)

- 6 cm diameter standard trolley rubber covered wheel (1)

- Aluminum Alloy Coupling (3)

- Metal screws, compression springs, nuts.

- L shape angle mild iron bar with predrilled holes -2 m.

- U shape hollow Aluminum Alloy bar 1 m.

## 3.2.2 Electrical Components

- Futaba servo motor: 6 V (3), 12 V (1).

- 12 V RS DC motor (3)

- Microchip PIC (16F84-04 PIC) (3).

- 4 MHz crystal (1).

- N-channel MOSFET (4)

- P-channel MOSFET (4)

- BJT Q3904 transistor (4).

- RS single pole 6V relay (1).

- RS double pole 6V relay (1).

- LM7806 (1).

- LM7906 (1).

- Infrared sensors (3).

- Ultrasonic transducer (1).

- 741 Op-amp (4).

- LM339 (1).

- Capacitors, BJT transistors, resistors, switches, LEDs, etc (as per needed).

- Battery pack: 12 V 2A lead -acid standard motorbike battery source (1).

# CHAPTER 4 RESULTS AND DISCUSSION

# 4.1 MECHANICAL STRUCTURE

In order to obtain the optimized structure for the robot, several mechanical layouts have been designed and put in consideration.

# 4.1.1 The first approach

Figure 5 The first robot structure (without wheels)

This structure contains of 1 controllable front wheel (controlled via servo motor) for changing the direction of the robot; and two fixed position back wheels driven by DC motors. The whole structure could be implemented using solid aluminum alloy bar. Even though this design offers the strength as well as the light weight to the robot, the implementation also issues the associated cost (solid aluminum alloy bar is a relatively costly material for the project). The main problems raised are the difficulties in bending the aluminum alloy bar to the designed shape, also the balancing of the whole structure while carrying the heavy load (the structure does not have sufficient space to locate the load evenly). Therefore, it is decided not to further follow this layout to build robot base structure, instead seeking for the cheaper version while still offering the stability and the ease in implementation.

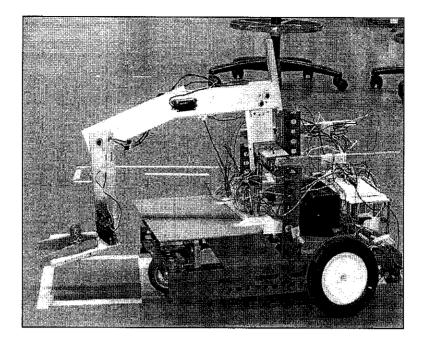

#### 4.1.2 The second approach

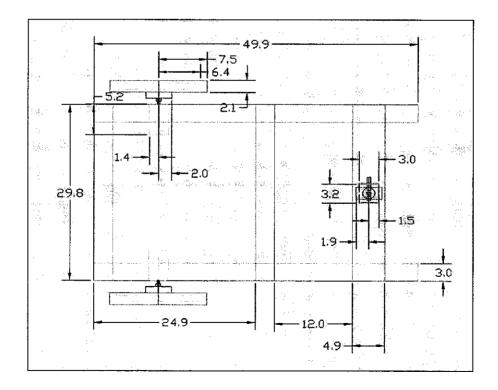

Figure 6 Base structure layout

The above structure comes with the mild iron bar skeleton. It is really convenience to be assembled since the mild iron bar comes in the shape of predrilled thin L shape bar which offering the strength and flexibility, but sufficiently light weighted. Those predrilled holes are made in various shapes and dimensions, which in turn let the motor be mounted on quite easily. Thus the implementation issue can be overcome. Moreover, this type of material is at a very cheaper price compared with the solid aluminum alloy bar, hence reduces the project cost.

The wheels are attached to the motor shafts through the Aluminum alloy couplings treated as the shaft extension. They are tightly screwed together, resulting in the stable and reliable movement as well as synchronizations. The detail drawings are shown in **APPENDIX B**.

For the mentioned above advantages, the second approach was chosen. The practical implementation showed the promised results. The structure is quite stable during the robot movement with sufficiently heavy load.

Figure 7 Robot Base structure in implementation.

# 4.2 MOTOR DRIVE CIRCUIT

Figure 8 H-Bridge employed MOSFET as switch

As mentioned earlier, to be able to improve the efficiency as well as enable the circuit to be capable to handle higher current rating, MOSFETs have been employed as the major switching devices in the H-bridge circuit. The following table details the circuit operation.

| CW  | AW  | Q1  | Q2  | Q3  | Q4  | Q5  | Q6  | Motor rotating<br>Mode |

|-----|-----|-----|-----|-----|-----|-----|-----|------------------------|

| On  | Off | On  | Off | On  | Off | Off | On  | Clockwise              |

| Off | On  | Off | On  | Off | On  | On  | Off | Anticlockwise          |

| Off | Stop                   |

| On  | On  | -   | -   | -   | -   | -   | -   | Not allowed            |

Table 2 H-bridge operating true table

#### Stop mode

When CW=0 and ACW=0, the motor is stopped. R3 and R4 pull up the Gates of Q3 and Q5 respectively and turn off the MOSFETs.

#### Anti-clockwise mode

When CW=0 and ACW=1 (+5V), the motor is in anti-clockwise direction. Q1 is turned off and Q3 is turned off due to R3. Q2 is turned on by the voltage at B. Q2's collector pulls Q5's Gate to ground. This turns on Q5 (P channel needs more negative voltage than Source to turn on). The negative side of the motor is raised to +12V. R5 raises Q4's Gate to around +11.5 V which turns on Q4. Q4's Drain goes to ground which makes the positive side of the motor go to ground. R7 is also connected to the positive side of the motor which pulls down Q6's Gate and makes sure that it is turned off. The current path for the motor is from +12V to Q5 to negative contact to positive contact to Q4 to ground.

#### **Clockwise mode**

When CW=1 and ACW=0, the motor is in clockwise direction. Q2 is turned off and Q5 is turned off due to R4. Q1 is turned on due to the voltage at A and Q1's collector goes to ground. This turns on Q3 raising the motor's positive side to +12V. R7 raises Q6's Gate voltage and turns it on. When Q6 turns on, R5 makes sure that Q4 remains off. The current path for the motor is from +12V to Q3 to positive contact to negative contact to Q6 to ground.

#### Not allowed mode

If CW=1 and ACW=1 then all MOSFETs turn on which shorts out the power supply among other things. This situation is not allowed to be occurred.

## 4.3 MANIPULATOR DESIGN AND IMPLEMENTATION

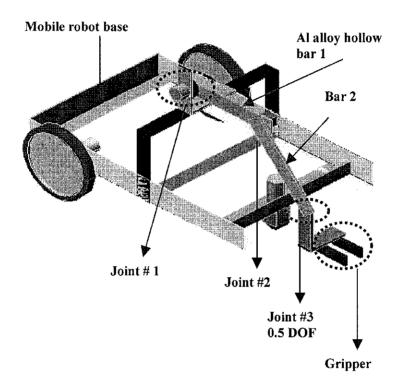

To enable the robot to have a simple pick and place capability, in this project we also include the design and implementation of a small manipulator, which is designed to have 2.5 DOF. What meant by 2.5 DOF is that it has two motor-controlled joints and one dependent joint which could be counted as half DOF as shown below.

Figure 9 Manipulator structure layout

#### 4.3.1 Joint #1

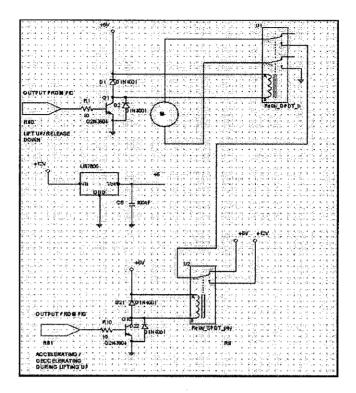

This joint is very critical since it withstands the whole manipulator load. Hence geared heavy duty 12 V RS DC motor is used here to be able to bring up and down the manipulator during pick up and placement of the object. For this situation, two stoppers are used at the back and in front of the joint to position the attached Al alloy bar when it hits the stoppers. In order to minimize the shaking/vibration of the structure when the Al Alloy bar hits the stoppers, the following relay circuit (which employs *latching circuits* to interface PIC output with relays) was implemented.

Figure 10 Joint #1 relay control circuit

### 4.3.1.1 Latching circuit

Due to the fact that the output from the PIC microcontroller is less than 20mA which is not sufficient to directly turn on / off the relay, a circuit network consisted of a BJT transistor and 2 D1N4001 Diodes is used for interfacing purpose between the PIC and the controlled relays.

|                           |                      |                                |               | ***<br>*:.⊮<br>≪:.⊮ |                                        | 4           | øy<br>Å     |      | 2    |                               |                |                    |          |            |       |                                      |                                                                                                                                                         |                                    | u4                                                                                                                                                                                                                                                                                                                                                     |                              |

|---------------------------|----------------------|--------------------------------|---------------|---------------------|----------------------------------------|-------------|-------------|------|------|-------------------------------|----------------|--------------------|----------|------------|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                           |                      |                                |               |                     | <u>کی</u> م<br>بہ بہ<br>د فر           |             |             |      |      |                               |                |                    |          | . 19 •     |       |                                      |                                                                                                                                                         |                                    |                                                                                                                                                                                                                                                                                                                                                        |                              |

| 114<br>1141<br>124<br>125 | * *<br>** *<br>** ** | ي ه<br>در ي<br>د- ه            |               | * *<br>* *<br>* *   | * *<br>* *<br>* -                      |             |             | D 16 | 1100 |                               |                | ید:<br>ایجا<br>ایر |          | • •<br>• • |       |                                      | •                                                                                                                                                       | f neig<br>Angeleige<br>Angeleige   | 8                                                                                                                                                                                                                                                                                                                                                      |                              |

| our                       | reut                 | F RC                           | ) <b>W</b> (P | C                   | RI                                     |             |             | D2 7 |      |                               | i ir<br>i<br>i |                    |          |            | 4<br> | ۰۰۰۰<br>۱۹۰۰<br>۱۹۰۰<br>۱۹۰۰<br>۱۹۰۰ | tity i                                                                                                                                                  | • * * .<br>• • • .<br>• • • .      | L3                                                                                                                                                                                                                                                                                                                                                     |                              |

|                           | 2) +<br>- 2<br>2,    | مربع<br>مربع مربع<br>مربع مربع |               | 2                   | -~~<br>10<br>0                         | V<br>211350 | -<br>-<br>- |      | Ū (N | 1001                          | • • • •        | 199<br>199<br>199  |          |            |       |                                      | e de la constante<br>La constante<br>La constante de la constante<br>La constante de la | ы жой<br>11 алд<br>11 алд<br>12 ар |                                                                                                                                                                                                                                                                                                                                                        |                              |

|                           | net a tra            | بد<br><br>                     |               |                     | ا به رکامی<br>( به ده به<br>زیره ارمین |             | ÷.,,        |      |      | ant àrr<br>Arrait<br>Gailtean |                |                    | ў.<br>У. |            |       |                                      |                                                                                                                                                         |                                    | من المراجعة المراجعة<br>مناطقة المراجعة المراج<br>مناطقة المراجعة المراج | 1918-19<br>2 12-2<br>2 12-11 |

Figure 11 Latching circuit

The circuit operation can be described as follows:

- When the control signal (CS) is turned high (+5V), Q1 on, current will flow from the external source through the relay coil, passing the transistor to ground→ the coil is energized, switching on the relay.

- When CS is low, Q1 off, the relay coil is de-energized, relay off.

With this circuit, the drive (Figure 10) can easily accept the TTL logic inputs to control the motor motion as described below.

### 4.3.1.2 Joint #1 Relay control circuit operation

In order to lift up the manipulator during pick up operation, R B0 (output from PIC 16F84) goes high, activating the U1 relay to on position. At the same time, RB1 goes high, turns on U2 relay, and connects the motor terminal to the 12 V 2A battery source. The DC motor will rotate clockwise for about 2 seconds to lift the arm up. At this point of time, the Al alloy bar should have almost hit the back stopper, RB1 goes low, switches to 6V power source (output from LM7806 regulator) to be a pplied to the motor terminal. The motor now acts as a generator supplying back the current to the source which in turn brakes and slows down significantly the motor speed and torque so that when the Bar hits the stopper, the vibration is reduced.

To bring the arm down during placement action, RB0 goes low to turn off the DC motor. The arm will freely drop down due to gravity for about 1 second. After 1 second, RB0 goes high again. At this moment, RB1 has been already low. The motor terminal is applied to the 6V regulated source (which is not sufficient to lift the arm up again) to help the motor fight against the gravity. Therefore, it could act as a brake to reduce the dropping speed of the arm which in turn significantly reduces the vibration while the arm hits the front stopper.

#### 4.3.2 Joint #2

A 12V Futaba coreless servo motor is used at this critical joint as it requires accuracy in positioning. One output (i.e. RB0) from another PIC 16F84 microcontroller is connected to the positioning control terminal of the servo motor.

During lifting up the object, PWM pulse of 1.6ms is given to the motor, let it bring the object a little bit from the floor (with the gripper holding). Then the whole manipulator is lifted up by the DC motor, PWM pulse of 1.1 ms is applied to bring down and place the object on the carrier platform of the robot (with the gripper releasing).

In order to bring down and place the object on the floor, after the whole arm (with the gripper holding) is lifted up by the DC motor. PWM pulse of 1.6 ms is applied on the servo motor terminal, bringing up the object out of the carrier platform. The DC motor then releases the arm down and brakes it accordingly until it reaches the front stopper. PWM pulse of 1.4 ms is now applied to finely bring down and place the object on the floor (with the gripper releasing).

#### 4.3.3 Joint #3 (0.5 DOF)

This is a dependent joint which is loosely screwed to the end of **Bar 2** (figure 9). Because of that, the gravity will play an active role to keep the gripper always perpendicular to the floor (horizontal axis) during pick up and placement. The gripper is also made from Al alloy hollow bar attached to this particular 0.5 DOF joint. The opening and closing of the two fingers are basically controlled through the use of two 6V Futaba indirect drive servo motors. These motors will help the fingers hold the object tightly by moving accurately towards each other. An infrared sensing circuit is also attached to the gripper letting it detect the desired object to pick up.

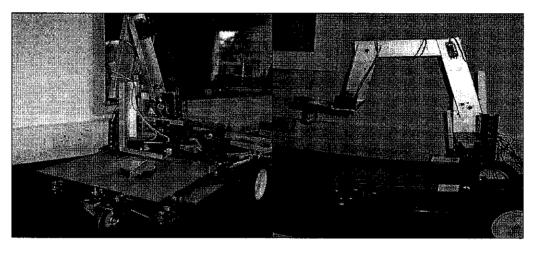

#### 4.3.4 Manipulator in implementation

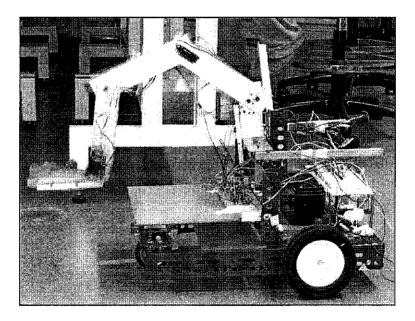

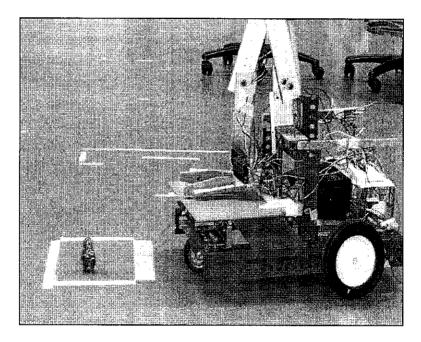

In this part, the manipulator in picking up and placing a small cylindrical box located from a known location on the floor was tested. The operation was so smooth that it was capable to handle the job well. First the object was picked up and put inside the carrier platform on the robot from the floor, then brought up and place back at predefined location. The followings are some photos taken of the manipulator in action as demonstrated below.

Manipulator stationed on carrier platform

Manipulator during placement operation

Manipulator during picking up

Object are placed back on the table

Figure 12 Manipulator in action

# 4.4 MOTOR SHAFT ENCODER

In order to record the movement of the wheel so that the position of the robot can be tracked, the motor shaft encoders are required. Unfortunately, the currently used RS DC motor in the robot does not consist of an internal encoder, thus it is necessary to construct our own ones. The basic mechanism is described as follows:

- The wheel is divided evenly into bright and dark sectors as in figure 13.

- IR (infrared) sensor (circuit is as shown in figure 14) is then used to sense the changing on brightness level while the wheel rotates which in turn keeps track for the number of rotations of the wheel so that we could know how far the robot has traveled.

Figure 13 The wheel is equally divided into dark and bright section

Figure 14 IR sensing circuit

### 4.4.1 IR (infrared) sensing circuit operation

- When the sensor encounters the dark surface on the wheel which actually absorbs the light transmitted from the IR emitter , thus there is no IR light reflected back to the receiver, the receiver is then acting as an open circuit→ V<sub>out</sub> = 5 V

- When the sensor encounters the bright surface on the wheel which actually reflects back the light transmitted from the IR transmitter to the receiver, the receiver is then acting as a short circuit  $\rightarrow V_{out} = 0V$

- The transition between low and high (or high and low) is then counted through the mean of a microcontroller. The number of pulses counted is actually related to the distance traveled by the robot through the following formula:

# Distance = (number of pulses) x (pi x diameter) / (number of sectors)

In our case, number of sectors is 20; diameter is 15 cm, therefore:

```

Distance = (number of pulses) (3.14) (15 \text{ cm})/(20)

= 2.355(number of pulses) - cm

```

which yields a maximum possible tolerance of about 2.355 cm.

Figure 15 Wheel encoder output pulses

# 4.5 OBSTACLE DETECTION

Figure 16 Ultrasonic transmitter (40KHz)

In this project, to enable the robot to detect any obstacles blocking its route, an ultrasonic sensing system is designed and implemented. Figure 16 shows the transmitter circuit.

#### 4.5.1 Ultrasonic Transmitter

The 40 KHz Ultrasonic sound is generated through the clock signal produced from a 555 timer circuit.

Figure 17 555 timer network

The circuit parameters are calculated below to produce a 40 KHz clock signal.

$$f = \frac{1.44}{(R_1 + 2R_2)C}$$

$$D = \frac{R_1}{R_1 + R_2} 100\% = 50\% \Longrightarrow R_1 = R_2 = R$$

$$\rightarrow f = \frac{1.44}{3RC} = 40 KHz$$

Choose C = 0.1µF, then

$$R = 120\Omega$$

Hence, in order to produce a 40 KHz, 50% duty cycle clock signal

$$R_1 = R_2 = 120\Omega$$

$$C = 0.1\mu F$$

The generated clock signal (40 KHz) is then used to trigger an NPN BJT transistor network (as shown in figure 16) so that it could be amplified before reaching the ultrasonic transmitter unit. The transmitted sound is then propagated in the air, and will be reflected back upon hitting any object within its operating range.

#### 4.5.2 Ultrasonic Receiver

This unit is to detect the reflected ultrasonic sound, and induce an AC voltage with according to how strong the reflect signal is. It means that the induced voltage across the receiver (terminals) will be varied accordingly to how far the object apart from the sensing system (mounted in front of the robot). The following table shows the experimental result obtained by measuring the induced voltage across the receiver terminals while varying the position of the object.

| Table 3         Induced voltage (Peak Voltage- mV) versus Sensing of |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| Sensing distance | Induced Voltage | Sensing distance | Induced Voltage |

|------------------|-----------------|------------------|-----------------|

| 10 cm            | 400 mV          | 60 cm            | 200 mV          |

| 20 cm            | 368 mV          | 70 cm            | 120 mV          |

| 30 cm            | 340 mV          | 80 cm            | 40mV            |

| 40 cm            | 300 mV          | 90 cm            | 10mV            |

| 50 cm            | 248 mV          | 100 cm           | 10mV            |

Figure 18 Ultrasonic receiver

Based on the experimental results as shown in table 3, the receiver circuit is designed carefully in the way that it could detect the object as far as 80 cm apart from its mounted position in front of the robot. Figure 18 shows the circuit schematic of the ultrasonic receiver which includes 5 processing stages as discussed below:

- Receiving stage: Once the receiver unit receives the reflected sound, an AC voltage (sinusoidal) is induced across its terminal.

- **Pre-Amplify**: The induced voltage is then amplified through an inverting amplifying op-amp network at a gain of -50.

$$Gain = -\frac{R18}{R19}$$

, if R18 = 100 KΩ, R19 = 2KΩ, then  $Gain = -50$

If the induced peak voltage is 40 mV at a sensing distance of 80 cm, then after this stage, it will be amplified to 40(50)=2000 mV = 2V but 180 degrees out of phase. However, since the supplies for the op-amp are only +6 V and -6V, the amplified signal is limited or saturated at +6V and -6V as shown in the following table.

| Sensing distance | Induced Voltage | Sensing distance | Induced Voltage |

|------------------|-----------------|------------------|-----------------|

| 10 cm            | 6V              | 60 cm            | 6V              |

| 20 cm            | 6V              | 70 cm            | 6V              |

| 30 cm            | 6V              | 80 cm            | 2V              |

| 40 cm            | 6V              | 90 cm            | 0.5 V           |

| 50 cm            | 6V              | 100 cm           | 0.5V            |

**Table 4**Pre-amplified signal (peak value)

• **Rectifying stage**: is to convert the pre-amplified signal to DC voltage through a simple half wave diode rectifier circuit. The average DC output is calculated through the following formula:

$$V_0 = \frac{V_{in} - 0.7}{\Pi} \cong \frac{V_{in} - 0.7}{3.14}$$

Where  $V_{in}$  is the peak value of the input signal.

0.7 refers to the voltage dropped across the diode

| Sensing<br>distance | Rectified Voltage | Sensing<br>distance | Rectified Voltage |  |

|---------------------|-------------------|---------------------|-------------------|--|

| 10 cm               | 1.68 V            | 60 cm               | 1.68 V            |  |

| 20 cm               | 1.68 V            | 70 cm               | 1.68V             |  |

| 30 cm               | 1.68 V            | 80 cm               | 0.41 V            |  |

| 40 cm               | 1.68 V            | 90 cm               | 0 V               |  |

| 50 cm               | 1.68 V            | 100 cm              | 0 V               |  |

Table 5

Rectified voltage versus sensing distance

• Amplifying stage: this stage is to amplify the rectified signal to a higher level. In order to do this, a non-inverting amplifying op-amp network is designed at a gain of 5.

$$Gain = 1 + \frac{R21}{R20}$$

, if R20 = 1 KΩ, R21 = 4KΩ, then  $Gain = 5$

Comparing stage: this DC amplified signal will be then compared a fixed voltage which could be varied through the variable resistor (R22) (connected to the non-inverting pin of the LM 339 comparator). If R22 is chosen so that the voltage applied to the non-inverting pin is slightly smaller than 0.41 x 5 = 2.05 V, then whenever an object appears within the sensing distance from (10 cm to 80 cm), the output of the comparator will go low and vice versa. This output is then tapped to the PIC 16F84 controller for obstacle detection and avoidance subroutine to be executed.

Table 6

Sensing Distance versus Output Voltage from the comparator

| Sensing<br>distance | Output voltage | Sensing<br>distance | Output<br>voltage |

|---------------------|----------------|---------------------|-------------------|

| 10 cm               | 0              | 60 cm               | 0                 |

| 20 cm               | 0              | 70 cm               | 0                 |

| 30 cm               | 0              | 80 cm               | 0                 |

| 40 cm               | 0              | 90 cm               | 6V                |

| 50 cm               | 0              | 100 cm              | 6V                |

## 4.6 PIC 16F84 MICROCONTROLLER AND ROBOT MOVEMENT

In this project, in order to incorporate the robot movement and the manipulator operation together, three units of PIC 16F84 as the controllers are employed. These three communicate to each other through the relationship of master and slave. The master is solely in charged of the robot movement (i.e. move straight, make a turn, obstacle avoidance) while the slaves are used to control the operation of the manipulator upon getting the triggering signal sent from the master. One is to control the positioning of manipulator arm during pick and placement, the other is in charged of controlling the opening and closing action of the gripper attached to the end of bar 2 (refer to figure 9).

Figure 19 Microcontroller communication block diagram

#### 4.6.1 Robot Programming Functional Blocks

As already discussed, the robot should be able to maneuver according to a predetermined path while avoiding any obstacles blocking its movement. Besides, it is also required to perform simple pick and place tasks. Therefore, the robot programming model should consist of the following functional blocks:

- <u>Navigation</u>: is in charged of all on-surface motion of the robot while communicating with two modules: path planning and obstacle detection and avoidance. However, in this project, the robot movement path is preplanned; therefore, the path planning module is skipped.

- <u>Position tracking</u>: is involved with the problem of estimating the robot location while it is moving within its movement plan. This is done through counting the input pulses from the motor shaft encoders as already discussed in section 4.

- <u>Obstacle detection & Avoidance</u>: is in charged of obstacle detection and avoidance while communicating with the navigation module as well as position tracking module.

- <u>Manipulator & Gripper Control block</u>: is in charged of controlling the pick and place operation of the robot (discussed in section 4.3). It also communicates with the navigation module and also the position tracking module in completing the tasks.

Figure 20 Robot Programming Functional blocks

#### 4.6.2 Movement Plan and Robot Navigation

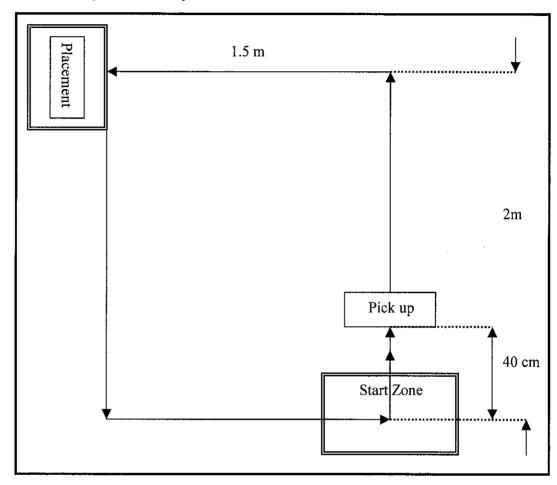

We have set up a movement plan to which the robot is able to follow.

Figure 21 Movement plan

Description:

- The robot starts from its start zone, moves forward about 40 cm to pick up a small object placed anywhere within from 20 cm to 40 cm in front of the robot.

- Upon picking up, it places the object on its carrier platform, travels 160 cm more to complete the 2 m route, makes a left turn, and moves toward to left side for 150 cm.

- The robot is now at its placement location. It places the object well inside the predetermined boundaries, moves reversely for 4 cm, brings its arm up, makes a left turn and returns to its parking position (start zone).

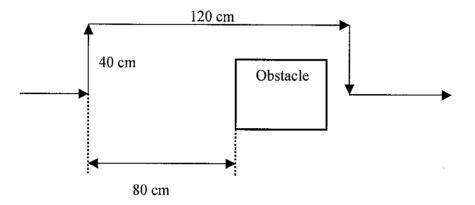

#### 4.6.3 Obstacle Avoidance

While moving accordingly to its predetermined path toward to destination or returning to the parking position, the robot might encounter obstacles. In these conditions, the ultrasonic sensing unit mounted in front of the robot will detect the existence of the obstacle within a sensing distance of 80 cm. An active low signal then triggers the microcontroller to activate its obstacle avoidance subroutine.

Figure 22 A Simple Obstacle Avoidance mechanism

To simulate the situation, the obstacles used to test the obstacle avoidance capability of the robot are boxes; with the fixed size of  $30 \times 30 \times 40$  cm. Figure 22 depicts a simple obstacle avoidance mechanism:

- Upon sensing unit detects the obstacle within a distance of 80 cm, the robot stops. At this point of time, it needs to identify its position referred to the movement plan through counting the pulses input from the wheel encoders.

- To avoid the obstacle, the robot then makes a left turn and moves forward to 40 cm. Based on the object dimension, the robot now escapes from being locked by the obstacle.

- It makes a right turn, moves forward for 120 cm to overcome the obstacle, turns right, again moves forward for 40 cm and makes a left turn eventually to return to its route. At this moment, the robot again needs to identify its position with referring to the movement plan so that it will know how far it has been moving from the start zone as well as how far it is from the destination, and then it only continues to move toward the target.

#### 4.6.4 Some pictures of the robot at work

Figure 23 The robot grasps the object on the floor

Figure 24 During picking up

Figure 25 The robot places the object into a predetermined location

Figure 26 After placement

# CHAPTER 5 CONCLUSION

The project objectives have been successfully met. The robot is not only able to move according to a predetermined plan while avoiding any obstacle blocking its route; but also able to do some simple pick and place tasks. To do all those, the robot programming is consisted of four building functional blocks: (1) Navigation (2) Position tracking (3) Obstacle detection and avoidance (4) Manipulator and gripper control block. The robot has incorporated these mentioned functional blocks by using 3 different units of master-slave communicated PIC 16F84 microcontrollers. The three units of microcontrollers have been working and communicating to each other accordingly, which in turn yields quite a smooth operation of the robot.

To further improve the performance, there are some recommendations as following:

- The manipulator programming needs some fine tuning so that it could operate more smoothly during picking up.

- Currently, there are several types of built-in two-finger gripper available in the market. Therefore, if possible, we could get one to equip to the robot manipulator to enhance the pick and place capability.

- More complicated obstacle avoidance algorithm needs to be implemented so that the robot would be able to react more precisely and effectively towards the changes in its working environment.

- A user interface is also in need to enable the user to select the robot path.

Besides, since this is the first time we have involved in implementing a big-scaled mobile robot, we have encountered a lot of issues, especially with the mechanical structure fabrication. Thus, it would be better if we could be provided a good robot base structure (with the supporting from the UTP mechanical department). Then we would proceed with all the related electrical work instead of implementing the base structure by ourselves (which might contain some mechanical defects, causing some misalignment in the robot movement latter).

#### REFERENCES

- Kortenkamp, Bonasso and Murphy, Artificial Intelligence and Mobile Robot, 1998, AAAI Press / MIT Press.

- [2] Jose A. Castellanos, Mobile Robot Localization and Map Building, 2000, KAP

- [3] Penelope Robert Smith, Active sensors for local planning in mobile robot, 2001, World Scientific.

- [4] Martin David Adams, Sensor Modeling, Design and Data processing for autonomous navigation, 1999, World Scientific.

- [5] Joseph L.Jones, Mobile Robots, 2<sup>nd</sup> edition, 1998, AK Peters

# APPENDIX A PROJECT GENERAL SCHEDULE

|                                   |   |         |          |                       | e<br>S            |             | in<br>S<br>A      |               |         |               |            | TUN AN ANA             | A CONTRACT  |              |

|-----------------------------------|---|---------|----------|-----------------------|-------------------|-------------|-------------------|---------------|---------|---------------|------------|------------------------|-------------|--------------|

| Literature review on mobile robot |   | Цар М   |          |                       | 9 - 5-<br>- 2-1   |             |                   |               |         |               |            |                        |             |              |

| technology.                       |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| Information compilation & basic   |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| conceptual layout.                |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| Detail mechanical & electrical    |   | 19974-0 |          | 2.5.676 <u>6</u> 5299 |                   |             | affi<br>Indiana d | e e circitate |         |               |            |                        |             |              |

| wiring drawing.                   |   |         |          |                       |                   | ല്ല്.<br>ക് |                   |               |         |               |            |                        |             |              |

| Robot assembled, structure built  |   |         |          |                       | in a state of the | //.i        |                   |               |         |               |            |                        |             |              |

| & motor drives & rotational parts |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| design.                           |   |         |          |                       |                   |             |                   |               | ing ang |               |            |                        |             |              |

| Structure stability, reliability, |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| workability test & trouble        |   |         |          |                       |                   |             | •                 |               |         |               | 44.0       | ster (                 |             |              |

| shooting.                         |   |         |          |                       |                   |             |                   |               | 57<br>1 | с. т.<br>С. 4 | ан.<br>Д-4 | 1949 - 1<br>1917 - 194 |             |              |

| Manual control development        |   |         | <u> </u> |                       |                   |             |                   |               |         | <u>C51000</u> |            |                        |             |              |

| Manipulator Implementation        |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| Sensing system + microcontroller  | + |         |          |                       |                   |             | · · · · · ·       |               |         |               |            |                        | <br><u></u> | а 13 на<br>С |

| implementation.                   |   |         |          |                       |                   |             |                   |               |         |               |            |                        | 11          |              |

| Robot optimum operating           |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             | ļ            |

| algorithms & microcontroller      |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             | •.           |

| programming.                      |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

| Improvement & modification        |   |         |          |                       |                   |             |                   |               |         |               |            |                        |             |              |

### **APPENDIX B**

## MECHANICAL DETAIL DRAWING

#

#### B1. Base Structure Drawing (Dimension in cm)

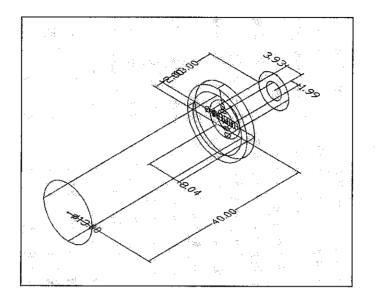

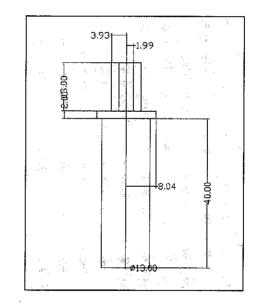

## B2. Coupling Drawing (Dimension in mm)

40

# APPENDIX C PIC 16F84 DATASHEET

.

# PIC16F84A Data Sheet

# 18-pin Enhanced FLASH/EEPROM 8-bit Microcontroller

© 2001 Microchip Technology Inc.

#### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, KEELOQ, SEEVAL, MPLAB and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, Filter-Lab, MXDEV, microID, *Flex*ROM, *fuzzyLAB*, MPASM, MPLINK, MPLIB, PICC, PICDEM, PICDEM.net, ICEPIC, Migratable Memory, FanSense, ECONOMONITOR, Select Mode and microPort are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2001, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELo@ code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

DS35007B - page ii

# **PIC16F84A**

# 18-pin Enhanced FLASH/EEPROM 8-Bit Microcontroller

#### High Performance RISC CPU Features:

- · Only 35 single word instructions to learn

- All instructions single-cycle except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- · 1024 words of program memory

- · 68 bytes of Data RAM

- · 64 bytes of Data EEPROM

- · 14-bit wide instruction words

- · 8-bit wide data bytes

- 15 Special Function Hardware registers

- Eight-level deep hardware stack

- · Direct, indirect and relative addressing modes

- · Four interrupt sources:

- External RB0/INT pin

- TMR0 timer overflow

- PORTB<7:4> interrupt-on-change

- Data EEPROM write complete

#### **Peripheral Features:**

- 13 I/O pins with individual direction control

- High current sink/source for direct LED drive

- 25 mA sink max. per pin

- 25 mA source max. per pin

- TMR0: 8-bit timer/counter with 8-bit programmable prescaler

#### **Special Microcontroller Features:**

- 10,000 erase/write cycles Enhanced FLASH Program memory typical

- 10,000,000 typical erase/write cycles EEPROM Data memory typical

- EEPROM Data Retention > 40 years

- In-Circuit Serial Programming™ (ICSP™) via two pins

- Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own On-Chip RC Oscillator for reliable operation

- · Code protection

- Power saving SLEEP mode

- · Selectable oscillator options

#### **Pin Diagrams**

#### CMOS Enhanced FLASH/EEPROM Technology:

- · Low power, high speed technology

- Fully static design

- Wide operating voltage range:

- Commercial: 2.0V to 5.5V

- Industrial: 2.0V to 5.5V

- Low power consumption:

- < 2 mA typical @ 5V, 4 MHz</li>

- 15 μA typical @ 2V, 32 kHz

- < 0.5 μA typical standby current @ 2V

© 2001 Microchip Technology Inc.

DS35007B-page 1

#### **Table of Contents**

| 1.0 Device Overview                                            | 3  |

|----------------------------------------------------------------|----|

| 2.0 Memory Organization                                        | 5  |

| 0 Data EEPROM Memory                                           | 13 |

| 3.0         Data EEPROM Memory           4.0         I/O Ports | 15 |

| 5.0 Timer0 Module                                              |    |

| 6.0 Special Features of the CPU                                |    |

| 7.0 Instruction Set Summary                                    |    |

| 8.0 Development Support                                        |    |

| 9.0 Electrical Characteristics                                 |    |

| 10.0 DC/AC Characteristic Graphs                               |    |

| 11.0 Packaging Information                                     |    |

| Appendix A: Revision History                                   |    |

| Appendix B: Conversion Considerations                          |    |

| Appendix C: Migration from Baseline to Mid-Range Devices       |    |

| Index                                                          |    |

| On-Line Support                                                |    |

| Reader Response                                                |    |

| PIC16F84A Product Identification System                        |    |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

81. ANS

42h

and to the

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F84A device. Additional information may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023), which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F84A belongs to the mid-range family of the PICmicro<sup>®</sup> microcontroller devices. A block diagram of the device is shown in Figure 1-1.

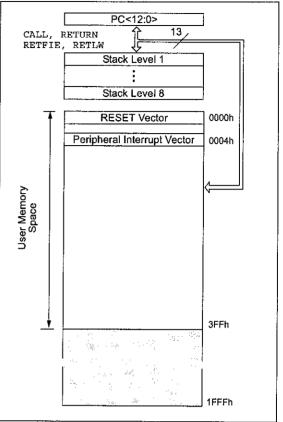

The program memory contains 1K words, which translates to 1024 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 68 bytes. Data EEPROM is 64 bytes.

There are also 13 I/O pins that are user-configured on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- · External interrupt

- · Change on PORTB interrupt

- Timer0 clock input

Table 1-1 details the pinout of the device with descriptions and details for each pin.

#### FIGURE 1-1: PIC16F84A BLOCK DIAGRAM

© 2001 Microchip Technology Inc.

#### TABLE 1-1: PIC16F84A PINOUT DESCRIPTION

| Pin Name         | PDIP<br>No. | SOIC<br>No. | SSOP<br>No. | l/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                            |  |

|------------------|-------------|-------------|-------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC1/CLKIN       | 16          | 16          | 18          | 1             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                  |  |

| OSC2/CLKOUT      | 15          | 15          | 19          | 0             |                        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mod OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |  |

| MCLR             | 4           | 4           | 4           | l/P           | ST                     | Master Clear (Reset) input/programming voltage input. This pin is an active low RESET to the device.                                                                                                   |  |

|                  |             |             |             |               | 1                      | PORTA is a bi-directional I/O port.                                                                                                                                                                    |  |

| RA0              | 17          | 17          | 19          | I/O           | TTL                    |                                                                                                                                                                                                        |  |

| RA1              | 18          | 18          | 20          | I/O           | TTL                    |                                                                                                                                                                                                        |  |

| RA2              | 1           | 1           | 1           | I/O           | TTL                    |                                                                                                                                                                                                        |  |

| RA3              | 2           | 2           | 2           | I/O           | TTL                    |                                                                                                                                                                                                        |  |

| RA4/T0CKI        | 3           | 3           | 3           | I/O           | ST                     | Can also be selected to be the clock input to the<br>TMR0 timer/counter. Output is open drain type.                                                                                                    |  |

| RB0/INT          | 6           | 6           | 7           | 1/0           | TT: (07(1)             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                          |  |

|                  | b<br>I      | Ð           | 7           | I/O           | TTL/ST <sup>(1)</sup>  | RB0/INT can also be selected as an external<br>interrupt pin.                                                                                                                                          |  |

| RB1              | 7           | 7           | 8           | I/O           | TTL                    |                                                                                                                                                                                                        |  |