#### IMPLEMENTATION OF SIMPLESCALAR PORTABLE INSTRUCTION SET ARCHITECTURE (PISA) ON FPGA

By

#### ABDUL AZIM BIN ABDULLAH

#### FINAL PROJECT REPORT

Submitted to the Electrical & Electronics Engineering Programme in Partial Fulfillment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2006 by Abdul Azim bin Abdullah, 2006

#### CERTIFICATION OF APPROVAL

# Implementation of SimpleScalar Portable Instruction Set Architecture (PISA) on FPGA

by

Abdul Azim bin Abdullah

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the BACHELOR OF ENGINEERING (Hons) (ELECTRICAL & ELECTRONICS ENGINEERING)

Approved by,

Lecturer Electrical & Electronic Engineering Universiti Teknologi PETRONAS Bandar Seri Iskandar, 31750 Tronob Perak Darul Ridzuan, Malaysia

#### UNIVERSITI TEKNOLOGI PETRONAS

TRONOH, PERAK

DECEMBER 2006

#### CERTIFICATION OF ORIGINALITY

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

ABDOL AZIM BIN ABDULLAH

# ABSTRACT

This report describes the current progress of final year project entitled Implementation of SimpleScalar Portable Instruction Set Architecture (PISA) on FPGA. The objectives of this study are to learn computer system architecture, to sharpen skill in programming and debugging a program and to complete study in Universiti Teknologi PETRONAS.

Problem statements will explain the reasons behind of this study was conducted. Firstly, there are few microprocessors in the market currently can be reconfigurable. Secondly, there is a need to design a microprocessor which can be used freely for academic purposes. Thus, in this study, we will focus on the designing of a microprocessor that is reconfigurable, easily understood and freely available for academicals purposes.

Methodology will describe way on how this project will be carried out. There are three main steps to be taken which are: 1) Studying the SimpleScalar instruction set architecture; 2) Programming and simulating by using VHDL programming language 3) Implementing the SimpleScalar architecture in VHDL and FPGA.

In the Discussion, a detail contents regarding the project will be explained. Contents included are SimpleScalar's instruction format, register and operation cycle, software and hardware used in the project, the SimpleScalar implementation in VHDL and VHDL simulation. The further details will be discussed later.

Finally, this report is concluded in the Conclusion. Recommendations describe the suggestions that can be done to the current project to improve them in the future.

# ACKNOWLEDGEMENT

Alhamdulillah, after 1 year, this project has reached its end. Lots of experience and knowledge were gained throughout the period. There are several individuals, who should be praised and mentioned here. Without them, this project will not able to be done.

I would like to express the greatest gratitude to Merciful God, Allah S.W.T for His blessings and mercy, which have helped and guided me in during this project.

My almost gratitude goes to my supervisor, Mr. Lo Hai Hiung. He given me advices, ideas, suggestions and ensured that this project will be beneficial to both parties. He supervised me since the first appointment and always kept track of my progress. I really appreciate all the hard work and the time spent, despite his bundle of workload.

I would also like to thank my Computer System Architecture lecturers, Mr. Patrick Sebastian and Dr. Yap Vooi Voon. They were very helpful in giving theoretical, guidance and hands on experience regarding computer architecture. Aside from that, a special thank you to all FYP series lecturers, who was giving me priceless advices on improving my skills in the area of researching, writings and presenting. Not to forget, thanks also to Ms. Siti Hawa who is always supportive.

Last but not least, million thanks to my parents and my fellow colleagues for the all cooperation and support. The encouragement from the people above will always be pleasant memory throughout my life.

# **TABLE OF CONTENTS**

| AI | BSTR         | ACT    |                                      | i  |

|----|--------------|--------|--------------------------------------|----|

| A  | CKNO         | OWLE   | DGEMENT                              | ii |

| 1. | INT          | RODU   | UCTION                               | 1  |

|    | 1.1          | Backg  | ground Study                         | 1  |

|    | 1.2          | Proble | em Statements                        | 2  |

|    | 1.3          | Objec  | tives                                | 3  |

| 2. | LIT          | ERAT   | URE REVIEW                           | 4  |

|    | 2.1          | Simpl  | eScalar Instruction Set Architecture | 4  |

|    |              | 2.1.1  | Instruction Set                      | 4  |

|    |              | 2.1.2  | Instruction Set Architecture         | 5  |

|    | 2.2          | Imple  | mentation on VHDL and FPGA           | 6  |

|    |              | 2.2.1  | VHDL                                 | 6  |

|    |              | 2.2.2  | FPGA                                 | 7  |

| 3. | ME           | THOD   | OLOGY                                | 9  |

| 4. | DIS          | CUSSI  | ONS                                  | 11 |

|    | 4.1          | Instru | ction Format                         | 11 |

|    | 4.2          | Regist | ter                                  | 14 |

|    | 4.3          | Opera  | ation Cycle                          | 16 |

|    | 4.4          | Simpl  | leScalar's Operation Cycle           | 17 |

|    | 4.5          | Softw  | vare                                 | 19 |

|    |              | 4.5.1  | Crimson Editor                       | 19 |

|    |              | 4.5.2  | C Compilers                          | 20 |

|    |              | 4.5.3  | GHDL                                 | 21 |

|    |              | 4.5.4  | Altera Quartus II Web Edition        | 22 |

|    | 4.6 Hardware |        | ware                                 | 25 |

|    |              | 4.6.1  | DSP Development Kit Cyclone II       | 25 |

|    | 4.7 SimpleScalar in VHDL |       | Scalar in VHDL      | 26 |

|----|--------------------------|-------|---------------------|----|

|    |                          | 4.7.1 | Fetch               | 26 |

|    |                          | 4.7.2 | Decode              | 29 |

|    |                          | 4.7.3 | Control             | 31 |

|    |                          | 4.7.4 | Execute             | 33 |

|    |                          | 4.7.5 | Memory              | 35 |

|    | 4.8                      | VHDL  | Simulation          | 38 |

|    |                          | 4.8.1 | Unsigned Addition   | 38 |

|    |                          | 4.8.2 | OR Operation        | 39 |

|    |                          | 4.8.3 | Shift Right Logical | 39 |

| 5. | CON                      | ICLUS | ION                 | 40 |

| 6. | REC                      | COMM  | ENDATIONS           | 41 |

| 7. | REF                      | EREN( | CES                 | 42 |

# LIST OF ILLUSTRATIONS

### LIST OF FIGURES

| Figure 1:  | FPGA Workflow                                          | 8  |

|------------|--------------------------------------------------------|----|

| Figure 2:  | Methodology Steps                                      | 9  |

| Figure 3:  | Instruction Format                                     | 11 |

| Figure 4:  | Instruction Set                                        | 13 |

| Figure 5:  | Register                                               | 14 |

| Figure 6:  | General Operation Cycle                                | 16 |

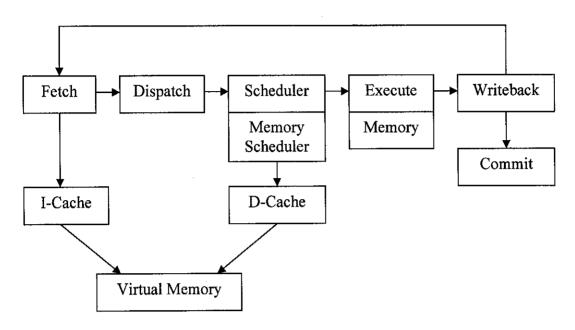

| Figure 7:  | SimpleScalar's Operation Cycle                         | 17 |

| Figure 8:  | SimpleScalar's Operation Cycle (C Language)            | 18 |

| Figure 9:  | Crimson Editor                                         | 19 |

| Figure 10: | Borland C                                              | 20 |

| Figure 11: | GHDL                                                   | 21 |

| Figure 12: | Altera Quartus II Web Edition                          | 22 |

| Figure 13: | Basic Design Flow                                      | 23 |

| Figure 14: | Altera Cyclone II EP2C35 FPGA                          | 25 |

| Figure 15: | SimpleScalar's Operation Cycle (VHDL Implementation)   | 26 |

| Figure 16: | SimpleScalar Instruction (Register & Immediate Format) | 27 |

| Figure 17: | SimpleScalar Opcodes (Register & Immediate Format)     | 29 |

| Figure 18: | SimpleScalar Immediate Fields (Register Format)        | 30 |

| Figure 19: | SimpleScalar Immediate Fields (Immediate Format)       | 30 |

| Figure 20: | Register Selection                                     | 31 |

| Figure 21: | Register-Memory                                        | 32 |

| Figure 22: | 32-bit Full Adder                                      | 34 |

| Figure 23: | Read Cycle Timing Waveforms                            | 36 |

| Figure 24: | Write Cycle Timing Waveforms                           | 37 |

| Figure 25: | Unsigned Addition Operation                            | 38 |

| Figure 26: | OR Operation                                           | 39 |

| Figure 27: | Shift Right Logical                                    | 39 |

# LIST OF TABLES

| Table 1: | Definitions of SimpleScalar Architecture Registers | 15 |

|----------|----------------------------------------------------|----|

| Table 2: | Quartus II Web Edition Device Support              | 22 |

| Table 3: | Full Adder Truth Table                             | 33 |

# TABLE OF APPENDICES

43

# **CHAPTER 1: INTRODUCTION**

### 1.1. Background Study

Modern processors are incrediblely complex marvels of engineering that are becoming increasing hard to evaluate. Simplescalar tool set performs fast, flexible and accurate simulation for modern processors that implement the Simplescalar architecture.

According to D. Burger [1], Simplescalar simulators can emulate the Alpha, PISA, ARM, and x86 instruction sets. The tool set includes a machine definition infrastructure that permits most architectural details to be separated from simulator implementations. All of the simulators distributed with the current release of Simplescalar can run programs from any of the above listed instruction sets. Complex instruction set emulation (e.g., x86) can be implemented with or without microcode, making the Simplescalar tools particularly useful for modeling CISC instruction sets.

The advantages of this tool are flexibility, portability, extensibility and performance. This tool set is portable, requiring only that the GNU tools may be installed on the host system. The tool set has been used on multiple platforms such as Linux/x86, Win NT, SPARC and Solaris. The tool set is easily extensible. The instruction set is designed to support easy annotation of instructions, without requiring a retargeted compiler for incremental changes. The instruction definition method along with the ported GNU tools makes new simulators easy to write and the old ones even simpler to extend. Finally, the simulators have been aggressively tuned for performance and can run codes approaching "real" sizes in tractable amounts of time. [1]

In this project, I will design a Portable Instruction Set Architecture (PISA) microprocessor in VHSIC Hardware Description Language (VHDL) and implement it on FPGA.

The PISA instruction set is a simple MIPS-like instruction set maintained primarily for instructional use. A GNU GCC-based cross-compiler and pre-built libraries are also available for this target. The PISA target is particularly useful for computer engineering instruction as the tools can be built on a wide range of host platforms, including Linux/x86, Win2000, SPARC Solaris, and others. [1]

### **1.2.** Problem Statements

In the current design of microprocessor, there are few microprocessors which can be reconfigurable. "Reconfigurable" term means the memory addressing and registers of the given microprocessor can be adjusted according to the author's preferences. Currently, all microprocessor available in the market, the function units, memory addressing and registers are fixed and cannot be reconfigured. Therefore, this project is attempting to design a microprocessor which is reconfigurable.

Currently, there are a lot of microprocessors designs available today from Intel, Motorola, SPARC and others. However, not all of them are easy to be understood by students who just begin their learning in computer system. In the learning curve, to know and understand the concept of computer system is by learning from the simplest form of digital system, logic circuits until the hardest part, which is the memory system. SimpleScalar, which is based on MIPS, provides an easy and simple architecture for study. In addition, it is free for academic purposes and open source for development. In this project, the simplest microprocessors will be design. From studies made, it is found that Simplescalar PISA can be implemented as a microprocessor. Besides it is free for non-commercial use, it is also reconfigurable and flexible to all platforms. PISA which is like MIPS-like instruction is good architecture for study, because it is easy to understand.

### 1.3. Objectives

#### To implement SimpleScalar PISA in FPGA.

SimpleScalar tool set is used to evaluate modern processors using the SimpleScalar architecture. However, it is only available in software based. The source code must be compiled first before it can be executed. Up to date, there is no hardware based implemented for SimpleScalar PISA. Therefore, in this project, I will implement the SimpleScalar PISA in hardware called FPGA.

#### To design and program circuits using VHDL language.

My interest is programming and I have learnt a lot of languages such as C, C++, HTML, Visual Basic, MATLAB and PHP. I also had experienced in microcontrollers programming. However, VHDL is one of the programming languages I did not manage to learn. Therefore, this project is able to help me to gain new knowledge and experience in programming the digital circuit using VHDL language.

#### To apply and relate computer system architecture.

In the computer system subject, I have learnt digital logic gates, full adder system, basic computer architecture, register design and memory design. From this project, I hope I will be able to apply and relate the concept of computer system subject learnt.

# **CHAPTER 2: LITERATURE REVIEW**

This project can be divided into two major partitions which are SimpleScalar Instruction Set Architecture and Implementation on the VHDL and FPGA.

#### 2.1. SimpleScalar Instruction Set Architecture

### 2.1.1. Instruction Set

Instruction set is a collection of all operations possible in a machine's language. There are many types of instructions in a computer system, such as arithmetic instructions, data movement instructions, control or branch instructions and many more.

In arithmetic instructions, it will accept one or more operands and produce a result. Besides, it may also set a flag to indicate that the result of the operation was a negative number. In data movement instructions, it moves data within the machine and to or from input/output devices. In control or branch instructions, it affects the order in which instructions are performed, or control the flow of the executing program, much as *goto*, *for*, and function calls do in C. [2]

Every instruction must contain encodings within it to specify the following 4 things, either explicitly or implicitly:

- 1. Which operation to perform.

- 2. Where to find the operand or operands, if there are operands.

- 3. Where to put the results, if there is a result.

- 4. Where to find the next instructions.

Source: John L. Hennessy & David A. Patterson, "Computer Architecture: A Quantitative Approach" [2]

In SimpleScalar, the instruction set can be divided into 4 groups, which are:

- 1. Control Instruction

- 2. Load/Store Instruction

- 3. Integer Instruction

- 4. Floating point Instruction

Source: Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [1]

(Refer to Appendix 1: List of Simplescalar Instruction Set for more details)

# 2.1.2. Instruction Set Architecture

Instruction set architecture is the collection of instructions and resources. It includes the instruction set, the machine's memory and all of the programmer-accessible registers in the CPU and elsewhere in the machine. [3]

The SimpleScalar architecture can be divided into parts:

- Instruction set principles.

- Memory hierarchy and register design.

- 5 stages of pipelining.

- Level 1 and level 2 cache.

Source: Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [1]

### 2.2. Implementation on VHDL and FPGA

# 2.2.1. VHDL

VHDL is an acronym of VHSIC Hardware Description Language. VHSIC is another acronym which stands for Very High Speed Integrated Circuits.

In digital design, the VHDL language is used for documentation, verification and synthesis of large digital system. It allows the system can be described in the same code to achieve these goals at one time, thus saving a lot of effort. [6]

There are three different approaches are used to describe hardware in VHDL. They are structural, data flow and behavioral methods of hardware description. In the beginning, the design behaviour is described (modeled) and verified (simulated). By using the synthesis tools, the design is able to be translated into real hardware (gates and wires). At this point, they are mapped onto a programmable logic device such a CPLD or FPGA. [6]

The VHDL standards are developed by IEEE (Institute of Electrical and Electronics Engineers). Currently, there are two standards widely used, which are VHDL'87 (STD 1076-1987) version and VHDL'93 (adopted in 1994). [6]

### 2.2.2. FPGA

FPGA is an acronym which stands for Field Programmable Gate Array. The term of "Field Programmable" refers to the ability to change the operation of the device, while "Gate Array" refers to the matrix of logic cell surrounded by a peripheral of I/O cells. Simply, FPGA are programmable digital logic chips which can be program to do digital function. [7]

FPGAs come in a wide variety of sizes and many different combinations of internal and external features from different manufacturers. Although they are different in many things, they have a common, which is composed of programmable logic blocks. Each of these blocks contains registers and logic elements, which are arranged in a grid and tied together using programmable interconnections. [7]

In a typical FPGA, the logic blocks that make up the bulk of the device are based on lookup tables (of perhaps four or five binary inputs) combined with one or two single-bit registers and additional logic elements such as clock enables and multiplexers. These basic structures may be replicated many thousands of times to create a large programmable hardware fabric. [7]

In more complex FPGAs these general-purpose logic blocks are combined with higherlevel arithmetic and control structures, such as multipliers and counters, in support of common types of applications such as signal processing. In addition, specialized logic blocks are found at the periphery of the devices that provide programmable input and output capabilities. [7]

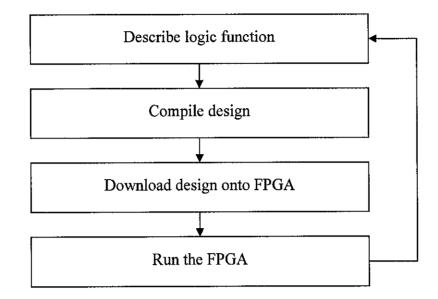

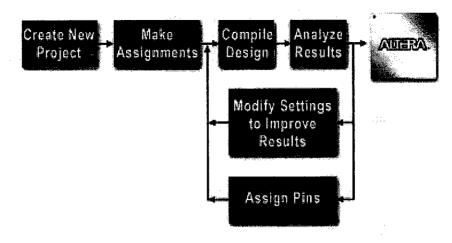

Figure 1 shows the general workflow when working with FPGA.

Figure 1: FPGA Workflow

First step is to describe the logic function that wants to be developed. Draw schematic or write program to describe the particular function.

Then, compile the design. The logic function designed is compiled by using the software provided from FPGA vendor (e.g.: Xilinix ISE, Altera Quartus, Active VHDL and etc). This will create a binary file that can be downloaded into the FPGA.

The next step is to download the design onto FPGA. Connect cable from the computer to the FPGA and download the binary file created to the FPGA.

Finally, run the FPGA. If successfully, the FPGA will behave according to the logic function. If not, repeat the steps again to re-develop.

Source: fpga4fun.com, What are FPGAs? [20]

# **CHAPTER 3: METHODOLOGY**

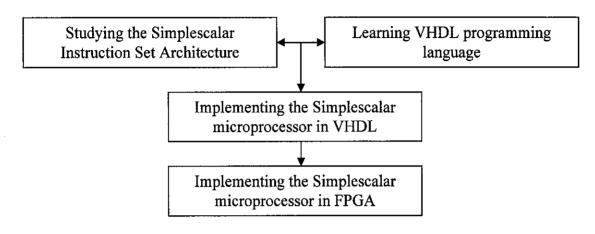

Figure 2: Methodology Steps

Figure 2 above shows the steps I will be taking during implementation of this project. The first part is to study the Simplescalar Instruction Set Architecture. This involves understanding the source code given, what instruction sets are to be used, how to set the memory addressing and registers and many more. Besides that, I also will have to simulate the microprocessors by using the tools given in order to help me to understand how it works.

Parallel with the Simplescalar architecture studies, I will have to learn the VHDL programming language. This requires understanding of the digital system design concepts, writing the source codes and doing some programming exercises given in the books. The software I will be using in VHDL programming is Altera Quartus II software.

Then, I will have to implement the Simplescalar microprocessor in VHDL. This step requires me to convert from the source code given and implement it by using VHDL programming languages I have learnt. This step requires a lot of programming and debugging the program.

Final step of this project is to implement the Simplescalar microprocessor which has been designed by using VHDL on the FPGA. This step requires a lot of programming, debugging the program and troubleshooting the hardware.

The schedule of this project during Final Year Project I and II can be referred to Planning Schedule on Appendix 2: Planning Schedule.

# **CHAPTER 4: DISCUSSIONS**

### 4.1. Instruction Format

The format of an instruction is usually depicted by a rectangular box symbolizing the bits of the instruction, as they appear in memory words or in a control register. The bits are divided into groups or parts called fields. Each field is assigned a specific item, such as the operation code, a constant value, or a register file address. The various fields specify different functions for the instruction and when shown together, constitute instruction format. [9]

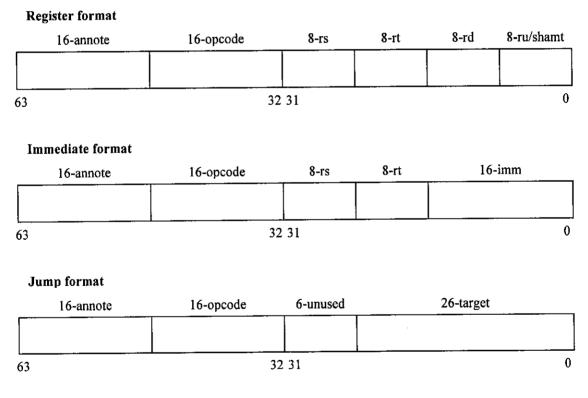

#### **Figure 3: Instruction Format**

Source: Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [1]

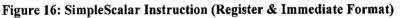

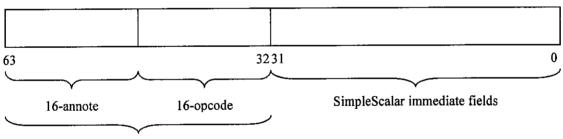

The three instruction formats for the SimpleScalar are illustrated in the Figure 3. SimpleScalar architecture is derived from MIPS-IV instruction set architecture. Therefore, it has same instruction set as MIPS-IV. All instructions are 64 bits in length. The instructions can be divided into three formats: *register*, *immediate* and *jump*. [1]

The register format is used for computational instructions. The immediate format supports the inclusion of a 16-bit constant. The jump format support specification of 24-bit jump targets. The register fields are all 8 bits, to support extension of the architectured registers to 256 integers and floating point register. Each instruction format has a fixed-location, 16-bit opcode field that facilitates fast instruction encodings. [1]

8 bits, 2<sup>8</sup> = 256 integers from 00000000 to 11111111

The bits are divided into groups or parts called fields. Each field is assigned a specific item, such as operation code, a constant value or a register file address.

The operation code of an instruction, often shortened to "opcode", is a group of bits in the instruction format. This determines which operations to be conducted by the processor. The operation of instruction is differentiate by using opcode. For example, the opcode for ADD instruction is 0x40 or 01000000 while the opcode for SUB instruction is 0x44 or 01000100. In SimpleScalar, the opcode is in hexadecimal. However, the opcodes of all instructions are 8 bits. The instruction format for the opcode is 16 bits. Therefore, the remaining 8 bits must be filled by using either zero fill or sign extension. In this architecture, zero-fill is specified for the operand. [1]

Constant value is the immediate value available in the instruction. In SimpleScalar, the value supported for the immediate value is from 0 to 65536. [1]

For full instructions, please refer to Appendix 3: SimpleScalar Instructions for.

File *pisa.def* defines all aspects of the Simplescalar instruction set architecture. Each instruction set in the architecture has a DEFINST macro call. Here, shows example on how the instructions are organized and defined in the source code:

```

#define ADD_IMPL

{

if (OVER(GPR(RS), GPR(RT)))

DECLARE_FAULT(md_fault_overflow);

SET_GPR(RD, GPR(RS) + GPR(RT));

}

DEFINST(ADD, 0x40, opcode

"add", "d,s,t", instruction flags

IntALU, F_ICOMP,

DGPR(RD), DNA, DGPR(RS), DGPR(RT), DNA)

```

**Figure 4: Instruction Set**

Source: Todd M. Austin, "SimpleScalar Hacker's Guide" [8]

Figure 4 shows on how the instruction set is defined in the *pisa.def*. The instruction is ADD arithmetic operation. The operation will involve:

- 1. Reading values from general purpose register of RS and general purpose register of RT.

- 2. Doing the operation, adding between general purpose register of RS and general purpose register of RT.

- 3. Writing (Storing) the results in the general purpose register of RD.

The opcode of this instruction is 0x40 in hexadecimal or 01000000 in binary. Different operation will use different opcode. Since the instruction is arithmetic operation between integers, therefore the functional unit requirement is IntALU. This operation also has helper function which is available to assist in the construction of instruction expression. OVER(GPR(RS), GPR(RT)) function is an overflow checking. This will check whether the results of the operation given have overflow or not. If overflow has occured, a function DECLARE\_FAULT(md\_fault\_overflow) will be called. [8]

# 4.2. Register

This module implements the SimpleScalar architected register state, which includes integer and floating point registers and miscellaneous registers. The architected register state is as follows:

| ger Register File:<br>1 general-purpose r |                   | Miscellaneous Regis | ters:                   |

|-------------------------------------------|-------------------|---------------------|-------------------------|

| \$r0 (src/sink 0)                         |                   | +                   | +<br>  Program Cou      |

| +<br>\$r1                                 | -                 | +                   | +<br>  Mult/Div HI      |

| ++<br>                                    | •                 | LO<br>+             | +<br>  Mult/Div LO<br>+ |

|                                           |                   | <b>•••••</b>        | <b>T</b>                |

| \$r31                                     | -                 | E stational second  |                         |

| ting point Registe                        | double-precision: | -+ +                | 4                       |

| \$f0                                      | \$f1 (for double) |                     | FP codes                |

| \$f1                                      |                   | -+ +                |                         |

|                                           | -                 |                     |                         |

| \$f30                                     | \$f31 (for double |                     |                         |

| \$f31                                     | +                 | -+                  |                         |

|                                           |                   |                     |                         |

Figure 5: Register

Source: SimpleScalar Source Code (regs.h) [10]

The floating point register file can be viewed as either 32 single-precision (32-bit IEEE format) floating point values \$f0 to \$f31, or as 16 double-precision (64-bit IEEE format) floating point values \$f0 to \$f31. [10]

Table below shows the definitions of SimpleScalar architecture register.

| Hardware Name | Software Name | Description                   |

|---------------|---------------|-------------------------------|

| \$0           | \$zero        | zero-valued source/sink       |

| \$1           | \$at          | reserved by assembler         |

| \$2-\$3       | \$v0-\$v1     | fn return result regs         |

| \$4-\$7       | \$a0-\$a3     | fn argument value regs        |

| \$8-\$15      | \$t0-\$t7     | temp regs, caller saved       |

| \$16-\$23     | \$s0-\$s7     | saved regs, callee saved      |

| \$24-\$25     | \$t8-\$t9     | temp regs, caller saved       |

| \$26-\$27     | \$k0-\$k1     | reserved by OS                |

| \$28          | \$gp          | global pointer                |

| \$29          | \$sp          | stack pointer                 |

| \$30          | \$s8          | saved regs, caller saved      |

| \$31          | \$ra          | return address reg            |

| \$hi          | \$hi          | high result register          |

| \$lo          | \$lo          | low result register           |

| \$f0-\$f31    | \$f0-\$f31    | floating point registers      |

| \$fcc         | \$fcc         | floating point condition code |

#### Table 1: Definitions of SimpleScalar architecture registers

Source: Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [1]

These registers defined in SimpleScalar architecture with their hardware name, software name and description. Take note, the registers used by the SimpleScalar is the same with MIPS IV ISA. [1]

# 4.3. Operation Cycle

The basic operation cycle of a computer is controlled by a control unit that puts into the following steps:

Step 1: Fetch the instruction from memory into a control register

- Step 2: Decode the instruction

- Step 3: Locate the operands used by the instruction

- Step 4: Fetch operands from memory (if necessary)

- Step 5: Execute the operation in processor register

- Step 6: Store the results in the proper locations

- Step 7: Repeat Step 1 with next instruction

#### Figure 6: General Operation Cycle

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

There is a register in the computer called the Program Counter (PC) that keeps track of the instructions in the program stored in the memory. The PC holds the address of the instruction to be executed next and is incremented by one each time a word is read from the program in memory. The decoding done in the Step 2 determines the operation to be performed and the addressing mode of the instruction. The operands in Step 3 are located from the addressing mode and the address field of the instruction. The computer executes the instruction, storing the results and returns to Step 1 to fetch the next instruction in sequences. [9]

### 4.4. SimpleScalar's Operation Cycle

Figure 7: SimpleScalar's Operation Cycle

Source: Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [1]

Figure 7 shows the operation cycle of SimpleScalar processors. The concept of SimpleScalar's operation cycle has similar to the general operation cycle we have discussed before. The only different is the term used in Dispatch process, Scheduler process and Writeback process. However, their purpose is the same as the general operation cycle. There are 6 cycles of SimpleScalar processors, which are Fetch, Dispatch, Execute, Writeback and Commit. Each cycle will be discussed later.

```

ruu_init()

for (;;) {

ruu_commit();

ruu_writeback();

lsq_refresh();

ruu_issue();

ruu_dispatch();

ruu_fetch();

}

```

#### Figure 8: SimpleScalar's Operation Cycle (C Language)

Source: SimpleScalar Source Code (sim-outorder.c) [10]

Figure 8 shows the C language implementation of the SimpleScalar's operation cycle. In *sim-outorder.c*, this operation cycle is implemented as pipelining. It is implemented reversely from Commit to Fetch. According to Doug Burger, this will eliminate this/next state synchronization and relaxation problems. [1]

### 4.5. Software

For this project to be completed and successful, I have used software for development. There are editors, compilers, synthesizers and simulators software. The development platform of this project will be under Windows XP operating system.

### 4.5.1. Crimson Editor

**Figure 9: Crimson Editor**

Crimson Editor is a professional source code editor for Windows platform. It can be downloaded free from the Internet at <u>http://www.crimsoneditor.com/</u>.

This software supports many programming languages such as HTML, C/C++, Perl, Java and even VHDL. One features of this editor is it enables syntax highlighting of all programming languages and can be extend for other programming languages. [11]

## 4.5.2. C Compilers

Figure 10: Borland C

I have used two C compilers, which are Borland C and Microsoft Visual Studio. Both programs can be used to edit, view and compile a C source codes. However, I will not be using this program to compile the SimpleScalar source codes. Rather than, these programs are used to check and test the SimpleScalar source codes. These involving checks the size of an arrays, the syntax used and variables used in the SimpleScalar source code.

### 4.5.3. GHDL

Figure 11: GHDL

GHDL is one of software I had used in this final year project. GHDL is a VHDL simulator, using the GCC technology and implementing the VHDL language according to the VHDL 1987 (IEEE 1076-1987) and VHDL 1993 (IEEE 1076-1993) standards. With GHDL, the program and designed written in VHDL can be compiled into executable files. With the binary files created from compilation, the design can be simulated. [12]

GHDL is an open source project and is free under GNU General Public License. Under the GNU license, this software can be redistributed and modified. It is free from restriction and license issues that arise with commercial simulators. Currently, there are two processors which are successfully compiled and run by using GHDL. There are DLX processors and LEON1 SPARC processors. [12]

However, it has disadvantage over the commercial simulator software. The design created does not be able to synthesis. It cannot translate the design into netlist and not be able to transfer onto FPGA. [12]

# 4.5.4. Altera Quartus II Web Edition

Figure 12: Altera Quartus II Web Edition

The main software for VHDL development will be Quartus II Web Edition. This software can be obtained free from Altera site, <u>http://www.altera.com/</u>. A license is required and it can be enquired freely at the particular website. This software supports Cyclone II of device family, which is the hardware that I will be using for FPGA. [13]

| Device Family          | Device Supported |

|------------------------|------------------|

| MAX II                 |                  |

| MAX 3000A              |                  |

| MAX 7000AE             |                  |

| MAX 7000B              |                  |

| MAX 7000S              | All devices      |

| Cyclone II             |                  |

| Cyclone                |                  |

| FLEX 10K <sup>®</sup>  |                  |

| FLEX <sup>®</sup> 10KA |                  |

| ACEX®                  |                  |

| FLEX 6000              |                  |

#### Table 2: Quartus II Web Edition Device Support

Source: Altera, Quartus II Web Edition Software [13]

Figure 13: Basic Design Flow

Source: Altera, Quartus II Software Basic Design Flow [13]

Figure 13 shows the basic design flow for the Quartus II software. The users can set up project and compile the design by using these steps. Altera defines 6 stages of developing the VHDL. [13]

The first stage is creating new project. At this stage involves declaration of entity or component, design files and libraries used in the project, and the device family and package used by the project. Next is making assignments. This stage requires specifying global maximum operating frequency requirements (fMAX), paths should not be reported in timing analysis reports and others. [13]

The next step will be compile design and analyzed the results. Before the project can be simulated and implemented, the project must be verified first. Here, each syntax of entity, component and architecture developed are checked. After compiling the design, a report summary of compiled results will be shown automatically. This report shows all the place-and-route results details and it is linked to many other software features. [13]

At the same time, if the results are not satisfied and we want to improve the current results, it can be changed by using assignment settings assignment editors) or by changing timing requirements in the Timing Wizard. Then, the design is compiled again and the results are analyzed. By default, the software will automatically assign pins to the top-level I/O signals. It also can be done by manual using the Assignment Editor. [13]

### 4.6. Hardware

# 4.6.1. DSP Development Kit Cyclone II

Figure 14: Altera Cyclone II EP2C35 FPGA

Figure 14 shows the hardware that I will be using to implement the SimpleScalar processor on it. The hardware is Cyclone II EP2C35 FPGA. An overview is summarized:

- Logic Elements: 33,216

- M4K RAM Blocks (4 kbits + 512 Parity Bits): 105

- Total RAM Bits: 483,840

- Embedded 18x18 Multipliers: 35

- PLLs: 4

- Maximum User I/O Pins: 475

- Differential Channels: 205

Source: Cyclone II FPGA Family Overview [13]

### 4.7. SimpleScalar in VHDL

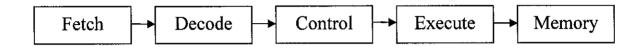

In this section, I will describe the VHDL implementation of SimpleScalar processors. In the implementation, the processors are divided into five cycles, which are Fetch, Decode, Execute and Memory.

Figure 15: SimpleScalar's Operation Cycle (VHDL Implementation)

### 4.7.1. Fetch

In the Fetch cycle, the stored instructions are bring out from the memory and send to the bus line. Then, these instructions will be decoded in the Decode cycle.

```

Source: fetch.vhd [Appendix IV]

```

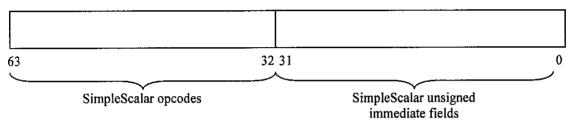

The SimpleScalar instructions can be divided into two sections as defined in the C languages, which are SimpleScalar opcodes and SimpleScalar unsigned immediate fields. Each section is an unsigned word data type and has 32 bit width.

typedef struct {

word\_t a;

word\_t b;

/\* simplescalar opcode (must be unsigned) \*/

word\_t b;

/\* simplescalar unsigned immediate fields \*/

} md\_inst\_t;

Source: SimpleScalar Source Code (pisa.h) [10]

#### Register & Immediate format

Source: SimpleScalar Tools Set [1]

SimpleScalar unsigned immediate fields are 32-bit from bit 0 till bit 31 of SimpleScalar instructions and SimpleScalar opcodes are also 32-bit from bit 32 till bit 63. The instructions are fetched from the memory accordingly to the program counter by using function MD\_FETCH\_INST. (See the source code below)

1

#define MD\_FETCH\_INST(INST, MEM, PC)

{ inst.a = MEM\_READ\_WORD(mem, (PC));

inst.b = MEM\_READ\_WORD(mem, (PC) + sizeof(word\_t)); }

```

MD_FETCH_INST(inst, mem, regs.regs_NPC);

```

Source: SimpleScalar Source Code (pisa.h, sim-fast.c) [10]

```

process(PC)

begin

case PC is

when X"00" =>

insta <= mem0;

instb <= mem1;

...

when X"2C" =>

insta <= mem22;

instb <= mem23;

when others =>

insta <= null;

instb <= null;

end case;

end process;</pre>

```

Source: fetch.vhd [Appendix IV]

Source code above shows on how the instructions are fetched using VHDL language. When the PC is X"00", the instruction at mem0 will be sent to insta (as SimpleScalar opcode) and another instruction at mem1 will be sent to instb (as SimpleScalar immediate fields).

```

entity fetch is

port(insta : out bit_vector(31 downto 0); -- inst.a

instb : out bit_vector(31 downto 0); -- inst.b

PCin : in bit_vector(7 downto 0); -- PC

clock, reset : in std_logic);

end fetch;

```

Source: fetch.vhd [Appendix IV]

In *fetch.vhd*, there are three inputs, which are the PC (program counter), clock and reset and two outputs, which are insta and instb. insta is the SimpleScalar opcodes and instb is the SimpleScalar immediate fields. These outputs will be the inputs during Decode cycle.

(Refer to Appendix IV: fetch.vhd for the source code)

#### 4.7.2. Decode

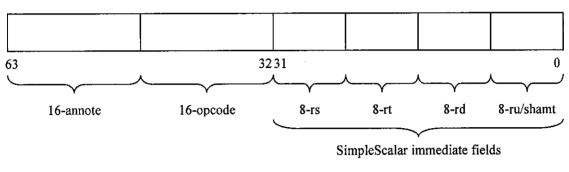

In Decode cycle, the fetched instructions will be translated into specific fields, which are OP (opcode), RS (register source #1), RT (register source #2), RD (register destination) and IMM (immediate value). The implementation of Decode cycle in C language can be seen as follows:

```

/* returns the opcode field value of SimpleScalar instruction INST */#define MD_OPFIELD(INST)#define MD_SET_OPCODE(OP, INST)((OP) = ((INST).a & 0xff))

```

| /* integer registe | r specifiers */                          |                     |

|--------------------|------------------------------------------|---------------------|

| #undef RS          | /* defined in /usr/include/sys/syscall.h | 1 on HPUX boxes */  |

| #define RS         | (inst.b >> 24)                           | /* reg source #1 */ |

| #define RT         | ((inst.b >> 16) & 0xff)                  | /* reg source #2 */ |

| #define RD         | ((inst.b >> 8) & 0xff)                   | /* reg dest */      |

Source: SimpleScalar Source Code (pisa.h) [10]

#### **Register & Immediate format**

SimpleScalar opcodes

#### Figure 17: SimpleScalar Opcodes (Register & Immediate Format)

Source: SimpleScalar Tools Set [1]

Figure 17 shows the SimpleScalar opcodes for Register and Immediate format. In the SimpleScalar opcodes, there will be two fields, which are annote and opcode. In the annote field, the SimpleScalar allows new instructions to be added or implemented into the current instruction set. The length of this field is 16 bit. In the opcode field, the SimpleScalar operation codes are defined. In other words, any operations of the instructions to be executing will be depending to this field. For example, in SimpleScalar,

the addition between two registers will happen when the opcode is 0x40. If the instruction fetched having the opcode of 0x40 in this field, the addition will be executed. Otherwise, another operation will be executed depending on the opcodes.

#### **Register format**

Figure 18: SimpleScalar Immediate Fields (Register Format)

Figure 19: SimpleScalar Immediate Fields (Immediate Format)

Figure 18 and 19 shows the SimpleScalar Immediate Fields. For Register format, there are 4 fields and for Immediate format, there are only 3 fields. In Register format, there are 8 bit register source #1 (RS), 8 bit register source #2 (RT), 8 bit register destination (RD) and 8 bit register shift arithmetic (RU/SHAMT). In Immediate format, there are 8 bit register source (RS), 16 bit immediate value (IMM) and 8 bit register destination (RT).

(Refer to Appendix IV: decode.vhd for the source code)

#### 4.7.3. Control

The purpose of Control cycle is to control the movement of data between the register and the memory.

```

ra_bus : out bit_vector(31 downto 0);

wa_bus : out bit_vector(31 downto 0);

reg_wrt : out std_logic;

reg_dst : out std_logic;

```

#### Source: control.vhd [Appendix IV]

For register design, there are two outputs, which are reg\_wrt and reg\_dst. reg\_wrt is required to control the writing process onto the register while reg\_dst is required to select which destination the register will be writing onto during the writeback.

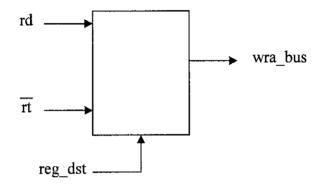

Figure 20: Register Selection

wra\_bus <= rt when reg\_dst='1' else rs;

Source: decode.vhd[Appendix IV]

Figure 20 shows the register selection. The purpose is to select which registers, either RS register or RT register during writeback.

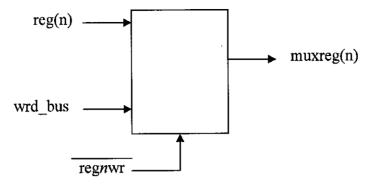

Figure 21: Register-Memory

```

\label{eq:reg0wr} $$ reg0wr <= '1' when ((wra_bus = "00000000") and (reg_wrt='1')) else '0'; reg1wr <= '1' when ((wra_bus = "00000001") and (reg_wrt='1')) else '0'; reg2wr <= '1' when ((wra_bus = "00000010") and (reg_wrt='1')) else '0';

```

muxreg(0) <= reg(0) when reg0wr='0' else wrd\_bus; muxreg(1) <= reg(1) when reg1wr='0' else wrd\_bus; muxreg(2) <= reg(2) when reg2wr='0' else wrd\_bus;</pre>

This design will select the register output between the intermediate register and the memory. Immediate register is the current register during operation and labeled as reg(n), where n is between 0 to 31.

(Refer to Appendix IV: control.vhd for the source code)

Source: decode.vhd[Appendix IV]

#### 4.7.4. Execute

In Execute cycle, the operation of an instruction will be carry out. The selection of which operations will be executing is done by opcode field. In this section, only integer instructions are implemented. Integer instruction

In arithmetic, the operation involves unsigned addition without overflow checking, unsigned subtraction without overflow checking and unsigned multiplication without overflow checking. In logical, the operation involves AND-operation, OR-operation, XOR-operation and NOR-operation. Other operations are shift arithmetic left and shift arithmetic right. Here, an unsigned addition will be explained.

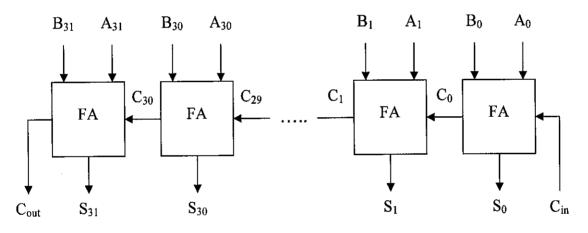

Full adder is a combinational circuit that performs the arithmetic addition of three inputs and produces two outputs. Two of the inputs are two bits to be added while another input is the carry bit from previous adder (if any). Three inputs are denoted by A, B and  $C_{in}$ . Two outputs are needed and denoted by S and  $C_{out}$ . [9]

|   | Inputs |     | Out  | puts |

|---|--------|-----|------|------|

| Α | B      | Cin | Cout | S    |

| 0 | 0      | 0   | 0    | 0    |

| 0 | 0      | 1   | 0    | 1    |

| 0 | 1      | 0   | 0    | 1    |

| 0 | 1      | 1   | 1    | 0    |

| 1 | 0      | 0   | 0    | 1    |

| 1 | 0      | 1   | 1    | 0    |

| 1 | 1      | 0   | 1    | 0    |

| 1 | 1      | 1   | 1    | 1    |

The truth table for full adder:

#### Table 3: Full Adder Truth Table

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

The simplified sum-of-product functions of two outputs are:

$$S = \overline{A} \overline{B} \overline{C}_{in} + \overline{A} \overline{B} \overline{C}_{in} + \overline{A} \overline{B} \overline{C}_{in} + ABC$$

$$C = AB + BC + AC$$

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

This implementation requires seven AND gates and 2 OR gates. However, the operation can be simplified into the simplest form which is can be expressed as:

$$S = (A \oplus B) \oplus C_{in}$$

$$C = AB + C_{in} (A \oplus B)$$

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

Figure 22: 32 bit Full Adder

Figure 22 shows the visual aid of 32-bit full adder implemented.

result(index) := op1(index) xor op2(index) xor carry; carry := (op1(index) and op2(index)) or (carry and (op1(index) xor op2(index)));

Source: execute.vhd [Appendix IV]

(Refer to Appendix IV: execute.vhd for the source code)

#### 4.7.5. Memory

In Memory cycle, the operations which memory always performs are writing and reading. Writing is when the data is transfer into the memory to be stored. Reading is when the data stored is retrieved out from the memory.

rd\_bus stands for read data from the memory, ra\_bus is the read address from bus line, wd\_bus write data to the memory and wa\_bus is the write address to the bus line. rd\_bus acts as output while ra\_bus. wd\_bus and wa\_bus acts as inputs to the *memory.vhd*. mem\_wrt, mem\_red, mem\_reg are the inputs from the Control cycle.

rd\_bus : out bit\_vector(31 downto 0); ra\_bus : in bit\_vector(31 downto 0); wd\_bus : in bit\_vector(31 downto 0); wa\_bus : in bit\_vector(31 downto 0); mem\_wrt : in std\_logic; mem\_red : in std\_logic; mem\_reg : in std\_logic; clock, reset : in std\_logic;

Source: memory.vhd[Appendix IV]

In this project, the implementation of SimpleScalar memory is not successfully. By part, the data is managed to be read from the memory and store into the given memory location. However, during the Execute cycle, the data is unable to retrieve back.

Given example, a data of 32 bit of X"00001010" is stored at memory location addressing X"00000010". During execution, the data X"00001010" is unable to be retrieve. A further work can be done to investigate this error.

In this section, the information provided the general how the instructions are read from and store into the memory.

#### <u>Read</u>

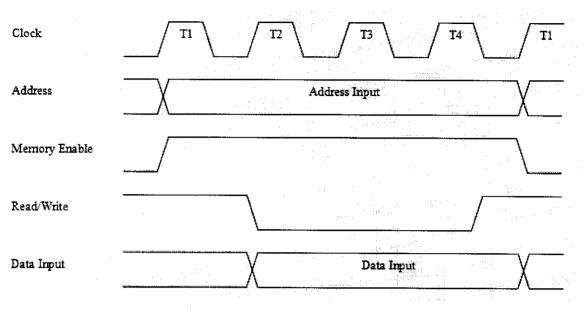

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

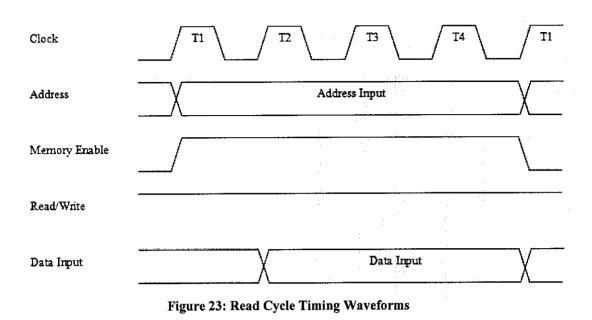

Figure 23 shows the read cycle timing waveforms of general memory design. Steps taken for read operation:

- 1. Apply the binary address of the desired word into address lines.

- 2. Active the Read input.

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

#### <u>Write</u>

Figure 24: Write Cycle Timing Waveform

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

Figure 24 shows the write cycle timing waveforms of general memory design. The steps that must be taken for a write operation:

- 1. Apply the binary address of the desired word into address lines.

- 2. Apply the data bits that must be stored in memory to the data input lines.

- 3. Active the Write input.

Source: M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals" [9]

(Refer to Appendix IV: memory.vhd for the source code)

#### 4.8. VHDL Simulation

From the implementation in VHDL, only integer instructions were implemented. They are unsigned addition, unsigned subtraction, unsigned multiplication, AND-operation, OR-operation, XOR-operation, NOR-operation, shift left logical and shift right logical. In the VHDL simulation, assumptions have been made:

- 1. Only functional are tested.

- 2. The RS register stored value of 0x00001010 and RT register stored value of 0x0000100F.

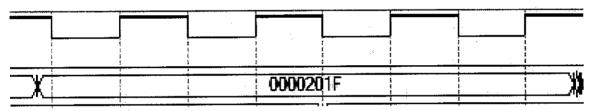

#### 4.8.1. Unsigned Addition

Figure 25: Unsigned Addition Operation

Figure 25 show the result of an addition operation. The operation does not require overflow checking. The addition operation in hexadecimal and binary form:

| Hexadecimal | Binary                                  |

|-------------|-----------------------------------------|

| 0x00001010  | 000000000000000000000000000000000000000 |

| +0x0000100F | +00000000000000000000000001111          |

| 0x0000201F  | 000000000000000000000000000000000011111 |

The result of 0x0000201F will be stored at register RD.

#### 4.8.2. OR Operation

|   |       | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | F<br>C<br>L |  |

|---|-------|---------------------------------------------------------------------------------------------|-------------|--|

| ₩ | 00001 | 1F                                                                                          |             |  |

Figure 26: OR Operation

Figure 26 show the result of an OR operation. The OR operation:

| Hexadecimal | Binary                                  |

|-------------|-----------------------------------------|

| 0x00001010  | 000000000000000000000000000000000000000 |

| 0x0000100F  | 000000000000000000000000000000001111    |

| 0x0000101F  | 00000000000000000000000000000000011111  |

The result of 0x0000101F will be stored at register RD.

#### 4.8.3. Shift Right Logical

| ······································ |   |        | · · · · · · · · · · · · · · · · · · ·                                                      |          |

|----------------------------------------|---|--------|--------------------------------------------------------------------------------------------|----------|

| <b></b>                                |   |        |                                                                                            |          |

|                                        |   |        | . · · · · · ·                                                                              |          |

|                                        |   |        |                                                                                            |          |

| ļ                                      | 1 |        | 1                                                                                          |          |

| 2                                      | 3 | Į.     |                                                                                            |          |

|                                        |   | 1      |                                                                                            |          |

| h                                      |   | ······ |                                                                                            |          |

| · · · · · · · · · · · · · · · · · · ·  | 1 | 00000  | 7/73                                                                                       |          |

| - 6                                    |   |        |                                                                                            |          |

| <b>L</b> Š                             |   | 00000  |                                                                                            | <u> </u> |

| 1                                      | 1 |        | <ul> <li>A. C. M. Martine, and M. M. Martine, Mathematical Society, 1987, 1987.</li> </ul> |          |

Figure 27: Shift Right Logical

Figure 27 show the shift right logical operation. The operation:

| 0x0000100F >> 1 | 000000000000000000000000000000000000000 |

|-----------------|-----------------------------------------|

| 0x00000807      | 00000000000000000010000000111           |

The result of 0x00000807 will be stored at register RD.

#### **CHAPTER 5: CONCLUSION**

From the project that will be done, I hope I will be able to fulfill objectives as described above. This project is well-done and is only able to be functional in VHDL simulation. However, this project is not yet completed within timeframe given. There were several reasons contributing to this cause. They were development progress and synthesizable problem.

Most of the development in this project spent on studying the C source code of SimpleScalar and the VHDL programming. A lot of exercises and examples done in C and VHDL programming before started the project. The lack of source codes available in the Internet makes the project has to be started from scratch. Thus, it takes longer than expected.

Another reason contributes to the project is the VHDL implemented are not synthesizable. During the project, I found a DLX source code, which is similar to MIPS architecture. I had developed the SimpleScalar architecture on it. However, when I tried to compile the source code, it was not synthesizable. Before downloading onto FPGA, it requires the source code to be synthesized first. When it comes to this, the project schedule is delayed.

Only integer instructions were implemented. They are unsigned addition, unsigned subtraction, unsigned multiplication, AND-operation, OR-operation, XOR-operation, NOR-operation, shift left logical and shift right logical.

In this project, the implementation on FPGA was unsuccessful. The code developed is able to be downloaded on the FPGA. However, when I tried to run the FPGA, the board does not working as expected.

#### **CHAPTER 6: RECOMMENDATIONS**

#### Redesign the Control Module

In this project, I have implemented the Control module which is between the Decode and Execute modules. The purpose of this module is to control the data movement between register and memory. However, in this project, this module is not working perfectly. Therefore, for future works, I recommend to redesign the Control module.

#### Implement Other Instructions

In this project, only integer instructions were implemented. Others instructions such as control instructions, load and store instructions, and floating point instructions are not implemented yet. In the future, I recommend implementing other types of instructions.

#### Program on FPGA

In this project, the program on FPGA was unsuccessful. The current source code is divided into 5 architectures for ease of use. Each module has own purposes as described earlier. In the future, to program on the FPGA, I recommend to test and program each module separately. This might be able to help them to troubleshoot the source code and solve the problem.

#### **CHAPTER 7: REFERENCES**

[1] Doug Burger, Todd M. Austin, "The SimpleScalar Tool Set, Version 2.0" [2] John L. Hennessy & David A. Patterson, "Computer Architecture: A Quantitative Approach", 2003, Third Edition, Morgan Kaufmann Publishers. [3] Vincent P. Heuring & Harry F. Jordan, "Computer Systems Design and Architecture", 2004, Second Edition, Pearson Prentice Hall. [4] SimpleScalar LLC, http://www.simplescalar.com/ [5] SimpleScalar Tools Home Page, http://www.cs.wisc.edu/~mscalar/simplescalar.html [6] VHDL Tutorial, http://www.gmvhdl.com/introduc.htm/ [7] FPGA as Computing Platform, http://www.informit.com/articles/article.asp?p=382614&rl=1 [8] Todd M. Austin, "SimpleScalar Hacker's Guide" [9] M. Morris Mano, Charles R. Kime, "Logic and Computer Design Fundamentals", 2004, Third Edition, Pearson Prentice Hall. [10] SimpeScalar Source Code [11] Homepage of Crimson Editor, http://www.crimsoneditor.com/ [12] GHDL home page, <u>http://ghdl.free.fr/</u> [13] Altera, http://www.altera.com/ [14] Cyclone II FPGA Overview, http://www.altera.com/products/devices/cyclone2/overview/cy2-overview.html [15] Charles Price, "MIPS Instruction Set", Revision 3.2, September 2005 [16] Todd Austin, Eric Larson, Dan Ernst, "SimpleScalar: An Infrastructure for Computer System Modeling", February 2002, IEEE Journal

[17] Douglas L. Perry, "VHDL Programming by Example", 2002, Fourth Edition, McGraw Hill

- [18] H.M. Deitel, P.J. Deitel, "C How To Program", 2001, Third Edition, Prentice Hall

- [19] The Hamburg VHDL Archive, http://tams-www.informatik.uni-hamburg.de/vhdl/

- [20] fpga4fun.com, What are FPGAs?, http://www.fpga4fun.com

### **TABLE OF APPENDICIES**

## Appendix 1

List of Simplescalar Instruction Set

|             | • • •                             | hle hand to 0                        |

|-------------|-----------------------------------|--------------------------------------|

| Control     | j – jump                          | $blez - branch \le 0$                |

|             | jal – jump and link               | bgtz - branch > 0                    |

|             | jr – jump register                | bltz - branch < 0                    |

|             | jalr – jump and link register     | $bgez - branch \ge 0$                |

|             | beq - branch == 0                 | bct – branch FCC TRUE                |

|             | bne – branch $!= 0$               | bcf – branch FCC FALSE               |

|             |                                   |                                      |

| Load/Store  | lb – load byte                    | l.d – load double-precision FP       |

| Louis otore | lbu – load byte unsigned          | sb – store byte                      |

|             | lh – load half (short)            | sbu – store byte unsigned            |

|             | lhu - load half unsigned          | sw – store word                      |

|             | lw – load word                    | dsw – store double word              |

|             | dlw – load double word            | s.s – store single-precision FP      |

|             | l.s – load single-precision FP    | s.d – store double-precision FP      |

|             |                                   | F                                    |

| Integer     | add – integer add                 | or – logical OR                      |

|             | addu – integer add unsigned       | xor – logical XOR                    |

| Arithmetic  | sub – integer subtract            | nor – logical NOR                    |

|             | subu – integer subtract unsigned  | sll – shift left logical             |

|             | mult – integer multiply           | srl – shift right logical            |

|             | multu – integer multiply unsigned | sra – shift right arithmetic         |

|             | div – integer divide              | slt – shift less than                |

|             | divu – integer divide unsigned    | sltu – shift less than unsigned      |

|             |                                   | situ – sinit iess than unsigned      |

|             | and – logical AND                 |                                      |

|             |                                   |                                      |

| Floating    | add.s - single-precision (SP) add | abs.d – DP absolute value            |

| Point       | add.d – double-precision (DP) add | neg.s – SP negation                  |

| Arithmetic  | sub.s – SP subtract               | neg.d – DP negation                  |

|             | sub.d – DP subtract               | sqrt.s – SP square root              |

|             | mult.s – SP multiply              | sqrt.d – DP square root              |

|             | mult.d – DP multiply              | cvt – int, single, double conversion |

|             | div.s – SP divide                 | c.s – SP compare                     |

|             | div.d – DP divide                 | c.d – DP compare                     |

|             | abs.s – SP absolute value         |                                      |

|             |                                   |                                      |

| 1           |                                   |                                      |

# Appendix 2 Planning Schedule

#### Final Year Project I

|   |                                  | 1   | 2                          | 3          | 4              | 5                         | 6           | 7 | 8              | 9      | 10         | 11 | 12       | 13              | 14       |

|---|----------------------------------|-----|----------------------------|------------|----------------|---------------------------|-------------|---|----------------|--------|------------|----|----------|-----------------|----------|

| 1 | FYP Titles                       |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | FYP Briefing                     | ржя |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Selection of FYP Titles          |     | ار میکرد ا <sup>ر</sup> بن |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   |                                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

| 2 | FYP Submissions                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Log Book                         |     |                            |            | iliana         |                           |             |   | <u>, s</u>     | ç4lır: |            |    |          | 3 - 1<br>       |          |

|   | Preliminary Report               |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Progress Report                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Interim Report First Draft       |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Interim Report Final Draft       |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Oral Presentation                |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Interim Report Final             |     | Ċ                          |            |                |                           |             |   |                |        |            |    |          |                 | <u>.</u> |

|   |                                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

| 3 | Meetings                         |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Supervisor                       |     |                            |            |                | U.V.S.M.                  | €"11"<br>   |   | - 300<br>      |        | ni≡".<br>  |    |          |                 | 2011     |

|   |                                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

| 4 | Project Development              | ļ   |                            | STREET, ST |                |                           |             |   |                |        |            |    |          |                 |          |

|   | Installing the Programs Required |     |                            | 10,000     |                | WARTIN AL                 | per.wattry. |   |                |        |            |    |          |                 |          |

|   | Learning the Programs Required   |     |                            |            |                |                           |             |   | المرد المرد ال |        | ы.<br>Алт. |    | 2320     |                 | 5.S.     |

|   | Learning the VHDL                |     |                            |            | <i>33</i> (12) |                           | 2           |   |                |        |            |    |          |                 |          |

|   | Programming the VHDL             |     |                            |            |                | ener 29 (n.<br>Anterstein |             |   |                |        |            |    |          | -<br>Brite      | i di     |

|   | Understanding the Source Code    |     |                            |            |                |                           |             |   |                | y sub  |            |    | andonija | e in all of the |          |

|   | Source Code -> VHDL              |     |                            |            |                |                           | 2.111       |   |                | Kara   | <u></u>    |    | 1        |                 |          |

|   |                                  |     |                            |            |                |                           |             |   |                |        |            |    |          |                 |          |

#### Final Year Project II

|   |                               | 1        | 2  | 3         | 4 | 5     | 6 | 7                                         | 8 | 9  | 10           | 11 | 12 | 13 | 14 |

|---|-------------------------------|----------|----|-----------|---|-------|---|-------------------------------------------|---|----|--------------|----|----|----|----|

|   |                               |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

| 1 | FYP Submissions               |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Log Book                      |          | ÷. | . <u></u> | - |       |   | a ideal                                   |   | -, |              |    | •  |    |    |

|   | Progress Report               |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Interim Report First Draft    |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Interim Report Final Draft    |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Oral Presentation             |          |    |           |   |       |   |                                           |   |    |              |    |    | 1  |    |

|   | Interim Report Final          | <u> </u> |    |           |   |       |   | ┝                                         |   |    |              | -  |    |    | 6  |

| 2 | Meetings                      |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Supervisor                    |          |    |           | T | 1     |   | rightig<br>Linger (                       |   | i  | تيا (أفر)    |    |    |    |    |

| 3 | Project Development           |          |    |           |   |       |   |                                           |   |    |              |    |    |    |    |

|   | Understanding the Source Code |          | -  |           |   |       |   | 28.25                                     |   |    |              |    |    |    |    |

|   | Programming the VHDL          |          |    | į         | Ī | -<br> | 1 | in an |   |    | iiiiiii<br>I |    |    |    |    |

# Appendix 3

### SimpleScalar Instructions

# **Control Instruction**

| Instructions                            | Opcode | Mnemonic | Format             |

|-----------------------------------------|--------|----------|--------------------|

| Jump to absolute address                | 0x01   | ſ        | J target           |

| Jump to absolute address and link       | 0x02   | JAL      | JAL target         |

| Jump to register address                | 0x03   | JR       | JR rs              |

| Jump to register address and link       | 0x04   | JALR     | JALR rs            |

| Branch if equal                         | 0x05   | BEQ      | BEQ rs, rt, offset |

| Branch if not equal                     | 90×0   | BNE      | BEQ rs, rt, offset |

| Branch if less than or equal to zero    | 0x07   | BLEZ     | BLEZ rs, offset    |

| Branch if greater than zero             | 0x08   | BGTZ     | BGTZ rs, offset    |

| Branch if less than zero                | 0x09   | BLTZ     | BLTZ rs, offset    |

| Branch if greater than or equal to zero | 0x0a   | BGEZ     | BGEZ rs, offset    |

| Branch on floating point compare false  | 0x0b   | BC1F     | BCIF offset        |

| Branch on floating point compare true   | 0x0c   | BCIT     | BC1T offset        |

|                                         |        |          |                    |

# Load / Store Instruction

| Instructions                                                      | Opcode | Mnemonic | Format                     |

|-------------------------------------------------------------------|--------|----------|----------------------------|

| Load byte signed, displaced addressing                            | 0x20   | LB       | LB rt, offset(rs) inc_dec  |

| Load byte signed, indexed addressing                              | 0xc0   | LB       | LB rt, (rs+rd) inc_dec     |

| Load byte unsigned, displaced addressing                          | 0x22   | LBU      | LBU rt, offset(rs) inc_dec |

| Load byte unsigned, indexed addressing                            | 0xc1   | LBU      | LBU rt, (rs+rd) inc_dec    |

| Load half signed, displaced addressing                            | 0x24   | LH       | LH rt, offset(rs) inc_dec  |

| Load half signed, indexed addressing                              | 0xc2   | TLH      | LH rt, (rs+rd) inc_dec     |

| Load half unsigned, displaced addressing                          | 0x26   |          | LHU rt, offset(rs) inc_dec |

| Load half unsigned, indexed addressing                            | 0xc3   | LHU      | LHU rt, (rs+rd) inc_dec    |

| Load word, displaced addressing                                   | 0x28   | LW       | LW rt, offset(rs) inc_dec  |

| Load word, indexed addressing                                     | 0xc4   | LW       | LW rt, (rs+rd) inc_dec     |

| Double load word, displaced addressing                            | 0x29   | DLW      | DLW rt, offset(rs) inc_dec |

| Double load word, indexed addressing                              | 0xce   | DLW      | DLW rt, (rs+rd) inc_dec    |

| Load word into floating point register file, displaced addressing | 0x2a   | L.S      | L.S ft, offset(rs) inc_dec |

| Load word into floating point register file, indexed              | 0xc5   | L.S      | L.S ft, (rs+rd) inc_dec    |

| addressing                                                        |        |          |                            |

| L.D L.D ft, offset(rs) inc_dec                                              | L.D L.D ft, (rs+rd) inc_dec                                               | LWL LWL offset(rs)                   | LWR LWR offset(rs)                    | SB SB rt, offset(rs) inc_dec     | SB I SB rt, (rs+rd) inc_dec    | SH SH rt, offset(rs) inc_dec     | SH Tt, (rs+rd) inc_dec         | SW   SW rt, offset(rs) inc_dec   | SW Tt, (rs+rd) inc_dec         | DSW DSW rt, offset(rs) inc_dec          | DSW DSW rt, (rs+rd) inc_dec           | DSZ DSW rt, offset(rs) inc_dec          | DSZ DSW rt, (rs+rd) inc_dec           | S.S S.S ft, offset(rs) inc_dec |                      | S.S S.S ft, (rs+rd) inc_dec                           | S.D ft. offset(rs) inc dec                           |                      | S.D B.D ft, (rs+rd) inc_dec                          |                    | SWL   SWL rt, offset(rs)              | SWR SWR rt, offset(rs)                 |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|---------------------------------------|----------------------------------|--------------------------------|----------------------------------|--------------------------------|----------------------------------|--------------------------------|-----------------------------------------|---------------------------------------|-----------------------------------------|---------------------------------------|--------------------------------|----------------------|-------------------------------------------------------|------------------------------------------------------|----------------------|------------------------------------------------------|--------------------|---------------------------------------|----------------------------------------|