# Feedback Control System Design for High Frequency Converter

by

Nurul Ilmi bt Khalid

# FINAL REPORT

Dissertation submitted in partial fulfilment of the requirements for the Bachelor of Engineering (Hons) (Electrical & Electronic Engineering)

# **JUNE 2008**

# Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2008 by Nurul Ilmi Khalid, 2008

### **CERTIFICATION OF APPROVAL**

# FEEDBACK CONTROL SYSTEM DESIGN FOR HIGH FREQUENCY CONVERTEE

by

Nurul Ilmi Khalid

A project dissertation submitted to the Electrical & Electronic Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved by,

(KHAIRUL NÍSAK MD HASSAN)

#### **UNIVERSITI TEKNOLOGI PETRONAS**

#### TRONOH, PERAK

June 2008

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

NURUL ILMI KHALID

# ABSTRACT

A new control scheme for a switch-mode power converter is proposed. A dynamic programming approach is applied to a buck converter switching regulator powering the load with abruptly varying load voltage and with abruptly powering changing load current. This approach can be applied to other switch-mode topologies. The voltage mode control is applied as it varies the duty cycle and essentially adjusts the input voltage drive to the buck LC components which directly affects output voltage. A closed-loop control system automatically maintains a precise output voltage regardless of varying input and load conditions. In simulation, the performance efficiency is slightly dropped by 4% but this feedback control system resulted in good regulation that holds a constant output under changing load condition. The gain of the feedback is limited to avoid instability. A maximum range of duty ratio gives advantages to widen the operation of DC-DC converter.

# ACKNOWLEDGEMENT

In the name of God, praise to Him the Almighty that in His will and given strength, I managed to complete my Final Year Project. This project would not have been possible without the support of many people. I would like to take this opportunity to thanks to my supervisor Miss Khairul Nisak Md. Hassan and greatest appreciation and gratitude to my co-supervisor Mr. Nor Zaihar Yahaya, for his guidance, and huge support through out the completion of this project.

Next, my appreciation goes to Final Year Project's committee member and all Electrical and Electronics Engineering Department staffs for extensive knowledge and insightful advice from them. Without the help from them, it is impossible for me to start and finish the work.

Particularly, I would like to express outstanding thanks to my colleagues, Fatimah Zaharah Hamidon and Fathiah Zakaria for sharing knowledge and ideas. I will embrace our friendship forever.

Finally, I would like to dedicate the thesis to my family for their love and support in these years. The great thanks go to my parents for their support and accompanying me from far during the time for preparing the thesis. With full cooperation from all above, I have successfully achieved the objectives of Final Year Project. Thank you.

# **TABLE OF CONTENTS**

|               |            | ·····                                               | v  |

|---------------|------------|-----------------------------------------------------|----|

|               |            | ſ                                                   | vi |

| LIST OF TABLE | 2 <b>S</b> |                                                     | ix |

|               |            | •••••••••••••••••••••••••••••••••••••••             | х  |

| LIST OF ABBRE | EVIATIC    | DNS                                                 | xi |

| CHAPTER 1:    | INTI       | RODUCTION                                           | 1  |

|               | 1.1        | Background of Study                                 | 1  |

|               | 1.2        | Problem Statement.                                  | 2  |

|               | 1.3        | Objectives and Scope of Study                       | 3  |

| CHAPTER 2:    | LITI       | ERATURE REVIEW                                      | 4  |

|               | 2.1        | History of Control System                           | 4  |

|               | 2.2        | Types of Feedback Control                           | 5  |

|               | 2.3        | Transfer function                                   | 6  |

|               |            | 2.3.1 Bode Plot.                                    | 7  |

|               |            | 2.3.2 Stability                                     | 9  |

|               | 2.4        | Voltage Mode Control                                | 10 |

|               |            | 2.4.1 Digital Linear Controller                     | 13 |

|               |            | 2.4.2 Non-linear Ideal Control                      | 14 |

|               | 2.5        | Analysis of an Optimal Controller                   | 15 |

|               | 2.6        | Feedback Controller in Spice-model                  | 17 |

|               |            | 2.6.1 Power Stage                                   | 18 |

|               |            | 2.6.2 Control loop- Error Amplifier                 | 18 |

|               |            | 2.6.3 Impact of Error Amplifier to Power Contr      |    |

|               |            | Design                                              | 18 |

|               |            | 2.6.4 Pulse-Width Modulator                         | 19 |

| CHAPTER 3:    | MET        | THODOLOGY                                           | 21 |

| CHARLENS.     | 3.1        | Project Work Flow.                                  |    |

| ۵             | 3.2        | Research                                            |    |

|               | 3.3        | Design Process                                      | 22 |

|               | 5,5        | 3.3.1 Power Stage                                   |    |

|               |            | 3.3.2 Compensator Network                           |    |

|               |            | 3.3.3 Pulse-Width Modulator Setting                 |    |

|               | 3.4        | Simulation by Pspice Software                       |    |

|               | 3.5        | Analysis and Discussion                             | 28 |

| CHAPTER 4:    | RES        | ULTS AND DISCUSSIONS                                | 29 |

|               | 4.1        | Effect of Feedback Control System at                |    |

|               |            | OutputVoltage, V <sub>out</sub>                     | 29 |

|               | 4.2        | Effect of Duty Ratio,D                              | 30 |

|               | 4.3        | Effect of performance efficiency, $\eta$ by varying |    |

|               | 1,42       | load                                                | 32 |

|               | 4.4        | Effect of gain, $k_d$ to the output voltage,        |    |

|               |            | Vout.                                               | 34 |

|               |            |                                                     |    |

|            | 4.5 | Effect of Capacitor value, $C_f$ to the output voltage ripple, $V_{ripple}$ | 38 |

|------------|-----|-----------------------------------------------------------------------------|----|

|            | 4.6 | Summary of Simulated Results                                                | 39 |

| CHAPTER 5: | CON | CLUSION AND RECOMMENDATIONS                                                 | 40 |

|            | 5.1 | Conclusion                                                                  | 40 |

|            | 5.2 | Recommendations                                                             | 40 |

| REFERENCES |     |                                                                             | 41 |

# LIST OF TABLES

| Table I: Parameters and values of power stage components          | 23 |

|-------------------------------------------------------------------|----|

| Table II: Maximum Ratings of Power MOSFET (N-channel) type IRF640 | 23 |

| Table III: Maximum Ratings of Precision Operational Amplifier     | 23 |

| Table IV: Parameters and values of PWM setting                    | 26 |

| Table V: Effect of duty ratio, D using feedback control system    | 30 |

| Table VI: Values of duty ratio, D from the simulation             | 31 |

| Table VII: Efficiency of the system performance                   | 33 |

| Table VIII: Output voltage when varying gain                      | 36 |

| Table XI: Summary of simulated results                            | 39 |

# **LIST OF FIGURES**

| Figure 1: Block diagram of transfer function                                             | 6  |

|------------------------------------------------------------------------------------------|----|

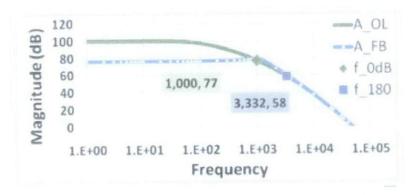

| Figure 2: Gain of feedback amplifier $A_{FB}$ in dB and corresponding open loop          |    |

| amplifier A <sub>OL</sub> . The gain margin in this amplifier is 19 dB [3]               | 8  |

| Figure 3: The phase of feedback amplifier with the phase margin is 45° [3]               | 8  |

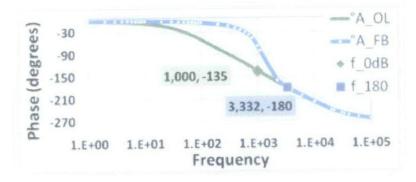

| Figure 4: Types of stability [4]                                                         | 10 |

| Figure 5: Buck Converter with Feedback Control System                                    | 10 |

| Figure 6: Block diagram for output voltage control of buck converter                     | 11 |

| Figure 7: Current waveform and error signal for high duty ratio                          | 12 |

| Figure 8: Typical Pulse Width Modulator                                                  | 12 |

| Figure 9: Control scheme: Combination of non-linear and linear digital control           | 13 |

| Figure 10: A buck switching regulator                                                    | 15 |

| Figure 11: Optimal controller- filter structure                                          | 16 |

| Figure 12: Simulated output voltage for step voltage change [5]                          | 17 |

| Figure 13: Pulse Width Modulator                                                         | 19 |

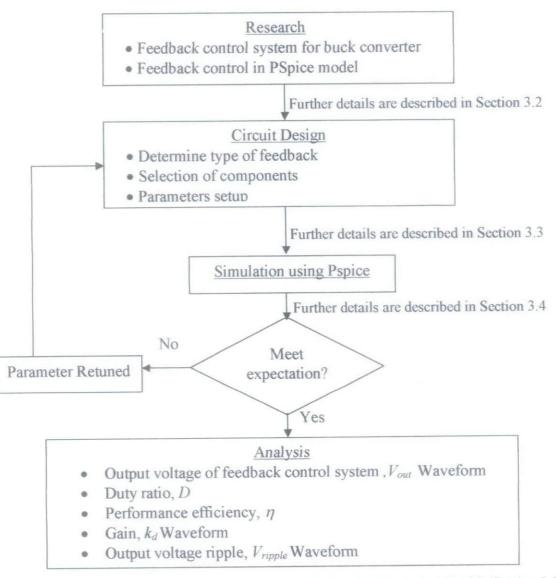

| Figure 14: Flowchart of project methodology                                              | 21 |

| Figure 15: Buck Converter with voltage mode control                                      | 22 |

| Figure 16: Compensator Network                                                           | 24 |

| Figure 17: PWM comparator                                                                | 25 |

| Figure 18: Sawtooth waveform from the simulation                                         | 25 |

| Figure 19: Analysis Setup Window                                                         | 27 |

| Figure 20: Transient Analysis                                                            | 27 |

| Figure 21: Part Browser Advanced                                                         | 28 |

| Figure 22: Graph V <sub>in</sub> vs V <sub>out</sub>                                     | 29 |

| Figure 23: $R= 87.5 \Omega$ , $P_{out} = 1.0290$ W and $P_{in} = 1.2447$ W               | 32 |

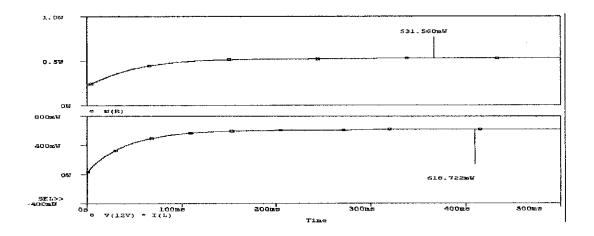

| Figure 24: $R = 175\Omega$ , $P_{out} = 531.56$ mW and $P_{in} = 618.722$ mW             | 32 |

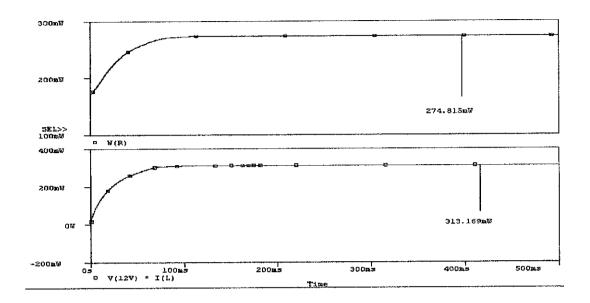

| Figure 25: $R = 350 \Omega P_{out} = 274.815 \text{ mWand } P_{in} = 313.169 \text{ mW}$ | 33 |

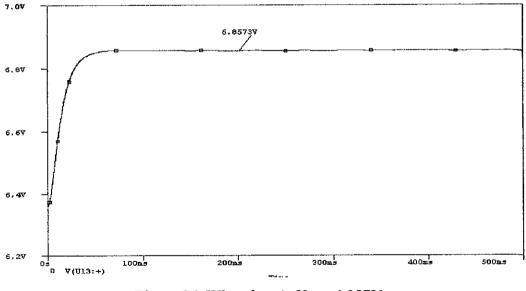

| Figure 26: When $k_d = 1$ , $V_{out} = 6.857$ V                                          | 34 |

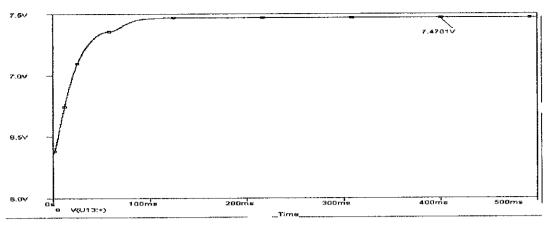

| Figure 27: When $k_d = 2$ , $V_{out} = 7.477 V_{out}$                                    | 35 |

| Figure 28: When $k_d = 3$ , $V_{out} = 8.6907$ V                    | 35 |

|---------------------------------------------------------------------|----|

| Figure 29: When $k_d = 4$ , $V_{out} = 9.643$ V                     | 36 |

| Figure 30: $k_d = 4$ , $C_f = 100$ Uf, $V_{ripple \ p-p} = 2.715$ V | 38 |

| Figure 31: $k_d = 4$ , $C_f = 1$ Uf, $V_{ripple p-p} = 0.1$ V       | 38 |

# LIST OF ABBREVIATIONS

PWM Pulse Width Modulator

.

MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor

# CHAPTER 1 INTRODUCTION

#### 1.1 Background of Study

In control theory, feedback is a process whereby some proportion of the output signal of a system is passed (fed back) to the input. This is often used to control the dynamic behavior of the system. Examples of feedback can be found in most complex system, such as engineering and biology. The processing and control of feedback is engineered into many electronic devices and may also be embedded in other technologies. Negative feedback is often deliberately introduced to increase the stability and accuracy of a system, as in the feedback amplifier. Feedback and regulation are self related. By varying the load, this will affect the output power of the system and the maximum duty ratio can widen the operational range of DC-DC converter. The negative feedback helps to maintain stability in a system in spite of external changes while the positive feedback is often amplifying and unstable where it will drive the system further away from its original setpoint. Faster output voltage stabilization is achieved as the gain increase, and output voltage ripple is shrinking by reducing the capacitor value. There are two ways in controlling the feedback control system. They are the voltage mode control where it is used to control varying load voltage and the current mode control is to vary the load current. The advantages of voltage mode control topology are that the control loop can be made relatively fast and there is no minimum ON-time required. It is used in fast applications such as powering high-end computer processors. The disadvantage of current mode control is the blanking time required to sense the current or else, it will cause the cycles to prematurely terminate.

#### 1.2 Problem of Statement

Varying the input voltage and load conditions will cause the output voltage to change and this cannot be used in real applications because there will be high power losses during delivery. Most converters produce an output dependent on the input, and do not provide inherent regulations that the duty ratio needs to be altered as needed. If the maximum duty ratio is small, the same output voltage cannot be generated even if the input voltage is decreased. At present, a dynamic programming approached has been applied to a buck converter switching regulator powering the abruptly varying load voltage which affects the performance of the output voltage. Output voltage ripple is one of the disadvantages in a switching power supply, and can be a measure of its quality. Output voltage ripple is the name given to the phenomenon where the output voltage rises during the ON-state and falls during the OFF-state. Several factors contribute to this, which include switching frequency, output capacitance, inductor, load and any current limiting features of the control circuitry.

This project will concentrate on how the feedback control system and how it is used to obtain the regulated output voltage by controlling the variation of the duty cycle of the switching. This feedback control system will also be able to control variable load where the duty cycle changes. An active control circuit will be needed to sense the input and adjust duty ratio accordingly.

# 1.3 Objectives

The objectives of this project are;

- 1. To study the basic understanding of feedback control system.

- 2. To study the effect of gain on stabilization of the system.

- 3. To study how the output capacitor,  $C_f$  affects the output voltage ripple.

- 4. To obtain the regulated output voltage by controlling the variation of duty cycle of the switching.

- 5. To obtain how much deviation of D cycles needs to be adjusted in response to the output load fluctuation data.

# CHAPTER 2

# LITERATURE REVIEW

#### 2.1 History of Control System

Feedback control systems are older than humanity. Numerous biological control systems were built into the earliest inhabitants of our planet. The Greeks began engineering feedback around 300 B.C. A water clock invented by Ktesibios operated by having water trickle into a measuring container at a constant rate. The water level in the measuring container could be used to tell time. For water to trickle at a constant rate, the supply tank had to be kept at a constant level. This was accomplished using a float valve similar to the water level control in today's flush toilets [1].

In 1745 speed control was applied to a windmill by Edmund Lee [1]. Increasing winds pitched the blades farther back, so that less area was available. As the wind decreased, more blade area was available. Modern developments have seen widespread use of the digital computer as part of control systems. For example, computers are in control systems used for industrial robots, spacecraft, and the process control industry.

A control system for a single-phase PWM converter composed of a plurality of power switching devices which converts an AC single-phase voltage to a DC voltage under PWM control. The control system includes a converter voltage reference operation unit for inputting a converter DC side voltage actual value, a converter DC side voltage reference value, a converter AC side current actual value, a power source voltage, and a sine wave power source voltage and for generating voltage references for respective phases, and a triangular wave generation unit for generating a triangular wave. The control system further includes a triangular wave

4

comparison unit for comparing the voltage references and the triangular wave to generate PWM signals for respective phases. Each of the PWM signals is applied to one of the power switching devices in the single-phase PWM converter to PWM control the single-phase PWM converter, respectively.

#### 2.2 Types of Feedback Control

Feedback is both a mechanism, process and signal that is looped back to control a system within itself. This loop is called the feedback loop. A control system usually has input and output to the system; when the output of the system is fed back into the system as part of its input, it is called the "feedback" Feedback and regulation are self related. The negative feedback helps to maintain stability in a system in spite of external changes. Positive feedback amplifies possibilities of divergences (evolution, change of goals where it gives the system the ability to access new points of equilibrium. A system in equilibrium in which there is positive feedback to any change in its current state is said to be in an unstable equilibrium, whereas it is possible for one with negative feedback to be in a stable equilibrium.

The end result of a positive feedback is often amplifying and explosive where a small perturbation results in big changes. This feedback, in turn, will drive the system further away from its original setpoint, thus amplifying the original perturbation signal, and eventually become explosive because the amplification often grows exponentially (with the first order positive feedback),

Both positive and negative feedback are closed systems, because the system is closed by a feedback loop. The response of the system depends on the feedback signal to complete its function; without such a loop, it would become an open system. In contrast, a feed-forward system is an open system since it does not have any feedback loop, and does not rely on feedback signal to function. Below are the three types of feedback:

- 1. negative feedback: which tends to reduce output (but in amplifiers, stabilizes and linearizes operation),

- 2. positive feedback: which tends to increase output, or

3. bipolar feedback: which can either increase or decrease output.

Bipolar feedback is present in many natural and human systems. Feedback is usually bipolar that is, positive and negative in natural environments, which, in their diversity, furnish synergic and antagonistic responses to the output of any system.

#### 2.3 Transfer function

A transfer function is the ratio of the output of a system to the input of a system, in the Laplace domain considering its initial conditions to be zero [2]. If we have an input function of X(s), and an output function Y(s), we define the transfer function H(s) to be:

$$H(s) = \frac{Y(s)}{X(s)}$$

(1)

Figure 1 below shows the block diagram of basic transfer function.

Figure 1: Block diagram of transfer function

The Transfer Function fully describes a control system. The Order, Type and Frequency response can all be taken from this specific function. Nyquist and Bode plots can be drawn from the open loop Transfer Function. These plots show the stability of the system when the loop is closed.

#### 2.3.1 Bode Plot

Bode plot is a graph of log magnitude versus frequency, plotted with a log-frequency axis, to show the transfer function or frequency response of a linear, time-invariant system. If the transfer function is a rational function with real poles and zeros, then the Bode plot can be approximated with straight lines. Bode plots are used to assess the stability of negative feedback amplifiers by finding the gain and phase margins of an amplifier. The notion of gain and phase margin is based upon the gain expression for a negative feedback amplifier given by

$$A_{FB} = \frac{A_{OL}}{1 + \beta A_{OL}}$$

(2)

where  $A_{FB}$  is the gain of the amplifier with feedback (the closed-loop gain),  $\beta$  is the feedback factor and  $A_{OL}$  is the gain without feedback (the open-loop gain). The gain  $A_{OL}$  is a complex function of frequency, with both magnitude and phase [3]. Bode plots are used to determine just how close an amplifier comes to satisfying this condition.

The Bode plotter is an electronic instrument resembling an oscilloscope, which produces a Bode diagram, or a graph, of a circuit's voltage gain or phase shift plotted against frequency in a feedback control system or a filter. It is extremely useful for analyzing and testing filters and the stability of feedback control systems, through the measurement of corner (cutoff) frequencies and gain and phase margins. This is identical to the function performed by a vector network analyzer, but the network analyzer is typically used at much higher frequencies. Figures 2 and 3illustrate the gain margin and phase margin for a different amount of feedback  $\beta$  where figure 2 shows the gain plot

Figure 2: Gain of feedback amplifier A<sub>FB</sub> in dB and corresponding open loop amplifier A<sub>OL</sub>. The gain margin in this amplifier is 19 dB [3].

Figure 3: The phase of feedback amplifier with the phase margin is 45° [3].

From there, the intersection of  $1 / \beta$  and  $A_{OL}$  occurs at  $f_{0dB} = 1$  kHz. Notice that the peak in the gain  $A_{FB}$  near  $f_{0dB}$  is almost gone. Figure 3 is the phase plot. Using the value of  $f_{0dB} = 1$  kHz found above from the magnitude plot of Figure 8, the open-loop phase at  $f_{0dB}$  is  $-135^{\circ}$ , which is a phase margin of  $45^{\circ}$  above  $-180^{\circ}$ . It should be noted that stability is not the sole criterion for amplifier response, and in many applications a more stringent demand than stability is good step response. As a rule of thumb, good step response requires a phase margin of at least  $45^{\circ}$ , and often a margin of over  $70^{\circ}$  is advocated, particularly where component variation due to manufacturing tolerances is an issue.

#### 2.3.2 Stability

Control analysis is concerned not only with the stability of a system but also the degree of stability of a system. A system is stable if every bounded input produces a bounded output. The stability of a system relates to its response to inputs or disturbances. A system which remains in a constant state unless affected by an external action and which returns to a constant state when the external action is removed can be considered to be stable.

Control analysis is concerned not only with the stability of a system but also the degree of stability of a system. A typical system equation without considering the concept of integral action is of the form.

$$a_2D^2 + a_1D + a_0 X = f(D)y....(3)$$

This is defined as be the highest order of D on the LHS as a equation of order 2.

The transient response, and as a result the stability, of such a system depends on the coefficients a  $_0$ , a  $_1$  and a  $_2$ . Assuming a  $_0 >0$  then provided that a  $_1 >0$  and a  $_2 >0$  the complementary function will not contain any positive time exponentials and the system will be stable. If either a  $_1 < 0$  (negative damping) or a  $_2 < 0$  (negative mass) the transient response will contain positive exponentials and the system will be unstable. If a  $_1 = 0$  (As resulting from zero damping) then the complementary function will oscillate indefinitely. This is not an unstable response but this marginally stable response is not satisfactory. Figure 4 shows a number of plots to illustrate the types of stability responses resulting from an input.

Figure 4: Types of stability [4]

## 2.4 Voltage Mode Control

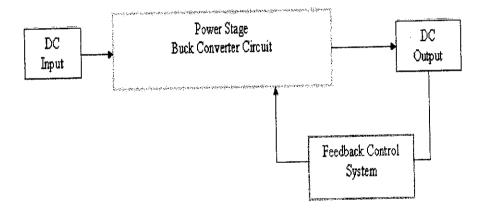

Figure 5: Buck Converter with Feedback Control System

Figure 5 shows a block diagram of buck converter with feedback control system. It consists of DC input, power stage, DC output and a feedback control system. Voltage mode control and current mode control are the two most popular switching power supply control strategies that make use of PWM. Varying the duty cycle essentially adjusts the input voltage drive to the converter components which

directly affects the output voltage ( $V_{out}$ ). The voltage mode control is used to control the voltage and automatically and so do the current. Current mode control is more complicated than this control strategy [5].

The block diagram suggests a stable system. In practice, however, the gain  $k_d$  must be limited. If not, stabilities will occur.

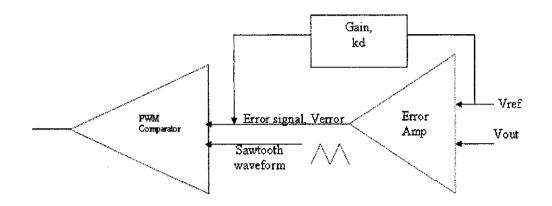

Figure 6: Block diagram for output voltage control of buck converter

Voltage mode-control is widely used. It is easy to implement where the error signal,  $V_{error}$  is equal to  $k_d(V_{ref} - V_{out})$  compared to a triangle or sawtooth waveform just as in PWM and  $k_d$  is the gain. The duty ratio is proportional to the error signal, and the converter control is complete. DC-DC converters act much like second-order systems. Besides, it is simple, work-well and has good immunity to disturbance at reference input,  $V_{ref}$ .

On the other hand, current-mode control has good operational properties within certain limits. An increase in  $V_{ref}$  will increase the duty ratio and raise the current. An increase in input source voltage will decrease the duty ratio without altering the output current. This makes voltage mode control easy to be implemented [6].

The only intriguing limitation of the PWM current-mode approach is a limit on the duty ratio. If D exceeds 50%, instability occurs.

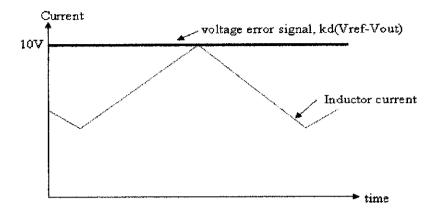

Figure 7: Current waveform and error signal for high duty ratio

The figure shows an inductor current, compared to a fixed output voltage error signal. The voltage, 10 V is high enough to command a duty ratio beyond 50%.

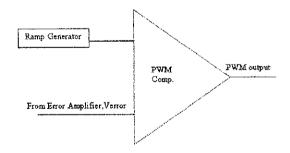

The output voltage from error amplifier is used as input voltage by the PWM. A simple ramp generator and a comparator is the actual circuit implementation of a voltage-mode control pulse-width modulator.

Figure 8: Typical Pulse Width Modulator

Figure 8 shows a typical pulse width modulator. The ramp waveform can be either of a sawtooth waveform or a triangle waveform. The two inputs of the PWM comparator are the ramp waveform and the error-amplifier output voltage. Since the PWM output contains a fixed frequency that drives the power stage, this frequency becomes the power supply switching frequency.

#### 2.4.1 Digital Linear Controller

In power converters, digital control has already been introduced. A lot of effort has been applied in search for better design where digital control is more advantageous than analog linear control. The need of a high switching frequency to achieve fast dynamic response is the drawback in analog linear control. To limit the inductor and output voltage ripple, a fast power stage design of converter is required. Increasing the effective bandwidth in a low frequency makes the ideal non-linear control combining with a digital linear loop is preferred over analog due to easy interaction with the non-linear control. In a high frequency converter, feedback of the output capacitor current is generally used.

The combination of the nonlinear and linear control needs to account for two issues. The non-linear action should lead the converter to a near steady-state situation with good accuracy. Otherwise, the transient response is still given by the slower linear loop. The other is the linear loop could interfere during the non-linear action leading to instabilities in the converter.

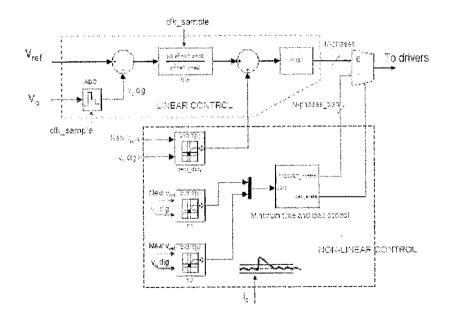

Figure 9: Control scheme: Combination of non-linear and linear digital control [6]

Refer to Figure 9 in previous page, shows the combination of non-linear and linear digital control. The linear action begins with both inductors current and output voltage values at steady state. This is necessary to avoid relying in the slower linear

loop to get the new steady state values. The duty cycle for the new steady state is different because it would lead to oscillations. By adding the nominal duty cycle to the output of the controller it would then solve the problems. The sampling frequency is selected as high as possible to maximize the bandwidth. In this case, the sample frequency is set to be equal to the switching frequency of the converter [6].

#### 2.4.2 Non-linear ideal control

The non-linear control is used to modify only few parameters on the linear loop, as the reference voltage or the duty-cycle, and its action is restricted to transients only [4]. Each time a voltage transition is required, the non-linear control performs the minimum time transition by passing the output of the PWM and controlling the switches of the phases. The fast control action under load steps is achieved by sensing the capacitor current. The three steps for non-linear control are the *transient detection, non-linear loop enabling*, and *non-linear loop reaction* [7].

The non-linear control loop identifies the transient beginning by detecting an instantaneous output voltage change and states if an increasing or decreasing load current is required by monitoring the converter output voltage. To optimize the non linear loop functioning, and to achieve fastest transient response, the transient time has to be detected as accurate as possible.

After all, the non-linear control performs by modifying the reference voltage in order to compensate the output voltage. The higher the gain  $k_d$ , the faster the output voltage stabilization. The gain should be as high as possible to improve the transient response but it should be as low as possible to avoid instabilities. An optimum  $k_d$  is needed.

#### 2.5 Analysis of an Optimal Controller

The response of the power converters to abruptly changes in load conditions has to be improved where it has generally resulted in complex and band-limited control arrangements. The controller would be quickly responsive to substantial changes in output voltage, and also provide precise steady-state control [8]. The control scheme can be translated into the voltage applied to the output filter of the power converter. It is either the input voltage or zero volts for a buck switching regulator, or is an easily derived voltage for other topologies.

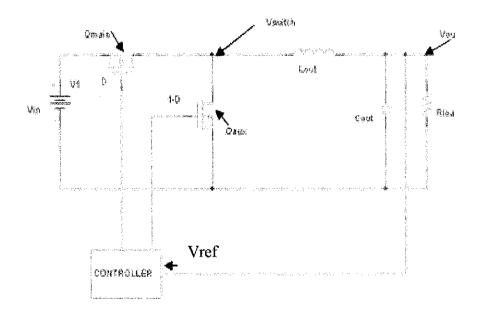

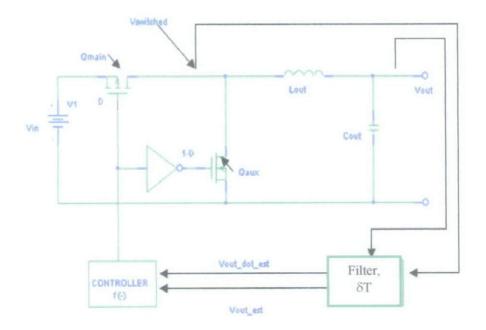

Figure 10: A buck switching regulator

A closed-loop controller for the buck regulator is illustrated in Figure 9 and preferably a filter is added to the circuit where it is used to estimate both power converters and avoid control system instability as the output voltage approaches the desired voltage level,  $V_{ref.}$

Figure 10 shows the optimal controller with embedded filter structure. The control structure can be modified to provide steady-state control or slowly varying endpoint voltage,  $V_{out}$ .

Figure 11: Optimal controller- filter structure

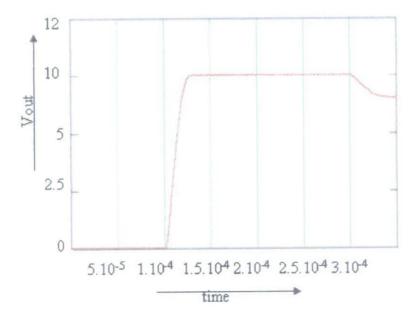

A functional delay,  $\delta T$  is introduced to produce steady-state limit cycle. For example to include a small delay factor  $\delta T$  such as 250 ns for a 250 kHz switching frequency, then the controller can provide steady-state operation limit cycle about a desired endpoint. Other than that, to provide a steady-state limit cycle at a desired endpoint can include other offsets such as a frequency-dependent filter, or simply delayed controller response can be included. Adjustable  $\delta T$  is used to provide corrective measure to the switching frequency for different operating conditions. The output voltage ( $V_{out}$ ) is modulated with an added signal such as triangular-wave function with a period equal to the desired steady-state switching frequency. This combination between time delay and the added signal can provide robust structure for controlling steady-state switching frequency. Figure 12 illustrates the result of simulation waveform of the circuit in Figure 11.

Figure 12: Simulated output voltage for step voltage change [8]

As indicate in the figure, the output voltage responds immediately and without overshoot to the desired voltage levels, following an essentially optimal trajectory to the desired endpoint voltages.

#### 2.6 Feedback Controller in SPICE-model

In designing DC-DC converter systems, there are two requirements to be satisfied: *steady state* and *dynamics*. The steady state requirements can be satisfied by properly choosing the parameters of the power stage. The dynamic requirements can be met by using an appropriate controller. In general, there are three types of SPICE-model developed for simulating DC-DC converters. They can be identified as *detailed model*, *large-signal averaged model*, and the *small-signal model*. All three models are useful in analysis and design of DC-DC converter systems [9].

#### 2.6.1 Power Stage

Three commonly used power stage topologies are buck, boost and buck-boost. Each of them has unique characteristics that make it desirable for particular applications. For example, the buck converter can only produce an output voltage that is lower than the input voltage while the boost converter produces an output voltage that is higher than its input [10]. The non-linear characteristics are results of the switching action of the power stage switching components. It was observed in reference [11] that the only nonlinear components in a power stage are switching device; the remainder of the circuit consists of linear elements.

#### 2.6.2 Control Loop – Error Amplifier

There are many aspects to the analysis and design of a switching power supply. A regulated switching power supply control loop consists of three major components: the *power stage*, the *reference voltage/error amplifier combination*, and the *pulse-width-modulator* [10]. The power stage performs basic voltage conversion. The reference voltage/error-amplifier circuit is designed so that a stable and fast-responding control loop is achieved. At this stage, it provides a signal which indicates the closeness of the output voltage to the desired value. Finally, the PWM converts analog output signal of the error-amplifier to a digital pulse train that is used by the power stage to produce the output voltage.

# 2.6.3 Impact of Error Amplifier Parameters to Controller Design

The commonly used feedback control loop includes the error amplifier, the main comparator which acts as a PWM modulator and the gate driver of power MOSFETs. In most cases, the error amplifier is used as a gain element in a compensator. Two assumptions are normally true. The signal transmitted by the amplifier is much greater than the signal fed forward by the feedback network, and the other one is that the signal fed back by the feedback network is much greater than the signal fed back through the amplifier [12]. The architecture of error amplifier used in the feedback loop suffers from an inherent load regulation performance limitation [13]. The limitation manifests itself through the limited DC open-loop gain, and results from limited closed-loop bandwidth. The frequency response of power supply loop is highly sensitive to the load conditions, thus, making proper compensation is a laborious effort. Small signal analysis is introduced to analyze the impact of error amplifier parameters. According to the model, the error amplifier consists of two stages. The input stage which carries input differential signal into current signal, and the gain stage.

# 2.6.4 Pulse-Width-Modulator

Pulse-width-modulator converts an analog input voltage to a repetitive train of logic level pulses that usually a fixed frequency whiles the width of the pulses is dependent on the analog input voltage. The logic level pulse train is generally referred to as the PWM output.

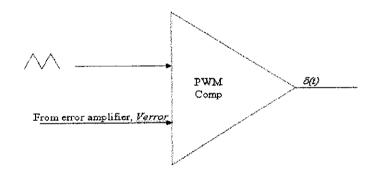

Figure 13: Pulse Width Modulator

The pulse-width-modulator is located after the error-amplifier. Figure 12 illustrate the PWM accepts the error-amplifier output voltage, as its input. The PWM output is a logic signal called  $\delta(t)$ . The actual circuit implementations of a voltage-mode control pulse-width modulator are the ramp generator and comparator. The ramp waveform can be either a sawtooth waveform or a triangle waveform. As the ramp waveform varies from its minimum level to maximum, the output of the PWM comparator switches from a high level to low level state, with the transition occurring when the two comparator input are equal. Since the PWM output is a fixed frequency that drives the power stage, this frequency becomes the power supply switching frequency. A control parameter is a value that provides a way to alter the output or the other desired variable. The conventional control parameters include phase and, as already mentioned, the duty ratio. In PWM inverter, the modulating function can be treated as the control parameter. By adjusting the duty ratio of the PWM to bring the output voltage ( $V_{out}$ ) equal to the reference voltage ( $V_{ref}$ ).

# **CHAPTER 3**

# METHODOLOGY

#### 3.1 Project work flow

Several procedures need to be done accordingly in order to implement the project. The methodology is simplified as shown in flow chart below (Figure 10).

Further details are described in Section 3.5

Figure 14: Flowchart of project methodology

#### 3.2 Research

Research has been done on feedback control system of buck converter to understand the basic operational. The controller section is studied at every block which is the error amplifier part and the PWM part. In order to understand the concept of simulation process, further research on how to use the software has been carried out.

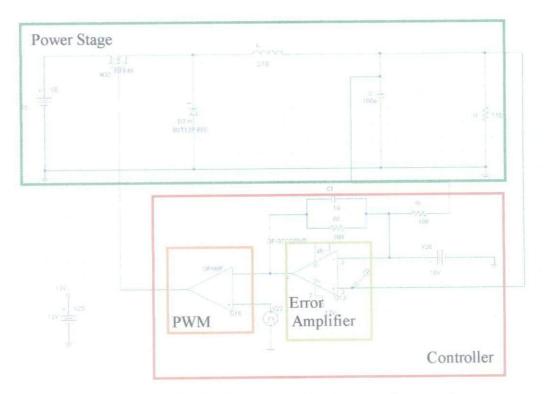

#### 3.3 Design Process

The buck converter with voltage mode control is shown in Figure 14. The converter is assumed to be in continuous conduction mode (CCM) of operation. The two requirements to be satisfied: the steady-state and dynamics. The parameters of the power stage have to be properly chosen in order to satisfy the steady-state requirements while the dynamic requirements can be met by using an appropriate controller. Choosing the correct parameter values of every component is important and for amplifier and power MOSFET value is chosen by referring to the data sheet.

Figure15: Buck Converter with voltage mode control

#### 3.3.1 Power Stage

In power stage topologies, a buck converter is used as a test circuit. It consists of five components which are  $V_{in}$ ,  $V_{out}$ , R, L, and C. The following parameters has been used in designing the power stage

| Parameters | Values |

|------------|--------|

| Vin        | 20 V   |

| Vout       | 10 V   |

| R          | 175 Ω  |

|            | 3.78 H |

| C          | 100 uF |

Table I: Parameters and values of power stage components

Both tables below shows the maximum ratings of power MOSFET and amplifier from datasheet provided. Table II provides the maximum ratings of power MOSFET type IRF640, and Table III is for amplifier maximum ratings.

Table II: Maximum Ratings of Power MOSFET (N-channel) type IRF640

| Parameters                         | Maximum |

|------------------------------------|---------|

| Continuous Drain Current, Vgs @10V | 18 A    |

| Pulse Drain Current                | 72 A    |

| Power Dissipation                  | 150 W   |

| Gate to Source Voltage             | ±20 V   |

Table III: Maximum Ratings of Precision Operational Amplifier

| Values                     |

|----------------------------|

| ±15 V                      |

| TYP: 1.6 nA MAX: 6 nA      |

| TYP : 11 V MAX 12.6 V      |

| <b>TYP : 4 W MAX : 8 W</b> |

|                            |

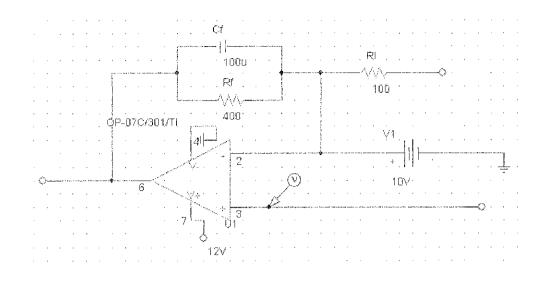

# 3.3.2 Compensator Network

Figure 16: Compensator Network

Figure 16 shows the controller part of the circuit. The peak value of the PWM is assumed to be 15V. The compensator network consists of  $R_{f}$ ,  $R_{i}$ , and  $C_{f}$ .  $\frac{R_{f}}{R_{i}}$  is the proposed feedback gain to keep the total load and line regulation under 1%.

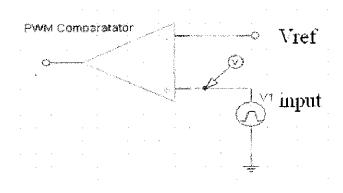

Figure 17: PWM comparator

Pulse width modulator (Figure 17) is determined to receive the sawtooth waveform at the input.

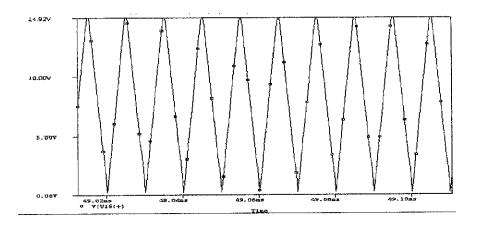

Figure 18 shows the sawtooth waveform of the PWM. The voltage peak to peak,  $V_{p-p}$  is 15V. The setting is set inside the  $V_{pulse}$  as on Table 4 follows:

Figure 18: Sawtooth waveform from the simulation

The setting of PWM is shown in Table IV below. It is applied inside the input,  $V_1$  as shown in Figure 17. This will produced a sawtooth waveform as shown in Figure 18 in the previous page.

| Values |

|--------|

| 0 V    |

| 15 V   |

| 0      |

| 4.9 us |

| 4.9 us |

| 0.5 us |

| 10 us  |

|        |

Table IV: Parameters and values of PWM setting

## 3.4 Simulation by Pspice software

.

The circuit is simulated using Pspice software. The basic setup for the analysis is by using transient setup. The challenges in designing the closed-loop control are important to give good performance without instability.

|                        | Enabled |                   | det. | <b>1129</b> |

|------------------------|---------|-------------------|------|-------------|

| AC Sweep               |         | Options           |      | Close       |

| Load Bias Point        |         | Parametric        |      |             |

| Save Bias Point        |         | Sensitivity       |      |             |

| DC Sweep.              |         | Temperature       |      |             |

| Monte Carlo/Worst Case |         | Transfer Function | ٦,   |             |

| Bias Point Detail      | T 🐔 🗍   | Transient         |      |             |

| Digital Setup          |         |                   |      |             |

Figure 19: Analysis Setup Window

|                     | and has the                                                                                                                                                                                                                        |                                    |                     |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|

| Transient Analysis  |                                                                                                                                                                                                                                    |                                    |                     |

| Print Step:         |                                                                                                                                                                                                                                    | luis                               |                     |

| Final Time:         | ļ                                                                                                                                                                                                                                  | 500ms                              |                     |

| No-Print Dela       | <b>h:</b>                                                                                                                                                                                                                          |                                    |                     |

| Step Cailing:       |                                                                                                                                                                                                                                    | aanaan dad a barar e waxiinda<br>J |                     |

| ) Detailed Bias     | Pt                                                                                                                                                                                                                                 |                                    |                     |

| i Skip initial trar | nsient solutio                                                                                                                                                                                                                     | n S                                |                     |

| Fourier Analysis    |                                                                                                                                                                                                                                    |                                    |                     |

| Enable F            | ourier                                                                                                                                                                                                                             |                                    | at an a first start |

| Center Frequ        | 그 같은 것이 같을                                                                                                                                                                                                                         |                                    |                     |

| Number of ha        | الاندانية المراجعة ا<br>مستحد مستحد مستحد مستحد مستحد مستحد مستحد المراجعة المراجعة المراجعة المراجعة المراجعة المراجعة المراجعة المراجع | · · · · ·                          | الله المحسب         |

| Output Vars.:       | di<br>Antara ang                                                                                                                                                                                                                   | ·                                  |                     |

| DK                  | <u> </u>                                                                                                                                                                                                                           | ncel                               |                     |

Figure 20: Transient Analysis

Figure 19 shows the analysis setup windows and transient is enabled. Then the transient analysis as shown in Figure 20 is set with the print step and final time, of  $1\mu s$  and 500ms respectively. To find the components inside Pspice, click "Get New Part" as shown in Figure 21 below.

| <b>L</b> A uA741 | Part     | Browser Advanced                                                                                                                                                                                                                                                                                                                                      |                                       | an da ing dina na katalan dan sa katalan da katalan katalan katalan katalan katalan katalan katalan katalan kat | ann naiseanna an ann an an an an an an an an an a                                                                              |

|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Get New Pa       | art Part | Name:                                                                                                                                                                                                                                                                                                                                                 |                                       | Description Search                                                                                              |                                                                                                                                |

|                  | inf      | and the second secon<br>Second second second<br>Second second |                                       | 1                                                                                                               |                                                                                                                                |

|                  |          | cription:                                                                                                                                                                                                                                                                                                                                             |                                       |                                                                                                                 |                                                                                                                                |

|                  | nc       | nannel mosfet - enhancei                                                                                                                                                                                                                                                                                                                              | m <b>ent</b>                          | Create New Part I                                                                                               | List                                                                                                                           |

|                  |          |                                                                                                                                                                                                                                                                                                                                                       |                                       | Sea                                                                                                             | rch                                                                                                                            |

|                  |          |                                                                                                                                                                                                                                                                                                                                                       |                                       |                                                                                                                 |                                                                                                                                |

| · · · ·          |          |                                                                                                                                                                                                                                                                                                                                                       | Libraty                               |                                                                                                                 |                                                                                                                                |

| · · ·            | IR3      | 741 👗                                                                                                                                                                                                                                                                                                                                                 | C:\Cadence\PSD_                       | 14.2\tools\PSpice                                                                                               | Close                                                                                                                          |

| D7m              |          | 084 0                                                                                                                                                                                                                                                                                                                                                 | -                                     |                                                                                                                 |                                                                                                                                |

| .8YT128-600      |          | 035<br>044                                                                                                                                                                                                                                                                                                                                            |                                       | 요즘 도신 전 생물                                                                                                      | Place                                                                                                                          |

|                  |          | 045                                                                                                                                                                                                                                                                                                                                                   |                                       |                                                                                                                 | Disco Classed                                                                                                                  |

|                  |          | 120<br>121                                                                                                                                                                                                                                                                                                                                            | M?                                    |                                                                                                                 | Place & Close                                                                                                                  |

|                  | IAF      | 122 🚊                                                                                                                                                                                                                                                                                                                                                 |                                       |                                                                                                                 | Help                                                                                                                           |

|                  |          | 123<br>130                                                                                                                                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · · |                                                                                                                 | المحت بمستحد فريسي يسرحهم                                                                                                      |

|                  | IRF      | 130/HA                                                                                                                                                                                                                                                                                                                                                | <u>े</u>                              |                                                                                                                 |                                                                                                                                |

|                  |          | 131<br>132                                                                                                                                                                                                                                                                                                                                            |                                       |                                                                                                                 | Libranes                                                                                                                       |

|                  | IRF      | 133                                                                                                                                                                                                                                                                                                                                                   |                                       | 134                                                                                                             |                                                                                                                                |

|                  |          | 140<br>141                                                                                                                                                                                                                                                                                                                                            | (), 11 %1 %<br>()<br>()               | 23≪21 L ⊴<br>}                                                                                                  | << Basic                                                                                                                       |

|                  |          | 142                                                                                                                                                                                                                                                                                                                                                   |                                       | <u></u>                                                                                                         |                                                                                                                                |

|                  |          |                                                                                                                                                                                                                                                                                                                                                       | Edit                                  | Symbol                                                                                                          | 가 같은 것을 가지.<br>1998년 - 동일에 가지 않는 것은 것을 가지 않는 것을 수 있는 것 |

|                  | Fi Fi    | ull List                                                                                                                                                                                                                                                                                                                                              |                                       |                                                                                                                 | 이는 이는 것을 받았다.<br>1999년 - 1993년 1월 1일                                                                                           |

Figure 21: Part Browser Advanced

Part Browser Advanced window will pop-up. From there, type part name such as IRF034 which is a power MOSFET and the component will be displayed. If it is the component needed, click "Place & Close" and the component will be placed on working window.

#### 3.5 Analysis and Discussion

Analysis and discussion are made with reference to the findings and observation during the simulations process. Several analysis based on the Pspice simulation will be evaluated in order to satisfy the objectives of this project.

# **CHAPTER 4**

## RESULTS

In this section will discuss about all findings from the simulations. The findings are discussed in separate sessions.

### 4.1 Effect of Feedback Control System at Output Voltage, Vout

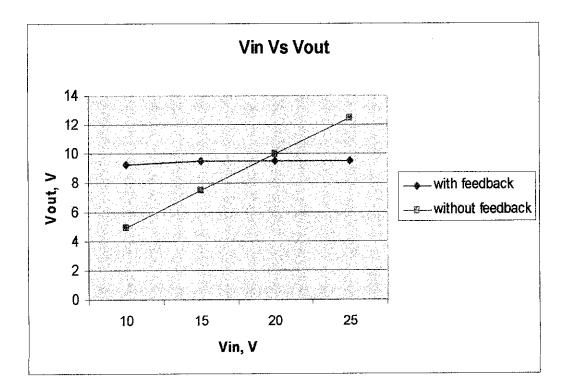

Figure 22: Graph Vin vs Vout

Figure 22 shows the differences between output voltage with feedback and without feedback control system at 100 kHz switching frequency. The output voltage of the converter without feedback control system increases proportional to the input voltage. The output voltage of the converter with feedback control system

is maintained within range of 9.1V, 9.5V, 9.6V and 9.8V. However, the feedback control system has produced a regulated output voltage around 10V.

From the results, it shows that using the feedback control system has produced the regulated output voltage under  $10V \pm 1\%$  tight regulation. As the input voltage increases to 35 V, the output voltage is still under line regulation as the duty cycle is automatically adjusted. From datasheet, the maximum input voltage for power MOSFET is 200 V while maximum current to turn on the amplifier is 6 nA. For this feedback control system, the current is 1.5 nA. It is still acceptable although the current is small. The value of resistor is very important as it will affect the gain which will cause instability. From the simulation, the higher value of capacitor,  $C_f$ will lead to current limitation into the amplifier and if smaller value is used, the current will abruptly change to several micro amperes. Theoretically, when *Ri* is smaller, the gain will increase. But there is limitation on the gain in order to stabilize the output voltage. For this circuit, the optimum value of *Ri* is 100 $\Omega$ .

| Input Voltage, Vin | Duty Ratio, D | Output Voltage, Vout |

|--------------------|---------------|----------------------|

| 20V                | 0.474         | 9.48V                |

| 25V                | 0.387         | 9.675V               |

| 30V                | 0.324         | 9.714V               |

| 35V                | 0.276         | 9.682V               |

| 40V                | 0.24          | 9.596V               |

| 45V                | 0.212         | 9.542V               |

#### 4.2 Effect of duty ratio, D

Table V: Effect of duty ratio, D using feedback control system

From the simulation, duty ratio is automatically being control by the feedback circuitry. Duty cycle ranging from 0.212 to 0.474 will produce regulated output voltage, *Vout*  $\pm 10V$ . Table V above summarizes the data taken from the simulation. By varying the value of the duty cycle, *D*, the feedback circuit can control the average output voltage to the desired level.

Theoretically, for Buck converter, voltage gain equation,  $D = \frac{V_{out}}{V_{in}}$ . It is proven by calculation below:

$$Vin(D) = Vout$$

.....(4)

| V <sub>in</sub> | D     | V <sub>out</sub> |

|-----------------|-------|------------------|

| 20 V            | 0.474 | 9.48 V           |

| 25 V            | 0.387 | 9.675 V          |

| 30 V            | 0.324 | 9.714 V          |

| 35 V            | 0.276 | 9.682 V          |

| 40 V            | 0.239 | 9.596 V          |

| 45 V            | 0.212 | 9.542 V          |

Table VI: Values of duty ratio, D from the simulation

As we know, theoretically to get the output voltage for Buck converter is given by equation (4) above. Results from simulation are verified using the equation and it is proven. For Buck converter without feedback, the duty ratio is 0.5 to produce output voltage of 10 V with input voltage 20 V. By using this feedback control system, it automatically controls the duty ratio and ranges them from 0.2 to 0.47. The result from the simulation is shown in Table VI. A maximum duty ratio is preferable since the set voltage range of the output voltage and the operational range of DC-DC converter can be widened. It shows that more energy can be converting from a single source rather than trying to distribute many different supplies. The highest output voltage generated is 9.715 V at input voltage of 30 V.

### 4.3 Effect of performance efficiency, $\eta$ by varying load

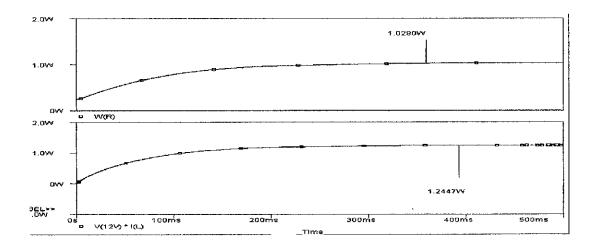

From simulation, input voltage,  $V_{in}$  is set to 20 V and the load is varied from 87.5  $\Omega$  to 350  $\Omega$  by factor of 2. The input and output power at different load are shown in Figure 19.

Figure 23:  $R= 87.5 \Omega$ ,  $P_{out} = 1.0290$  W and  $P_{in} = 1.2447$  W

Figure 23 illustrates the simulation result for  $P_{out}$  and  $P_{in}$  at load 87.5  $\Omega$ .  $P_{in}$  is greater than  $P_{out}$ .

Figure 24:  $R = 175\Omega$ ,  $P_{out} = 531.56$  mW and  $P_{in} = 618.722$  mW

The  $P_{in}$  and  $P_{out}$  shows in Figure 24 is produced at load 175  $\Omega$ . Both power is in *miliwatt* and it is smaller than both power at load 87.5  $\Omega$ .

Figure 25bexplains the power that is created at load 350  $\Omega$ . The  $P_{in}$  and  $P_{out}$  is decreasing as the load increase.

Figure 25:  $R = 350 \Omega$   $P_{out} = 274.815$  mW and  $P_{in} = 313.169$  mW

| Load (Ω) | Vout (V) | $P_{in}(\mathbf{W})$ | Pout (W)  | Efficiency,η(%) |

|----------|----------|----------------------|-----------|-----------------|

| 87.5     | 9.41     | 1.2447               | 1.029     | 82.6            |

| 175      | 9.48     | 618.72 m             | 531.56 m  | 85.9            |

| 350      | 9.81     | 313.169 m            | 274.815 m | 87.8            |

Table VII: Efficiency of the system performance

Table VII above shows the efficiency results from Buck converter with feedback control system. It shows that varying the load from 175  $\Omega$  to 350  $\Omega$ , will lead efficiency to drop by 2% while decreasing the value from 175  $\Omega$  to 87.5  $\Omega$  increase efficiency by 1.9%.

Theoretically, efficiency is

$$\eta(\mathbf{y}) = \frac{P_{out}}{P_{in}}$$

.....(5)

The relationship between load and output power is extended in order to see the effect on performance. From the simulation, the input and output power is illustrated by varying load values. It can be concluded that the efficiency is stable. The load with resistor 350  $\Omega$  is chosen because it has the highest efficiency of 87.8%. The power in the system increases as the load multiplies.

The equation (6) proves that when  $V_{out}$  is maintains, power output will increase as the load decrease.

## 4.4 Effect of gain, $k_d$ to the output voltage, $V_{out}$

To see the effect of gain to the output voltage, the gain value is varied from 1 to 4. Input voltage is set to be 20 V.

Figure 26: When  $k_d = 1$ ,  $V_{out} = 6.857$ V

Figure 26 shows that output voltage when gain is equals to 1. It can be observed that the output voltage is 6.8573V which is lower than the desired output voltage which is 10V.

Figure 27: When  $k_d = 2$ ,  $V_{out} = 7.477$  V

Figure 27 above illustrates the output voltage for gain equals to 2. The simulation result shows that the output voltage increases to 7.477V.

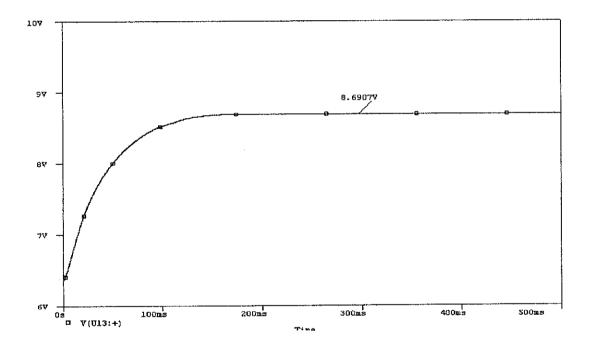

Figure 28: When  $k_d = 3$ ,  $V_{out} = 8.6907$ V

Figure 28 shoes the output voltage is 8.6907 V when gain is set to 3. It is getting higher and closed to the desired output voltage.

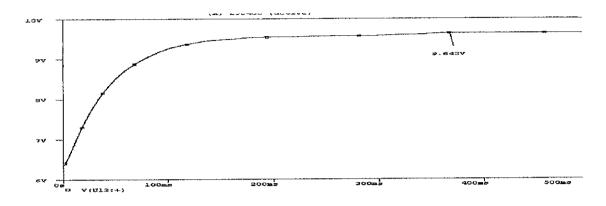

As the gain increases to 4 as shown in Figure 28, output voltage going up to 9.643V. The higher the gain, the longer transient time is needed during simulation.

Figure 29: When  $k_d = 4$ ,  $V_{out} = 9.643$  V

Table VIII below summarizes the output voltage,  $V_{out}$  with respect to increase in gain,  $k_d$ .

| Gain, k <sub>d</sub> | 1              | 2      | 3      | 4       |

|----------------------|----------------|--------|--------|---------|

| V <sub>in</sub>      | Vout           | Vout   | Vout   | Vout    |

| 30 V                 | 6.68 V         | 7.53 V | 8.78 V | 9.682 V |

| 25 V                 | 6.51 V         | 7.49 V | 8.72 V | 9.675 V |

| 20 V                 | 6.4 <b>8</b> V | 7.47 V | 8.69 V | 9.643 V |

Table VIII: Output voltage when varying gain

When gain is set to 1,  $V_{out}$  is ranging from 6.48 V to 6.68 V for input voltage of 20 V to 30 V respectively. While the gain is equal to 2,  $V_{out}$  is from 7.447 V to 7.53 V and  $V_{out}$  is nearly to  $\pm 10$ V as the gain is set to 4.

To verify the gain value, this equation is used,

$$Gain, k_d = \frac{R_f}{R_i}$$

(7)

Based on equation (7), as the gain increases the faster output voltage stabilization will be. From the simulation, it shows that longer transient time is needed. The gain in general must be limited to avoid instability and also to avoid driving control parameters to hard physical limits. Resistor value for  $R_i$  and  $R_f$  must be in the range between 100  $\Omega$  and 900  $\Omega$  to maintain input current to turn on the amplifier at 1.5 nA. If bigger value is employed, the circuit will not perform well and it will affect the input current used to turn on the amplifier. The input current will increase from 1.5 nA to 3  $\mu$ A. The maximum current to turn on the amplifier is 6 nA. Thus, the gain must be limited to 4 or else instability in performance will occur. It is proven that by increasing the gain value, the output stabilization will be faster and closed to desire  $V_{out}$  of 10 V.

# 4.5 Effect of Capacitor value, $C_f$ to the output voltage ripple, $V_{ripple}$

11.5XV 11.5XV 11.5XV 10.000V 9.000V 9.00V 9.0V 9.00V 9.00V 9.00V 9.0V 9.0V 9.0V 9.0V 9.0V 9

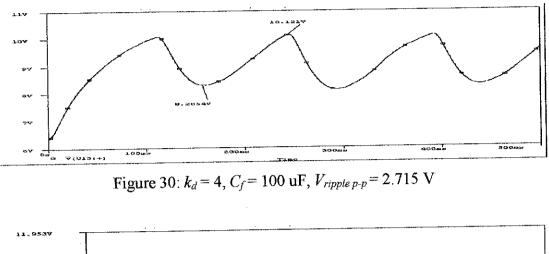

Figure 29shows voltage ripple waveform when capacitor value,  $C_f$  is set to 100 µF and  $V_{ripple p-p}$  is 2.715 V and Figure 30 shows the same voltage ripple waveform with different value of capacitor of 1 µF and  $V_{ripple p-p} = 0.1$ V. Voltage ripple peak-to-peak is obtained from equation

$$Vripple \qquad = \frac{Vripple}{Vripple} \qquad (8)$$

According to equation (8), ripple is affected by adjusting the capacitor value, Cf. The RC low-pass filter is used to stabilize the output. The compensation network is needed to increase the gain and speed up the transient response. As we increase the value of  $C_f$ ,  $V_{ripple}$  will increase from 0.1  $V_{p-p}$  to 2.715  $V_{p-p}$ . Here, the results are not acceptable and hence the ripples have to be further minimized. The best value of the capacitor to reduce the ripple is 1µH.

### 4.6 Summary of simulated results

| No. | Parameters                                                  | Improvement                                             |

|-----|-------------------------------------------------------------|---------------------------------------------------------|

| 1.  | Output voltage, Vout                                        | Regulated output 10V ±1%                                |

| 2.  | Duty ratio, D                                               | Automatically adjusted<br>(Ranging from 0.212 to 0.474) |

| 3.  | Output power, P <sub>out</sub><br>(Vin constant, vary load) | Efficiency decrease 4%                                  |

### Table XI: Summary of simulated results

From Table XI, it summarized the findings from the simulations. The output voltage,  $V_{out}$  is regulated as the duty ratio, D is adjusted automatically from 0.212 to 0.474. Although the efficiency is decreases by 4%, the feedback control circuitry still manage to produce a regulated output voltage. The gain and the output capacitor help to increase the voltage stabilization and reduce the voltage ripple.

# CHAPTER 5 CONCLUSION AND RECOMMENDATIONS

### 5.1 Conclusion

The closed-loop feedback control system automatically maintains a precise output voltage regardless of varying input and load conditions. It also adjusts the duty cycle to bring the output voltage ( $V_{out}$ ) equals to the reference voltage ( $V_{ref}$ ). The duty-ratio ranging from 0.212 to 0.474 give the advantages to widen the operation of DC-DC converter. More energy can be converted from a single source rather than trying to distribute to many different supplies. The gain of the feedback needs to be limited to avoid instability even though output voltage stability will be achieved faster as the gain increases. Based on the simulation results, this improved feedback control design will produce good regulation where the desire to hold a constant output under changing condition is achieved although the performance efficiency is decrease by 4%. An active control circuit will be needed to sense the input and adjust duty ratio accordingly. Output voltage ripple is reduced by minimizing the capacitor values.

## 5.2 Recommendations

There are few recommendations in order to improve the performance of the design in future time. With proper research especially on component selections as well as design evaluations can yield a very good performance for the feedback control system circuit. The recommendations suggested are as follows:-

5.2.1 Design the PWM that function for various frequencies

5.2.2 Give more attention on selection of components

5.2.3 Experimental approach is necessary to compare the simulated results with the experimental results.

40

## REFERENCES

- [1] Norman S. Nise, Control Systems Engineering, Wiley and son, 4<sup>th</sup> Edition, 2004

- [2] Wikipedia, Transfer Function, 2 June 2008"http://en.wikipedia.org/wiki/Transfer\_function"

- [3] Eric Cheever, Bode Plot,2005"http://www.facstaff.bucknell.edu/mastascu/elessonsHTML/Freq/Freq5.html"

- [4] Roy@roymech.co.uk, Stability, 17 February 2006"http://www.roymech.co.uk/Related/Control/Stability.html"

- [5] Rick, eCircuit Center, 2006"http://www.ecircuitcenter.com/Circuits/smps\_buck\_vm1"

- [6] A. Soto, P. Alou, J.A. Cobos," Non-Linear Digital Control Breaks Bandwidth Limitations", in *Applied Conference and Exposition 2006*, 21<sup>st</sup> *Annual IEEE*, pp 7, 19-23 March 2006

- [7] G.M Di Blasi, et al.,"A Novel linear-non-linear Digital Control for DC/DC Converter with Fast Transient Response", *IEEE Applied Power Electronics Conferences*, pp.493-498, Vol.1, March 19, 2006

- [8] Mark E. Jacobs, "Optimal Feedback Control of Switch-Mode Power Converters", in *Telecommunications Energy Conference*, 2006 INTELEC'06, Annual international IEEE, pp 1-10

- [9] N.D.Muhamad, M.R Rashid, A.H.M.Yatim, N.R.N. Idris and M.S. Ayob "Design of Power Stage and Controller for DC-DC Converter Systems Using Pspice," in PEDS IEEE, 2005