# Electrical Properties of High Voltage Rectifier Diodes Simulated Using Athena and Atlas

by

Muhammad Firdaus Bin Suid FINAL REPORT

Dissertation submitted in partial fulfilment of the requirements for the Bachelor of Engineering (Hons) (Electrical and Electronic Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

> > © Copyright 2011

by

Muhammad Firdaus Bin Suid, 2011

### CERTIFICATION OF APPROVAL

### Electrical Properties of High Voltage Rectifier Diodes Simulated Using Athena And Atlas

by

Muhammad Firdaus Bin Suid

A project dissertation submitted to the Electrical and Electronic Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the BACHELOR OF ENGINEERING (Hons) (ELECTRICAL AND ELECTRONIC ENGINEERING

Approved by,

(Dr. Zainal Ariff Burhanuddin)

# UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

### MAY 2011

### **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Freda

MUHAMMAD FIRDAUS BIN SUID

### ABSTRACT

As the title for this project, this final report for FYP 2 will include and conclude all the work and research that I have done regarding the Electrical properties of High Voltage Rectifier diodes simulated using Athena and Atlas. The objective of this project is to simulate the fabrication process of the High Voltage Rectifier based on the curve trace data gain during my internship in a semiconductor company. This report will summarize the work done on of the project. First chapter will give a brief description about the background of the project. There is also problem statement and some objectives included in this chapter. Second chapter will concentrate more on the study on the theory of High Voltage Rectifier diodes. Three important part of the High Voltage p-n junction will be discussed which is; the structure of a high voltage p-n junction, comparison between available structure and the electrical characteristics of each structure. The latest progress is on the research for the most suitable material for the high voltage diodes. In third chapter, there is a chart describing a methodology on how this project to be carried on. The chart has been followed to avoid any disturbance so that this project can be completed as planned.

### ACKNOWLEDGEMENT

Alhamdulillah is the best words that I can say for my grateful to Allah the Almighty god as for His mercy He gave me and the strength and ability to overcome the obstacle to complete this final year project throughout the year. I would like to take this opportunity to thank all parties involved both mentally and emotionally in helping me to be able to finish this Final year Project. Deepest gratitude goes to my parents, Suid Bin Salleh and Samsiah Binti Hassan for their continuous doa(pray), motivation, and nonstop moral support.

I would like to thank Dr. Zainal Ariff Burhanuddin for patience in guidance in helping me pursuing this project. I am very thankful to god as He has given me a chance to be working under the supervision of Dr. Zainal, for his guidance surely have help me during the times of needs.

I would like to thank everyone for their continuous support especially my colleagues and fellow friend for these elements have successfully assisted me to do my best and effort in upholding the learning spirit during my whole lifetime studying in UTP. Thank you once again and only Allah the God Almighty and The Most Merciful can repay all of your kindness.

### **TABLE OF CONTENTS**

| <b>CERTIFICATION</b> | OF API | PROVA   | L        | •         | •         | •        | •    | ii  |

|----------------------|--------|---------|----------|-----------|-----------|----------|------|-----|

| <b>CERTIFICATION</b> | OF OR  | IGINA   | LITY     | •         | •         | •        | •    | iii |

| ABSTRACT .           | •      | •       | •        | •         | •         | •        | •    | iv  |

| ACKNOWLEDGEN         | AENTS  |         | •        | •         | •         | •        | •    | v   |

| LIST OF TABLES       | •      | •       | •        | •         | •         |          | •    | ix  |

| LIST OF FIGURES      | •      | •       |          | •         | •         | •        |      | x   |

| CHAPTER 1:           | INTR   | ODUC'   | TION     | •         | •         | •        | •    | 1   |

|                      | 1.1    | Backg   | round o  | f Study   | •         | •        | •    | 1   |

|                      | 1.2    | Proble  | m State  | ment      | •         | •        | •    | 2   |

|                      | 1.3    | Object  | ives and | i Scope   | of Stud   | ly       | •    | 2   |

| CHAPTER 2:           | LITEI  | RATUF   | RE REV   | /IEW      | •         | •        | •    | 3   |

|                      | 2.1    | Review  | vs on D  | oping P   | rofile fo | or P-N   |      |     |

|                      |        | Junctio | on.      |           | •         |          |      | 4   |

|                      |        | 2.1.1   | Abrupt   | t Junctio | on        |          | •    | 4   |

|                      |        | 2.1.2   | Linear   | ly Grad   | ed Junc   | tion     | •    | 5   |

|                      | 2.2    | Unders  | standing | g The C   | urrent-V  | Voltage  |      |     |

|                      |        | Charac  | teristic | Of A P    | N-Junct   | ion      |      | 6   |

|                      | 2.3    | Junctio | on Breal | kdown     | •         |          |      | 7   |

|                      |        | 2.3.1   | Therm    | al Instal | oility    |          | •    | 7   |

|                      |        | 2.3.2   | Tunnel   | ling Efi  | fect      | •        |      | 8   |

|                      |        | 2.3.3   | Avalan   | che Mu    | ltiplica  | tion     | •    | 10  |

|                      | 2.4    | Compa   | rison b  | etween    | High V    | oltage F | ower |     |

|                      |        | Rectifi | er Struc | tures     |           |          | •    | 11  |

|                      |        | 2.4.1   | The str  | ucture o  | of a higl | h voltag | ;e   |     |

|                      |        |         | p-n jun  | ction.    | •         | •        | •    | 12  |

|                      | 2.5    | Device  | Structu  | ire and   | Operatio  | on       | •    | 12  |

|                      |        | 2.5.1   | P-i-N r  | ectifier  | •         | •        |      | 12  |

|                      |        | 2.5.2   | MPS re   | ectifier  | •         | •        | •    | 12  |

|                      |        | 2.3.3   | SSD re   | ctifier   |           | •        | •    | 13  |

|            | 2.6  | Blocking Characteristics 1               |          |           |           |          |            |    |  |

|------------|------|------------------------------------------|----------|-----------|-----------|----------|------------|----|--|

|            | 2.7  | Selecting the Most Suitable Material for |          |           |           |          |            |    |  |

|            |      | High `                                   | Voltage  | Diodes    | S         |          | •          | 15 |  |

|            |      | 2.7.1                                    | List o   | f Band    | Gaps      |          | •          | 16 |  |

|            |      | 2.7.2                                    | The F    | orward    | and Re    | verse    |            |    |  |

|            |      |                                          | Chara    | cteristi  | cs of Sil | icon C   | arbide     |    |  |

|            |      |                                          | Diode    | es at Hig | gh Temj   | peratur  | es.        | 17 |  |

| CHAPTER 3: | MET  | HODO                                     | LOGY     | •         | •         | •        | •          | 18 |  |

|            | 3.1  | Resea                                    | rch Me   | thodolo   | gy        | •        | •          | 18 |  |

|            | 3.2  | Metho                                    | odology  | •         | •         | •        | •          | 18 |  |

| CHAPTER 4: | RESU | JLTS A                                   | ND DI    | SCUSS     | SION      | •        | •          | 21 |  |

|            | 4.1  | Simul                                    | ation or | n PN Ju   | nction I  | Diode    |            |    |  |

|            |      | Struct                                   | ures.    |           |           | •        | •          | 21 |  |

|            |      | 4.1.1                                    | Basic    | PN Jun    | ction     | •        | ٠          | 21 |  |

|            |      | 4.1.2                                    | Simul    | ation of  | n MPS I   | Rectifie | er.        | 24 |  |

|            | 4.2  | Alpha                                    | -SiC Di  | iode D(   | C Forwa   | rd, Rev  | verse,     | 26 |  |

|            |      | and B                                    | reakdov  | wn Cha    | racterist | ics      |            |    |  |

|            |      | 4.2.1                                    | Silico   | n Carbi   | de Dioc   | le Stru  | cture.     | 26 |  |

|            |      | 4.2.2                                    | Forwa    | ard Volt  | tage Ch   | aracteri | istics.    | 28 |  |

|            |      | 4.2.3                                    | Break    | down V    | oltage    | Charac   | teristics. | 29 |  |

|            | 4.3  | Discu                                    | ssion    | •         | •         | •        |            | 31 |  |

|            |      | 4.3.1                                    | Effect   | of Dop    | oing Co   | ncentra  | tion       |    |  |

|            |      |                                          | to the   | I-V Cu    | rve.      | •        | •          | 31 |  |

|            |      | 4.3.2                                    | Effect   | Of Inc    | reasing   | The Ro   | egion      |    |  |

|            |      |                                          | Lengt    | h Of Tł   | ne P+ R   | egion I  | n MPS      |    |  |

|            |      |                                          | Rectif   |           | •         | •        | •          | 31 |  |

|            |      | 4.3.3                                    |          |           | ng Silic  | on Carl  | bide       |    |  |

|            | A    |                                          |          | Structu   | ıre.      | •        | •          | 32 |  |

| CHAPTER 5: |      | CLUSI                                    |          | •         | •         | •        | •          | 33 |  |

|            | 5.1  | Concl                                    |          | •         | •         | •        | •          | 33 |  |

|            | 5.2  | Kecon                                    | nmenda   | tion      | •         | •        | •          | 33 |  |

| REFERENCES | •    | •                                        | •        | •         | •         | •        | •          | 34 |  |

# LIST OF TABLES

| Table 1 | List Of Materials With Band Gap Value                 | •     | 16 |

|---------|-------------------------------------------------------|-------|----|

| Table 2 | Gantt chart for FYP 2                                 | •     | 19 |

| Table 3 | Comparison On The Effect Of Varying Schottky Region L | ength |    |

|         | To Its I-V Curve                                      | •     | 25 |

# LIST OF FIGURES

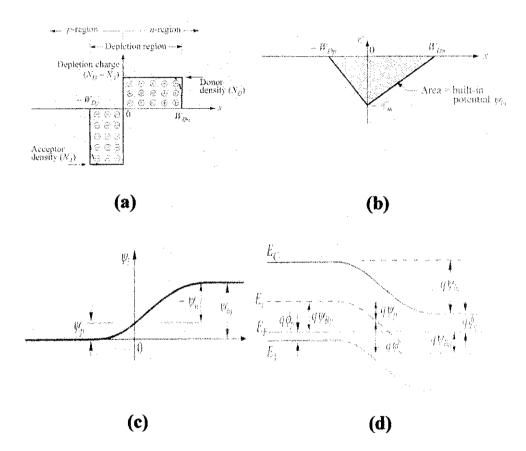

| Figure 1  | Abrupt junction in thermal equilibrium.                                     |                 |  |  |  |  |  |  |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|--|--|

|           | (a) Space-charge distribution,(b) Electric-field distribution.              |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | (c) Potential distribution where $\Psi_{bi}$ is the built-in potential.     |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | (d) Energy band diagram. I-V characteristics of a P-N junction              |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | diode                                                                       | 4               |  |  |  |  |  |  |  |  |  |  |  |

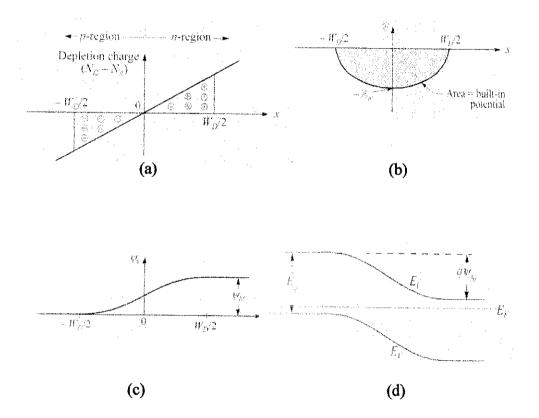

| Figure 2  | A linearly graded junction in thermal equilibrium.                          |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | (a) Space-charge distribution,(b) Electric-field distribution.              |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | (c) Potential distribution,(d) Energy band diagram                          | 5               |  |  |  |  |  |  |  |  |  |  |  |

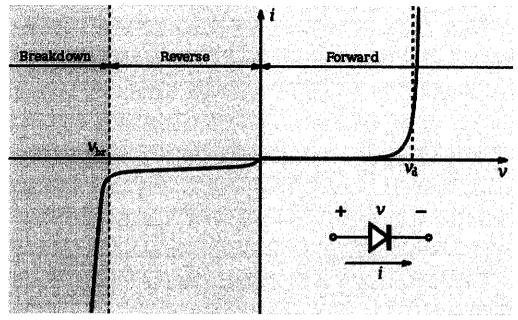

| Figure 3  | I-V characteristics of a P-N junction diode                                 | 6               |  |  |  |  |  |  |  |  |  |  |  |

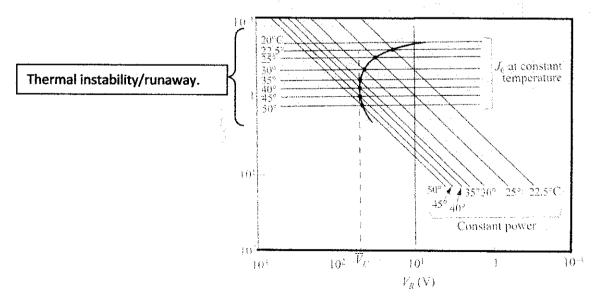

| Figure 4  | Reverse current-voltage characteristics of thermal breakdown.               | 7               |  |  |  |  |  |  |  |  |  |  |  |

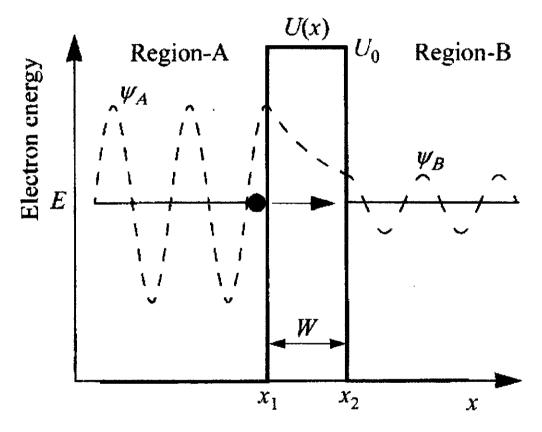

| Figure 5  | Wave functions showing electron tunneling through a rectangular             |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | barrier                                                                     | 8               |  |  |  |  |  |  |  |  |  |  |  |

| Figure 6  | Energy band diagrams during tunneling effect.                               | 9               |  |  |  |  |  |  |  |  |  |  |  |

| Figure 7  | Avalanche multiplication (initiated by hole current $I_{po}$ ).             | 10              |  |  |  |  |  |  |  |  |  |  |  |

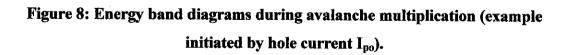

| Figure 8  | Energy band diagrams during avalanche multiplication (example               |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | initiated by hole current I <sub>po</sub> ).                                | 10              |  |  |  |  |  |  |  |  |  |  |  |

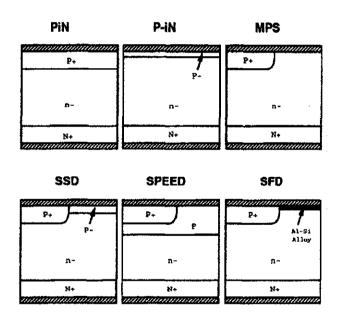

| Figure 9  | Figure showing the cross-sections of the different rectifier structure      | e11             |  |  |  |  |  |  |  |  |  |  |  |

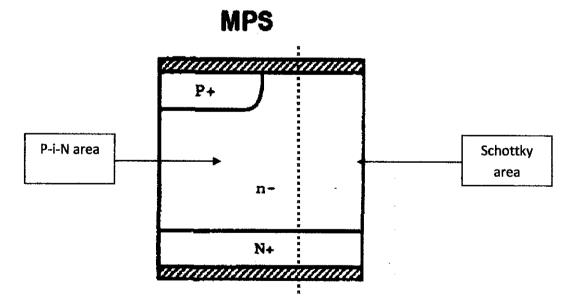

| Figure 10 | Figure showing the combination of Schottky and P-i-N.                       | 12              |  |  |  |  |  |  |  |  |  |  |  |

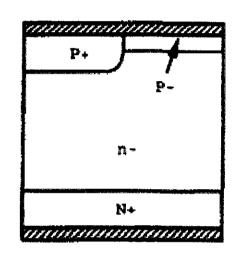

| Figure 11 | Figure showing the combination of lightly dope P- layer and PiN.            | 13              |  |  |  |  |  |  |  |  |  |  |  |

| Figure 12 | Reverse blocking characteristics for the rectifiers at $T = 100^{\circ}C$ . | 14              |  |  |  |  |  |  |  |  |  |  |  |

| Figure 13 | Graphical Representation For Band Gap                                       | 15              |  |  |  |  |  |  |  |  |  |  |  |

| Figure 14 | SILVACO Company Logo                                                        | 18              |  |  |  |  |  |  |  |  |  |  |  |

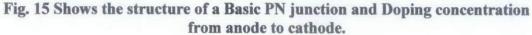

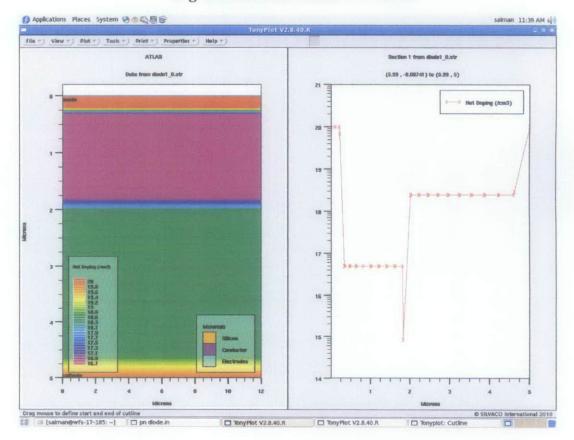

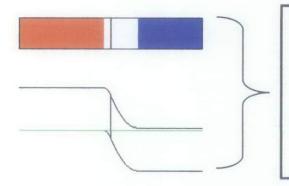

| Figure 15 | Shows the structure of a Basic PN junction and Doping concentrat            | ion             |  |  |  |  |  |  |  |  |  |  |  |

|           | from anode to cathode                                                       | 21              |  |  |  |  |  |  |  |  |  |  |  |

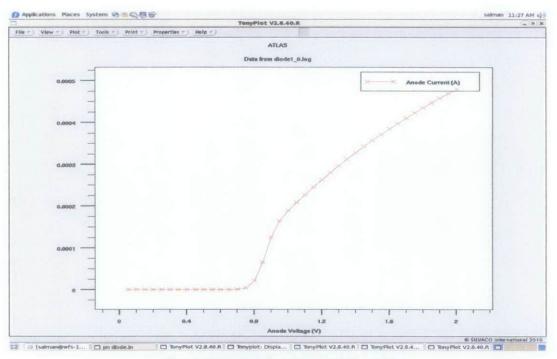

| Figure 16 | Shows the Anode I-V curves                                                  | 22              |  |  |  |  |  |  |  |  |  |  |  |

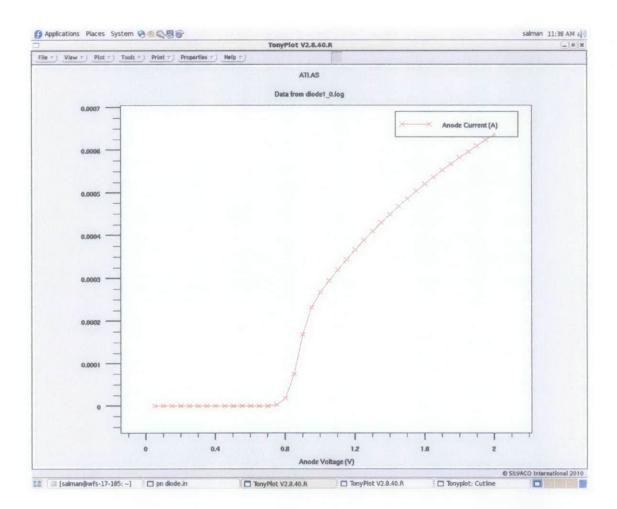

| Figure 17 | Shows the Effect of increasing the N doping concentration =                 |                 |  |  |  |  |  |  |  |  |  |  |  |

|           | 2.5e18atoms/cm <sup>3</sup>                                                 | <sup>.</sup> 22 |  |  |  |  |  |  |  |  |  |  |  |

| Figure 18 | Shows the Resulting I-V curves                                              | 23              |  |  |  |  |  |  |  |  |  |  |  |

| Figure 19 | Shows the MPS rectifier simulated using Silvaco Software                    | 24              |  |  |  |  |  |  |  |  |  |  |  |

| Figure 20 | Simulated Silicon Carbide Diode Structure                                   | 27              |  |  |  |  |  |  |  |  |  |  |  |

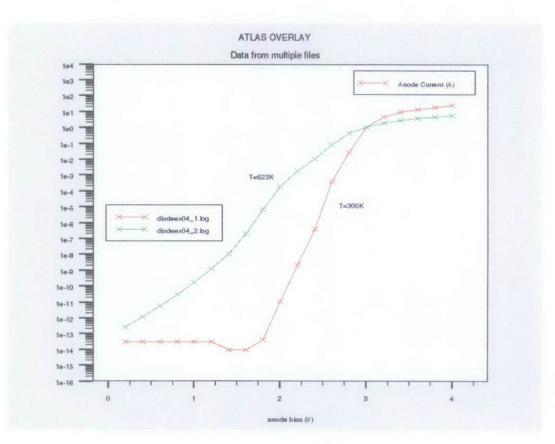

| Figure 21 | Forward Voltage Characteristics Between Two Different           |   |  |  |  |  |  |

|-----------|-----------------------------------------------------------------|---|--|--|--|--|--|

|           | Temperatures                                                    | 8 |  |  |  |  |  |

| Figure 22 | Breakdown Voltage Characteristics                               | 9 |  |  |  |  |  |

| Figure 23 | The Actual Breakdown Voltage Characteristics                    | 0 |  |  |  |  |  |

| Figure 24 | Fermi level Characteristics between normal PN junction and P-i- |   |  |  |  |  |  |

|           | N junction                                                      | 2 |  |  |  |  |  |

### **CHAPTER 1**

### INTRODUCTION

#### 1.1 Background

This FYP project will concentrate on simulating an electrical properties of a high voltage p-n junction that will achieved a breakdown voltage up to ~400V. A rectifier diode or PN junction diode was the first form of semiconductor device to be investigated in the early 1940s when the first real research was undertaken into semiconductor technology. Today, the PN junction has undergone a significant amount of development. Many varieties of diode are in use in a variety of applications. In addition to this, the PN junction forms the basis of much of today's semiconductor technology where it is used in transistors, FETs, and many types of integrated circuit [1]. The fundamentals of PN junction is found and used in many semiconductor devices today, diode, bipolar transistor, junction FET, Diac, Triac and many more.

There are many reasons why high voltage rectifier is needed such as for avalanche diode; where voltage transients are expected. Due to its high speed and ability to withstand large numbers of transients, avalanche diodes are used to protect circuits against surges, lightning and other transients. There are many types of high-voltage diodes, generally based on their construction [2].

### **1.2 Problem Statement**

Parameters that can cause high breakdown voltage for a p-n junction rectifier needs to be identify. Several paper have been reviewed on the p-n junction rectifier breakdown voltage such as by Manoj Mehrotra and B.J.Baliga[3], Y. C Kao[4] and several others will be as the reference for this project. By understanding its origin, simulation can be done to obtain high reverse breakdown voltage without destroying the diode.

### **1.3 Objectives**

Objectives of this project include:

- 1. To simulate the fabrication process and the high voltage p-n junction rectifier and to understand the electrical characteristic of it.

- 2. To understand the linearly graded doping profile as it is the reference for this project.

- 3. To understand the parameters that can affect high breakdown voltage of a p-n junction.

- 4. Understand the structure of a high voltage p-n junction that makes it possible for high voltage breakdown voltage up to ~400V.

- 5. Research on how to model those structures.

### CHAPTER 2

### LITERATURE REVIEW

A P-N junction is simply a junction of identical semiconductor but different doping. It is formed by doping donor atoms on one side (N-side) and doping acceptor atoms on the other (P-side). Doping agents can be introduced by diffusion at high temperature or by ion implantation.

Ion implantation has many advantages over diffusion and making it a much more popular process as compared to diffusion. Since P-N junction is the simplest of all semiconductor devices, having developed a method of extracting doping profile for P-N junctions, the same method could be easily extended to other more complicated devices like transistors.

Therefore, the device under test (DUT) chosen for this thesis is P-N junctions based on the curve trace of it has been obtain during my internship in a semiconductor company. It is essential to have a good knowledge of the P-N junction physics and its reaction under applied voltage bias. As a result, this section provides an in depth review of the electrical characteristics of different structure and with different material.

Work done by other engineers/scientist will be reviewed and will be discussed in this section. By understanding its concept, simulation can be done on it.

### 2.1 R eviews on Doping Profile for P-N Junction.

### 2.1.1 Abrupt Junction

Abrupt junction is a condition where the impurity concentration in a semiconductor changes abruptly from acceptor impurity  $N_A$  to donor impurities  $N_D$ , as shown in Fig 1. If  $N_A >> N_D$  (or vice versa), it will obtains a one-sided abrupt p<sup>+</sup>-n (or n<sup>+</sup>-p) junction.

Figure 1: Abrupt junction in thermal equilibrium. (a) Space-charge distribution. (b) Electric-field distribution. (c) Potential distribution where  $\Psi_{bi}$  is the builtin potential. (d) Energy band diagram.

#### 2.1.2 Linearly Graded Junction

In practical or in actual case, the doping profile cannot change abruptly from donor to acceptor side (vice versa), especially near the metallurgical junction where the two types meet and they compensate each other [5]. When the depletion widths terminate within this transition region, the doping profile can be approximated by a linear function.

Figure 2: Linearly graded junction in thermal equilibrium. (a) Space-charge distribution. (b) Electric-field distribution. (c) Potential distribution. (d) Energy band diagram.

### 2.2 Understanding the Current–Voltage Characteristic of a PN-Junction

Figure 3: I-V characteristics of a P-N junction diode

A simple p-n junction semiconductor diode's behaviour in a circuit is given by its current-voltage characteristic, or I–V graph (see Figure 3). The shape of the curve is determined by the transport of charge carriers through the depletion layer or depletion that exists at the p-n junction. When a p-n junction is first created, conduction band (mobile) electrons from the N-doped region diffuse into the P-doped region where there is a large population of holes (vacant places for electrons) with which the electrons "recombine". When a mobile electron recombines with a hole, both hole and electron vanish, leaving behind an immobile positively charged donor (dopant) on the N-side and negatively charged acceptor (dopant) on the P-side. The region around the p-n junction becomes depleted of charge carriers and thus behaves as an insulator [5].

### 2.3 Junction Breakdown

All p-n junction rectifiers cannot be biased with reverse voltage indefinitely. When sufficient high field is applied to a p-n junction, the junction will breaks down and conducts a very large current. According to the analysis done by S.M Sze [5], there are 3 causes that is responsible for breakdown voltage to occurs:

- 1. Thermal Instability.

- 2. Tunnelling Effect.

- 3. Avalanche Multiplication.

### 2.3.1 Thermal Instability

Thermal instability is responsible for the maximum dielectric strength in most insulators at room temperature. Heat dissipation caused by reverse current at high voltage caused the temperature of the junction to increase.

It will increase the reverse current in comparison with its value at lower voltages, thus caused breakdown. Because of the heat dissipation at high reverse voltage, the diode will be destroyed unless some special measure such as a large series-limiting resistor is used. Figure 4 shows the effect called thermal instability or thermal runaway. The thermal instability is important at room temperature, but at low temperatures it becomes less important compared with other mechanism.

Figure 4: Reverse current-voltage characteristics of thermal breakdown.

### 2.3.2 Tunnelling Effect

Tunnelling is a quantum mechanical phenomenon. In classical mechanics, carriers are completely confined by the potential walls. Only those carriers with excess energy higher than the barriers can escape.

In quantum mechanics, an electron can be represented by its wave function. The wave function does not terminate abruptly on a wall of finite potential height and it can penetrate into and through the barrier (figure 5). The probability of electron tunnelling through a barrier of finite height and width is thus not zero.

Figure 5: Wave functions showing electron tunnelling through a rectangular barrier.

When the junction is under a large reverse bias, the carrier can tunnel through a potential barrier as long as if the barrier is sufficiently thin is induced by a large field,  $\varepsilon$ . Figure 5 shows that particle (hole/electron) can flow through the barrier.

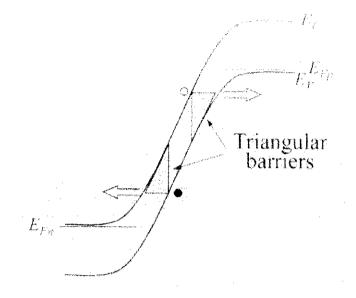

Figure 6: Energy band diagrams during tunnelling effect.

### 2.3.3 Avalanche Multiplication

For a junction breakdown voltage in excess of  $6E_g/q$ , the mechanism is caused by avalanche multiplication.

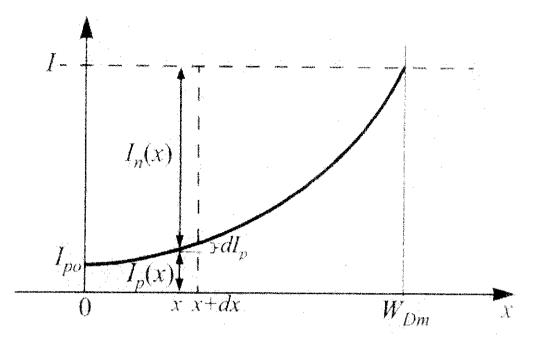

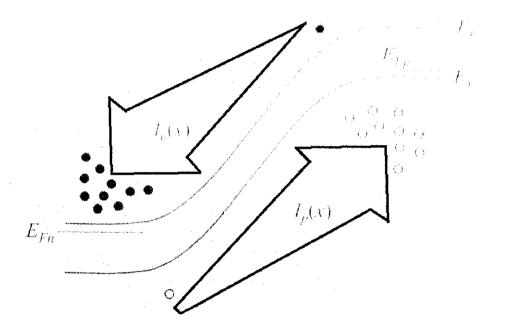

Avalanche multiplication, or impact ionization, is the most-important mechanism in junction breakdown. The avalanche breakdown voltage imposes an upper limit on the reverse bias for most diodes [5]. If the electric field in the depletion region is high enough that electron-hole pairs are generated by the impact ionization process, the hole current  $I_p$  will increase with the distance through the depletion region.

This incremental hole current is equal to the number of electron-hole pairs generated per second in the distance dx(figure 7).

Figure 7: Avalanche multiplication (initiated by hole current Ipo)

# 2.4 Comparison between High Voltage Power Rectifier Structures

### 2.4.1 The structure of a high voltage p-n junction.

In order to simulate the high voltage p-n junction, research has been done on its structure. Many high voltage power rectifier structures (P-i-N, SSD, MPS, SPEED, SFD) have been reported with improved reverse recovery characteristics. Research have been done by many researcher on comparing and analysis of these rectifiers performed by using identical drift region properties to obtain the forward I-V, reverse I-V, and reverse recovery characteristics by the researcher from NCSU(North Carolina State University)[7].

Fig. 9 Figure showing the cross-sections of the different Rectifier structures

Based upon this study, it is concluded that the trade-off between stored charge, leakage current, reverse recovery time and forward voltage drop is the best for the MPS (Merged P-i-N/Schottky) and SSD rectifiers [6].

### 2.5 Device Structure and Operation

#### 2.5.1 P-i-N rectifier

Fig. 6 shows the cross sections of the different rectifier structures considered in this study. For blocking voltage above 100 volts, the P-i-N rectifier has been the only commercially available rectifier [7]. The switching speed of this diode is limited by its long reverse recovery time due to the large amount of charge stored in the drift region. Methods to improve the switching speed of the P-i-N diode have been proposed using various lifetime control techniques to reduce minority carrier lifetime in the device drift region.

However, the reduction in lifetime for these devices results in an increase in forward voltage drop and reverse leakage current. In the P--i-N rectifier the stored charge is reduced by reducing the injection efficiency of the anode. However this device has a large V, at large current levels due to the poor conductivity of the drift region.

Fig. 10 Figure showing the combination of Schottky and P-i-N.

The MPS rectifier is based on merging a Schottky rectifier with the conventional P-i-N rectifier. The P-i-N region is used to inject minority carriers into the drift region and reduce the resistance in series with the Schottky region. As a consequence, the forward voltage drop for MPS rectifier remains low even at

a high current density. The introduction of the Schottky region also greatly reduces the stored charge in the drift region and results in a much faster switching speed.

# 2.5.3 SSD rectifier

SSD

### Fig. 11 Figure showing the combination of lightly dope P- layer and P-i-N.

The SSD rectifier has a shallow lightly doped P-layer surrounded by a highly doped P+ layer. The low injection efficiency of the P-layer results in a reduced stored charge.

The SFD rectifier is similar in concept to the SSD rectifier but the thin Player is formed by alloying the AI-Si electrode.

### 2.6 Blocking Characteristics

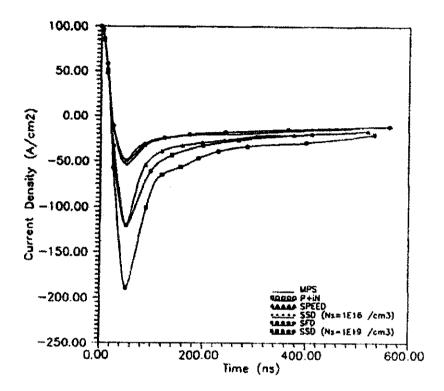

Fig. 12 Reverse blocking characteristics for the rectifiers at T= 100°C

The simulated reverse blocking characteristics of all the rectifiers are shown in Fig. 5 at 100°C and for a minority carrier lifetime of  $\mu$ s. The MPS and SSD rectifiers have larger leakage current when compared to the P<sup>+</sup>-i-N and SPEED rectifiers. The higher leakage current in the MPS rectifier arises from the reverse current flow at the Schottky region.

It can be reduced by increasing the barrier height. The high leakage current for the SSD rectifier arises from the depletion of the *P*- region allowing the depletion region to reach the ohmic contact, which has a very high surface generation rate. It can be seen that the MPS and SSD rectifiers have similar breakdown voltage to the P+-i-N rectifier due to the pinch-off of the depletion region under the P- or the Schottky region.

# 2.7 Selecting the Most Suitable Material for High Voltage Diodes.

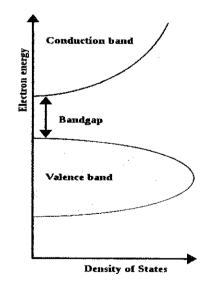

Band gap is an energy range in a solid where no electron states can exist. In graphs of the electronic band structure of solids, the band gap generally refers to the energy difference (in electron volts) between the top of the valence band and the bottom of the conduction band in insulators and semiconductors.

The conductivity of intrinsic semiconductors is strongly dependent on the band gap. The only available carriers for conduction are the electrons which have enough thermal energy to be excited across the band gap.

This is equivalent to the energy required to free an outer shell electron from its orbit about the nucleus to become a mobile charge carrier, able to move freely within the solid material.

So the band gap is a major factor determining the electrical conductivity of a solid. Substances with large band gaps are generally insulators, those with smaller band gaps are semiconductors, while conductors either have very small band gaps or none, because the valence and conduction bands overlap.

Fig. 13 Graphical Representation For Band Gap.

### 2.7.1 List of Band Gaps

Table 1 shows that there are several materials that can be used in fabricating diodes and each material have its own band gap value. Theoretically  $SiO_2$  (Silicon Dioxide) have the largest value of band gap energy, but the band gap is already considered as an insulator which is not suitable for a p-n junction rectifier a semiconductor.

| Material             | Symbol | Band Gap(eV) at<br>302K |              |

|----------------------|--------|-------------------------|--------------|

| Silicon              | Si     | 1.11                    | -            |

| Selenium             | Se     | 1.74                    | -            |

| Germanium            | Ge     | 0.67                    | -            |

| Silicon carbide      | SiC    | 2.86                    | Highest band |

| Aluminium phosphide  | AlP    | 2.45                    | gap value.   |

| Aluminium arsenide   | AlAs   | 2.16                    | _            |

| Aluminium antimonide | AlSb   | 1.6                     |              |

### Table 1: List Of Materials With Band Gap Value.

Based on the table 1, I choose Silicon Carbide (SiC) as the most suitable material for my diode as it requires more energy for carrier to flow from the top of the valence band to the bottom of the conduction band.

# 2.7.2 The Forward and Reverse Characteristics of Silicon Carbide Diodes at High Temperatures

Silicon carbide (SiC) is also known as *carborundum*, is a compound of silicon and carbon with chemical formula SiC. Silicon carbide powder has been mass-produced since 1893 for use as an abrasive. Electronic applications of silicon carbide as light emitting diodes and detectors in early radios were first demonstrated around 1907, and nowadays SiC is widely used in high-temperature/high-voltage semiconductor electronics [8].

The thermal and electronic properties of silicon carbide lead to very high semiconductor figures of merit for high-power, high-speed, high-temperature, high-frequency and radiation hard applications. This has caused growing interest in semiconductor devices based on SiC material systems. A recent review of the reasons for the interest in SiC technologies, and the increasing range of research and development activities in the area, was given in [9].

Based on the work done by P. Rabkin (Silvaco), R. Cottle (Silvaco), Professor M. Shur (University of Virginia), and P. Blakey (Silvaco), the DC characteristics at room temperature were simulated, and shown to be in good agreement with experimental data. Simulation was then used to estimate the high frequency characteristics of the device [10].

# **CHAPTER 3**

### **METHODOLOGY**

### 3.1 Research Methodology

- 1. Gather I-V curves or traces data provided by the semiconductor company.

- 2. Review papers on High Voltage power rectifier structures and comparison on it.

- 3. Review papers on different material used in building a rectifier and comparison on it.

- 4. Simulate the electrical characteristics of the design and material reviewed.

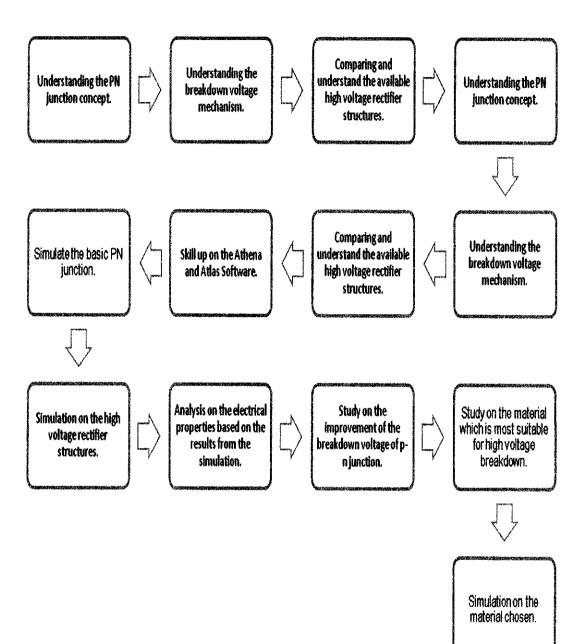

### 3.2 Methodology

ATHENA and ATLAS, a device simulation tool from SILVACO will be used in this project for defining the device by doing numerical simulation of the device. The first important step for this study is data gathering and research to acquire the theoretical knowledge of the fabrication process and a deep understanding on the breakdown mechanism of a rectifier.

Articles, journals and papers regarding p-n junction rectifier and its fabrication process will be referred to ensure the accuracy of collected data. The second step is developing the simulation by using Athena and Atlas software. The results of the simulation will be analysed and to be discussed further in the attempt to understand explain the electrical characteristic of each structure.

Fig. 14 SILVACO Company Logo.

Table 1 below is Gantt chart showing the timeline allocate by the author to complete the task. However the methodology it should differ because it should be an improvement on level of knowledge and technical skills on the project.

| Activities / Week                                 | 1 | 2 | 3 | 4 | 5 | 6          | Mid-               | 8 | 9 | 1 | 1<br>1 | 1 2 | 13 | 1 4 | 15 | 16 | 17 | 1 8 | 19 |

|---------------------------------------------------|---|---|---|---|---|------------|--------------------|---|---|---|--------|-----|----|-----|----|----|----|-----|----|

| Study on existence<br>project                     |   | - |   |   | - | •          | semes              | 0 | - | v |        |     | 5  | -   | 5  | U  | /  | 0   | ,  |

| Study on materials<br>needed and how its<br>work  |   |   |   |   |   | States and | fid-semester break |   |   |   |        |     |    |     |    |    |    |     |    |

| Preparation for<br>Progress Report                |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Submission of<br>Progress Report                  |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Further study on the design with second breakdown |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Simulation using<br>Silvaco Athena and<br>Atlas   |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Submission of Draft<br>Report                     |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Data collection (Data rate, operating time)       |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Study for improvement                             |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Data recording (Graph, table)                     |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Submission of Technical paper                     |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Submission of Final<br>Report                     |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Viva                                              |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Preparation for Oral presentation                 |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Oral presentation                                 |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

| Submission of Final<br>Report Hard Cover          |   |   |   |   |   |            |                    |   |   |   |        |     |    |     |    |    |    |     |    |

Table 2: Gantt chart for FYP 2

### 3.3 Flow Chart for FYP 2:

### CHAPTER 4 RESULT AND DISCUSSION

# 4.1 Simulation on PN Junction Diode Structures:

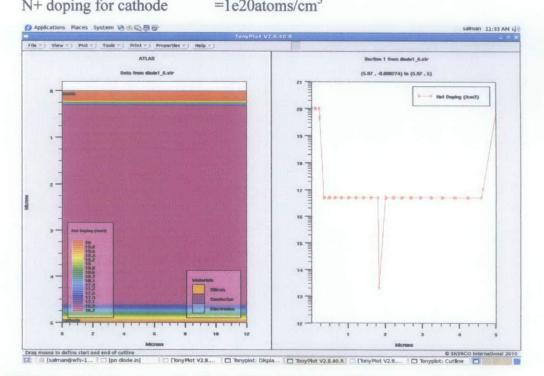

### **4.1.1 Basic PN Junction**

For the first part on the skill up on the Athena and Atlas software, I have simulated the basic PN- junction diode and to analyse the effect of doping concentration. See Appendix A for the programming code.

Parameter

2-D device simulation on a basic p-n junction rectifier:

| P-epi doping concentration | $=5e16atoms/cm^{3}$        |

|----------------------------|----------------------------|

| P+ doping for anode        | =1e20atoms/cm <sup>3</sup> |

| N+ doping                  | =1e17atoms/cm <sup>3</sup> |

| N+ doping for cathode      | =1e20atoms/cm <sup>3</sup> |

Fig. 16 Shows the Anode I-V curves

Fig. 17 Shows the Effect of increasing the N doping concentration =2.5e18atoms/cm<sup>3</sup>

Figure 18 Shows the Resulting I-V curves.

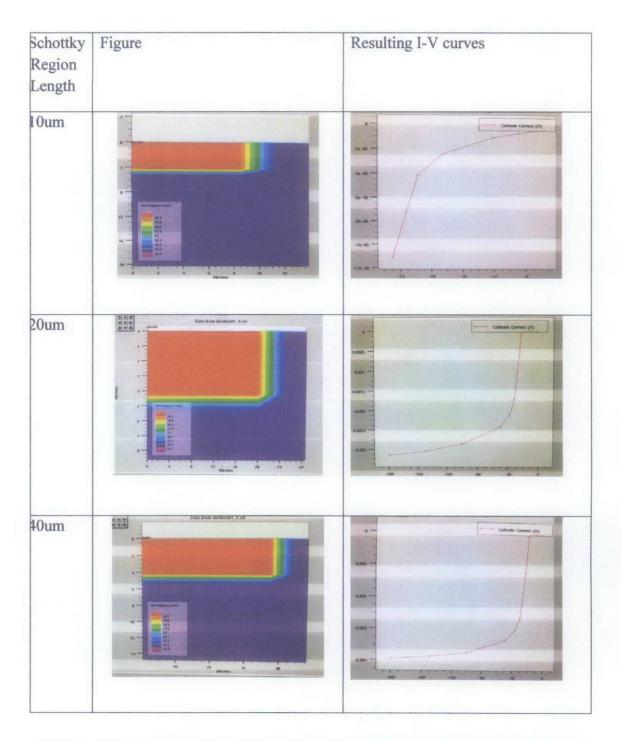

### 4.1.2 Simulation on MPS Rectifier:

MPS rectifier was simulated by varying the region length of the P+ region and the I-V curve of the reverse voltage was captured. The basic structure of MPS rectifier can be refered at Figure 3. The simulation was based on the work done by Shankar Sawant and BJ Baliga[6]

The coding use can be refer at Appendix B.

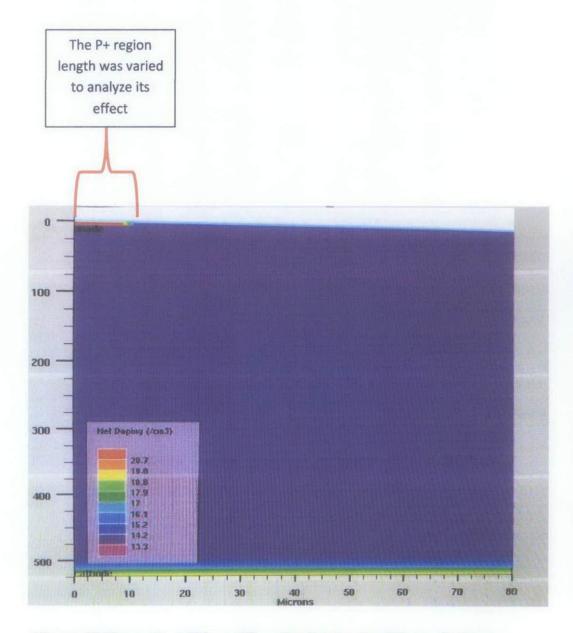

Figure 19 Shows the MPS rectifier simulated using Silvaco Software.

# 4.2 Alpha-SiC Diode DC Forward, Reverse, and Breakdown Characteristics

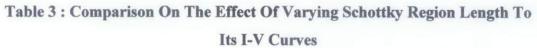

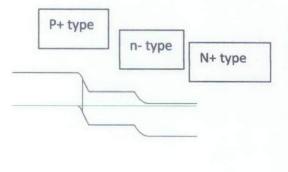

#### 4.2.1 Silicon Carbide Diode Structure.

The p+/n/n+ diode structure considered is a device based on one of the SiC polytypes called alpha-SiC (or 6H-SiC), and is constructed using ATLAS syntax. The input file consists of the following main parts:

- Mesh, regions, electrodes and doping specification using ATLAS syntax

- Material and models definition for SiC

- Calculation of forward I-V characteristic under the room temperature conditions

- Calculation of forward I-V characteristics under elevated temperature 623K

- Calculation of reverse and breakdown characteristics at 623K.

The simulations at elevated temperatures are performed in a separate ATLAS run within the same input file with the respective resetting/changing of the material and models definition.

The structure consists of 3 regions: p+, n, and n+emitter regions, each uniformly doped. The dimensions of the regions and their doping are defined in the region and doping statements respectively. The anode and cathode contacts are specified in the electrode statements.

Basic material parameters of alpha-SiC and temperature is also specified in the model statement.

The p-n-n<sup>+</sup>- diode structure simulated:

- 1. 1µm thick p-emitter doped at 2.0e19cm<sup>-3</sup>.

- 2. 6µm thick n-base region doped at 1.0e16cm<sup>-3</sup>.

- 3.  $330\mu m$  thick n+- emitter doped at  $5.0e18cm^{-3}$ .

- 4. The electron and hole capture times were assumed to be 10 ns. Because of the high energy band gap of about 3eV, and its comparatively strong temperature dependence, energy band gap narrowing due to the temperature and doping becomes very important, and must be accounted for properly.

Fig. 20 Simulated Silicon Carbide Diode Structure

# 4.2.2 Forward Voltage Characteristics.

The first run is completed by the solve statement in which the anode bias is stepped from 0.1 up to 4 V to calculate the diode forward characteristic under room temperature conditions. The I-V data is saved in the log file.

# 4.2.3 Breakdown Voltage Characteristics.

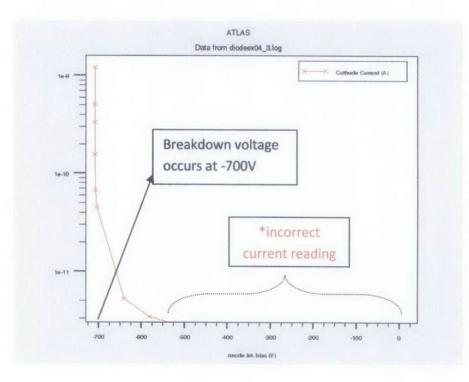

Simulation of the reverse characteristics and breakdown behavior of SiC devices is done at 300 K..Since cylindrical coordinates were used, Note that in all I-V plots the units of current is Amps and not Amps/micron.

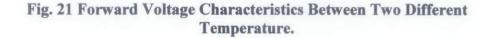

## Fig. 22 Breakdown Voltage Characteristics.

From figure 10, I manage to obtain breakdown voltage at -700V. But the accuracy of the graph is not acceptable as from 0 to -540V it shows that there is no current could flow.

Fig. 23 The Actual Breakdown Voltage Characteristics.

## 4.3 DISCUSSION

### 4.3.1 Effect of Doping Concentration to the I-V Curves.

Based on figure 7 and figure 9 we can see that by increasing the N+ doping concentration from 1e17atoms/cm<sup>3</sup> to 2e18 atoms/cm<sup>3</sup> the resulting current density for bias at anode (Vanode=2V) also increase 0.5mA to 0.65mA.

In general, an increase in doping concentration affords an increase in conductivity due to the higher concentration of carriers available for conduction.

# 4.3.2 Effect Of Increasing The Region Length Of The P+ Region In MPS Rectifier.

MPS rectifier have a larger reverse leakage current than the P-N device due to the Schottky area present in the MPS device structure. Under reverse bias conditions, depletion regions spread from the P+ in the MPS structure and intersect beneath the Schottky regions of the device. These depletion regions establish a potential barrier under the Schottky interface that reduces the rate of increase of electric field at the Schottky contact, with increasing reverse bias[7].

The high reverse blocking capability in these rectifiers with low leakage currents is obtained due to the formation of a potential barrier created by the merging of the depletion regions from the adjacent deep P+ diffusions[6].

## 4.3.3 Effect of Using Silicon Carbide Diode Structure.

From table 1, it is very clear that Silicon Carbide (SiC) has the highest band gap value which is 2.86 Band Gap (eV) at 302K. The higher the value of the band gap, will resulting in the higher amount of energy to move electron from covalence band to conductance band.That is why SiC diodes could achieve reverse breakdown up to -700.

#### **Basic PN junction** :

The red rectangle represents a p-type semiconductor and the blue rectangle an n-type semiconductor. The green horizontal line is the Fermi level.

The additional N- region doped in between abide and cathode caused additional energy needed to move electron from valence band to covalence band.

# Fig. 24 Fermi Level Characteristics Between Normal P-N Junction And P-I-N Junction.

# **CHAPTER 5**

# **CONCLUSION AND RECOMMENDATION**

This section will include the summarization of the whole project and also some recommendation to improve this project for the future.

# 5.1 CONCLUSION

The objective of this project is to simulate the fabrication process and the high voltage p-n junction rectifier and to understand the electrical characteristic of it. By understanding the different High voltage rectifier structures and its electrical properties a better structure can be propose to improve the breakdown voltage. Based on the work and research done on FYP 1, I have proved that the characteristics that can affect the performance and the breakdown voltage of the rectifier based on its structure are the doping concentration and its depth or thickness.

For this progress report of FYP 2, I have further my research on the material that will be well suited for high voltage which is Silicon Carbide (SiC). The simulation done have proved that SiC material can achieved breakdown voltage as high as -700V.

# 5.1 RECOMMENDATION

More research needs to be done on the possibility on the second breakdown occurrence. Based on the progress done, hope for the successful second breakdown simulation is bright.

## REFERENCES

- [1] [Online]. Available: http://www.electronicsradio.com/articles/electronic\_components/semiconductors/how-a-pnjunction-diode-works-basics-tutorial.php

- [2] [Online]. Available:

http://www.globalspec.com/LearnMore/Semiconductors/Discrete/Diodes/Hig

h Voltage Diodes

- [3] Manoj Mehrotra and B.J.Baliga North Carolina State University "Comparison of High Voltage Power Rectifier Structures"-

[Online]. Available: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=297080

[4] Y. c. KAO, MEMBER, IEEE

"High-Voltage Planar p-n Junctions"

IEEE, VOL. 55, NO. 8, AUGUST 1967

[5] S.M. Sze

"Physics of Semiconductor Devices"

3<sup>RD</sup> Edition 2007.

- [6] S.H.Larry Tu, and B.J. Baliga,

"Optimisation of the MPS rectifier via variation of Schottky region area," ISPSD ,PP. 109-112,1991.

- [7] Shankar Sawant and B.Jayant Baliga

"Comparative High Voltage (4kV) Power Rectifiers

PiN/MPS/SSD/SPEED"

Power Semiconductor Research Center, North Carolina State University

- [8] S.F. Gilmartin, A.F.J. Murray, W.A. Lane

"A looov Merged P-Nechottky (Mps) High-Speed Low-Loss Power

Rectifier" National Microelectronics Research Centre (NMRC), Ireland

- [9] http://en.wikipedia.org/wiki/Silicon\_carbide

- [10] R. Davis, G. Kelner, M. Shur, J. Palmour, and J. Edmond.

"Thin Film Deposition and Microelectronic and Optoelectronic Device Fabrication and Characterization in Monocrystalline Alpha and Beta Silicon Carbide,"

Proceedings of the IEEE, vol. 79, No.5, pp. 677-701, 1991.

- [11] P. Rabkin (Silvaco), R. Cottle (Silvaco), Professor M. Shur (University of Virginia), and P. Blakey (Silvaco)

"The Forward and Reverse Characteristics of Silicon Carbide Diodes at High Temperatures" go atlas

| # | Direction X                                                              |

|---|--------------------------------------------------------------------------|

|   | line x loc=0.00 spac=0.5                                                 |

|   | line x loc=3.00 spac=0.2                                                 |

|   | line x loc=5.00 spac=0.25                                                |

|   | line x loc=7.00 spac=0.25                                                |

|   | line x loc=9.00 spac=0.2                                                 |

|   | line x loc=12.00 spac=0.5                                                |

| # | Direction Y                                                              |

|   | line y loc=0.00 spac=0.1                                                 |

|   | line y loc=1 spac=0.2                                                    |

|   | line y loc=2 spac=0.2                                                    |

|   | line y loc=5 spac=0.4                                                    |

| # | Electrodes Contact Definition                                            |

|   | electrode name=anode x.min=0 length=12                                   |

|   | electrode name=cathode bot                                               |

|   | electrode name=anode workf=4.97                                          |

| # | P-epi Doping                                                             |

|   | Doping p.type conc=5e16 uniform                                          |

| # | P+ doping for anode                                                      |

|   | Doping p.type conc=1e20 x.min=0 x.max=12 y.top=0.0 y.bottom=0.25 uniform |

| # | N+ Doping(Nd)                                                            |

|   | Doping n.type conc=1e217 x.min=0 x.max=12 y.top=2 y.bottom=4.8 uniform   |

| # | P+ doping for anode                                                      |

|   | Doping p.type conc=1e20 x.min=0 x.max=12 y.top=0.0 y.bottom=0.25 uniform |

| # | Structure Saving                                                         |

|   | struct outfile=diode.str                                                 |

| # | Structure Plotting                                                       |

|   | tonyplot diode.str                                                       |

go atlas

mesh space.mult=1.0

| #                                                              | Direction X                                                               |                   |  |

|----------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|--|

|                                                                | line x loc=0.00 spac=0.1                                                  |                   |  |

|                                                                | line x loc=20.00 spac=5.0                                                 |                   |  |

|                                                                | line x loc=80.00 spac=10.0                                                |                   |  |

| #                                                              | Direction Y                                                               |                   |  |

|                                                                | line y loc=0.00 spac=0.1                                                  |                   |  |

|                                                                | line y loc=500.00 spac=100.0                                              |                   |  |

|                                                                | line y loc=525.00 spac=100.0                                              | The value for P+  |  |

| region n                                                       | um=1 silicon                                                              | length was varied |  |

| electr na                                                      | me=anode top                                                              | from 10um to 40um |  |

| electr name=cathode bot                                        |                                                                           |                   |  |

| electrode name=anode workf=4.97                                |                                                                           |                   |  |

| #                                                              | N-epi Doping                                                              |                   |  |

|                                                                | Doping n.type conc=2e13 uniform                                           |                   |  |

| #                                                              | P+ Doping                                                                 |                   |  |

|                                                                | Doping gaussian conc=5e20 p.type x.left=0 x.right=10 y.top=0.0 y.bottom=5 |                   |  |

| #                                                              | N+ Doping(Nd)                                                             |                   |  |

|                                                                | Doping n.type conc=5e19 x.min=0 x.max=80 y.top=520 y.bottom=252 uniform   |                   |  |

| saveoutf=diodeex01_0.str                                       |                                                                           |                   |  |

| tonyplot diodeex01_0.str -set diodeex01_0.set                  |                                                                           |                   |  |

| model conmob fldmob srh auger bgn                              |                                                                           |                   |  |

| contact name=anode workf=4.97 Forcing function                 |                                                                           |                   |  |

| solve init reverse voltage f                                   |                                                                           | e from            |  |

| logoutfile=diodeex01_log                                       |                                                                           |                   |  |

| solve vcathode=-50.00 vstep=-50.00 vfinal=-200.00 name=cathode |                                                                           |                   |  |

tonyplot diodeex01.log-set diodeex01\_log.set

۰.

```

go atlas

#

Title alpha-SiC Diode DC Forward, Reverse, and Breakdown Characteristics

# Section 1 : Mesh Input

#

Mesh rect

smooth=1

diag.flip cylindrical

I=0.0

x.m

spac=20

l=80.0

x.m

spac=10

|=200.0

x.m

spac≈50

#

# Section2 : Regions and Electrodes

#

Region num=1 material=a-SiC

y.max=3.2

Region num=2 material=a-SiC y.min=3.2

y.max=7.0

Region num=3 material=a-SiC y.min=7.0

#

Elec

name=anode x.max=100.0

Elec

name=cathode bottom

#

# Section 3: Doping Definition

#

# p+ emitter

Doping region=1

uniform conc=2.0e19

p.type

# n-base

Doping region=2

uniform conc=1.0e16

n.type

# n+ emitter

Doping region=3

uniform conc=5.0e18

n.type

#

Save outf=diodedaus.str master

#

# Section 4:

Material $ Models Definitions

#

Material

permittivity=9.66 ef300=3.00

egbeta=0.

Egalpha=3.3e-4

augn=2.8e31

augn=9.9e-32 vsat=2.0e7

tmun=2.25

tmup=2.25

lt.taun=2.3

lt.taup=2.3

Ħ

Material

num=1 mun0=35.0

mup0=25.0

taun0=1.e-9

taup0=1.e-9

Material

num=2 mun0=330.0

mup0=60.0

taun0=1.e-7

taup0=1.e-7

Material

mup0=35.0

num=3 mun0=120.0

taun0=5.e-9

taup0=5.e-9

#

Model fldmod srh auer bgn print temperature=300

Impact selb an1=1.66e6 an2=1.66e6

bn1=1.273e7

bn2=1.273e7

ap1=5.18e6

ap2=5.18e6

bp1=1.4e7

bp2=1.4e7

#

#

```

```

42

```

# Section 5: Forward Characteristic Room Temperature # Solve init Log outf=diodedaus.log Solve vanode=0.2 vstep=0.2 name-anode vfinal=4.0 Ħ Go atlas Ħ # Simulation At Elevated Temperature # Section 6: Read in Mesh and Structure Data Mesh inf=diodedaus.str cylindrical # Section 7: Set Material, Models Definitions & Temperature # Material permittivity=9.66 ef300=3.00 egbeta=0. Egalpha=3.3e-4 augn=2.8e31 augn=9.9e-32 vsat=2.0e7 tmun=2.25 tmup=2.25 lt.taun=2.3 lt.taup=2.3 # num=1 mun0=35.0 Material mup0=25.0 taun0=1.e-9 taup0=1.e-9 Material num=2 mun0=330.0 mup0=60.0 taun0=1.e-7 taup0=1.e-7 Material num=3 mun0=120.0 mup0=35.0 taun0=5.e-9 taup0=5.e-9 # Model fldmod srh auer bgn print temperature=623 Impact selb an1=1.66e6 an2=1.66e6 bn1=1.273e7 bn2=1.273e7 ap1=5.18e6 ap2=5.18e6 bp1=1.4e7 bp2=1.4e7 # Section 8: Forward I-V Characteristics 623K Ħ Solve init Logoutf=diodedaus.log Solve vanode=0.2 vstep=0.2 vfinal=4.0 name=anode # # Section 9: Calculate Reverse I-V Characteristics and Breakdown Ħ Method newrton dvmax=1e8 climit=1.e-5 Log off Solve init Log outf=diodedaus.log Curve trace end.val=1e-9 contr.name=anode curr.cont mincur=1e11 nextst.ratio=1.1 step.init=-0.5 Solve curve trace Save outf=diodedaus.str # Forward Characteristics at 300K and 623K Tonyplot –overlay diodedaus.log diodedaus.log -set iodedaus\_log1.set # Reverse and Breakdown Characteristics at 623K Tonyplot diodedaus.log -set diodedaus\_log2.set Quit