## DISSERTATION

"Bit-level non-destructive arbitration of CAN controllers"

By:

Kwong Lai Yeen (1473)

Dissertation submitted in partial fulfilment of the requirements for the Bachelor of Engineering (Hons) (Electrical and Electronics Engineering)

#### JUNE 2004

Universiti Teknologi PETRONAS Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

1. CAN controllers

2. Controller Area Network

3. EEE -- theris

## **CERTIFICATION OF APPROVAL**

## Bit-level non-destructive arbitration of CAN controllers

by

Kwong Lai Yeen

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved by

(Mr. Abu Bakar Sayuti) Project Supervisor

## UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

June 2004

## **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

YEEN KWC

## ABSTRACT

This report is written as part of the requirement of Final Year Project in progress. The title; "Bit-level non-destructive arbitration of CAN controllers" was selected by the author from a selection of titles provided by lecturers and approved by the Final Year Project (FYP) committee.

Chapter 1 of the report presented a brief overview on the project scope and concepts applied. It gave some introduction and a brief history on Controller Area Network (CAN). The problem statement which leads to the implementation of the project has also been highlighted. The objective of the project has also been defined in this section in which the main aim of this project is have an FPGA implementation of a CAN controller which will be able to demonstrate the non-destructive arbitration operation when sending messages across the bus. Chapter 2 of the report discussed more on CAN in general. It explained on the CAN protocol and the principle used in the network. CAN in general is divided into three layers which is the Object Layer, Physical Layer and Transfer Layer. Each layer has its corresponding tasks or functionality in data/message handling within the network. In network data transmission, CAN uses a method known as Carrier Sense, Multiple Access with Collision Detect (CSMA/CD) but with the enhanced capability of non-destructive bitwise arbitration to handle message collision to deliver maximum use of the available capacity of the bus.

In Chapter 3, the methodology used in implementing the project has been identified. The methodology schedule is based on the Gantt chart (Appendix A). The FPGA design flow used to program into the design into the FPGA chip has also been presented. In Chapter 4, some discussions and findings of CAN especially in the bit-level arbitration process of CAN has been discussed. The Register Transfer Level (RTL) simulation results and the Logic Analyzer captured output waveform has been analyzed and verified. The last section consists of the conclusion and some recommendations to improve on the design.

## ACKNOWLEÐGEMENT

This project would not have been possible without the help of a number of people, and the author would like to express her utmost gratitude to all of them.

The author would like to express her foremost gratitude to her supervisor, Mr. Abu Bakar Sayuti for his guidance and endless supports in the course of this project. Being under his supervision has been an irreplaceable experience; Mr. Abu Bakar has continuously monitored her progress and guided her throughout the duration of the project. His comments, critiques and suggestions were given serious consideration and were invaluable in determining the final outcome of the project.

Heartfelt gratitude also goes to Mr. David Kong, Mr. Ho Tatt Wei and Mr. Ng Kiat Hong, the author's fellow course mates who have been very helpful in providing basic tutelage in high-level programming to the author. Thank you very much for their support.

The author would also like to extend her sincerest thanks to Mr. Goh Teik Ming, the authors' good friend for providing valuable insights, ideas and assistance in one way or another throughout the duration of the project. His many useful comments and support has indeed helped the author in completing her project successfully. Also, the author would like to express her gratitude to the UTP Electrical and Electronics Lab technician especially Encik Musa bin Mohd Yusof for his valuable tips and assistance from time to time.

Last but not least, the author would also like to thanks her family for their continuous love and support, for which is a source of strength and motivation to the author. Finally, a very big thank you to everyone who has directly or indirectly assisted the author in different aspects throughout the development of her project. Without their constant guidance, supervision and encouragement, this project would not have been successfully completed. Thank you again for making this project a thorough learning experience for the author. Your kindness will be deeply appreciated.

# **TABLE OF CONTENTS**

| CERTIFICATION OF APPROVAL                                                                                         | i   |

|-------------------------------------------------------------------------------------------------------------------|-----|

| CERTIFICATION OF ORIGINALITY                                                                                      | ii  |

| ABSTRACT                                                                                                          | iii |

| ACKNOWLEDGEMENT                                                                                                   | iv  |

| TABLE OF CONTENTS                                                                                                 | V   |

| LIST OF ILLUSTRATIONS                                                                                             | vi  |

| LIST OF APPENDICES                                                                                                | vii |

| 1.0 INTRODUCTION                                                                                                  | 1   |

| <ul><li>1.1 Background of Study</li><li>1.2 Problem Statement</li><li>1.3 Objectives and Scope of Study</li></ul> | 3   |

| 2.0 LITERATURE REVIEW AND THEORY                                                                                  |     |

| <ul> <li>2.1 Basic CAN Principle</li></ul>                                                                        |     |

| 3.0 METHODOLOGY/PROJECT WORK                                                                                      | 14  |

| <ul> <li>3.1 Procedure Identification</li></ul>                                                                   |     |

| 4.0 RESULTS AND DISCUSSION                                                                                        | 26  |

| <ul> <li>4.1 Design Simulation Results</li></ul>                                                                  |     |

| 5.0 CONCLUSION                                                                                                    | 27  |

| <ul><li>5.1 Conclusion</li><li>5.2 Recommendations</li><li><b>REFERENCES</b></li></ul>                            |     |

| APPENDICES                                                                                                        |     |

| <u> </u>                                                                                                          |     |

# LIST OF ILLUSTRATIONS

| Figure 1.1  | : | ISO/OSI Reference Model                                          | 2  |

|-------------|---|------------------------------------------------------------------|----|

| Figure 2.1  | : | CAN Data Frame                                                   | 9  |

| Figure 2.2  | : | CAN Remote Frame                                                 | 9  |

| Figure 2.3  | : | An example of CAN arbitration process                            | 12 |

| Figure 3.1  | : | Project Flow Chart                                               | 15 |

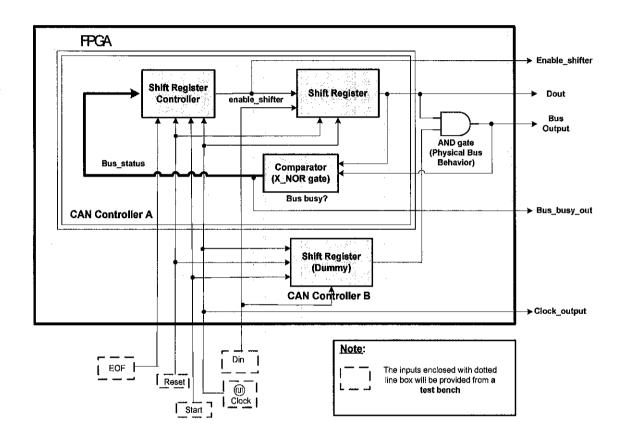

| Figure 3.2  | : | Functional Block Diagram for CAN controller                      | 17 |

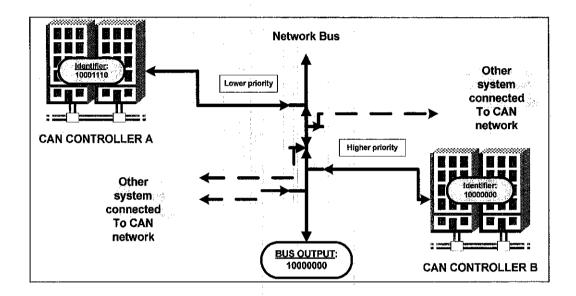

| Figure 3.3  | : | A CAN message handling system                                    | 18 |

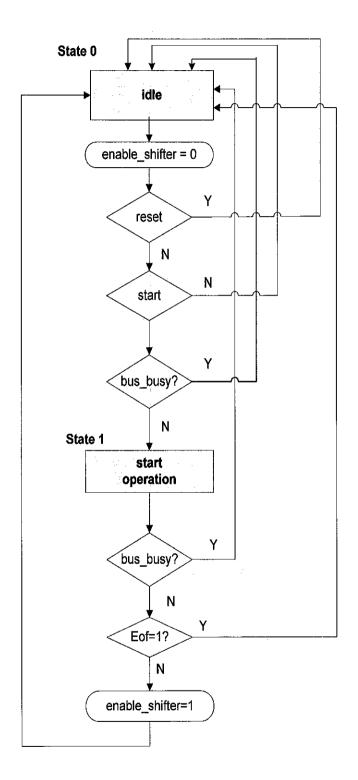

| Figure 3.4  | : | Finite State Machine Chart for Shift Register Controller         | 19 |

| T' 25       |   | Finite State Machine Chart for 8-bit Serial-in, Serial-out Shift | 20 |

| Figure 3.5  | : | Register                                                         | 20 |

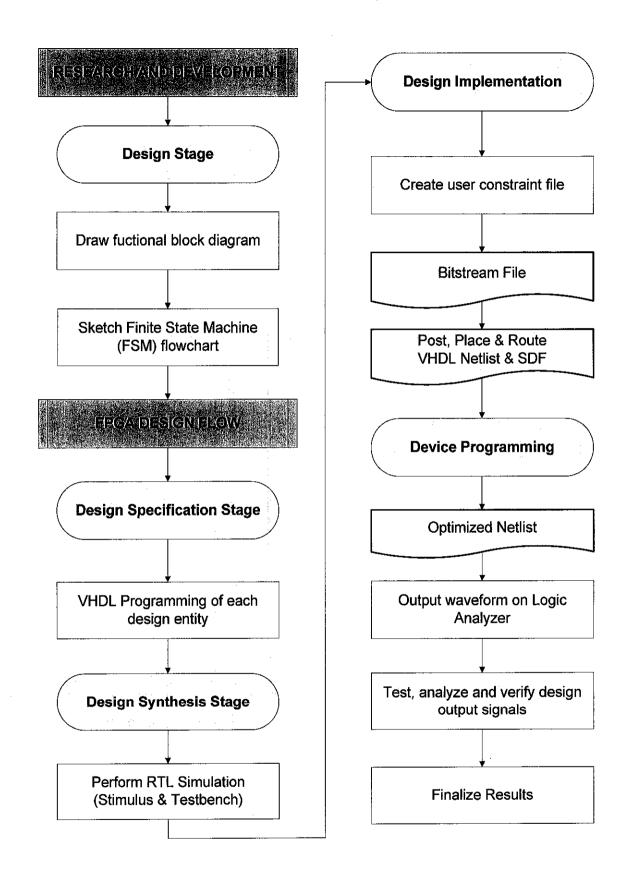

| Figure 3.6  | : | FPGA Design Flow                                                 | 21 |

| Figure 4.1  | : | RTL simulation using stimulus for XNOR gate                      | 27 |

| Figure 4.2  | : | RTL simulation using stimulus for 8-bit shift register           | 28 |

| Figure 4.3  | : | RTL simulation using stimulus for shift register controller      | 29 |

| Figure 4.4  | : | RTL simulation using stimulus for Top-level CAN controller       | 30 |

| Figure 4.5  | : | Test bench simulated output for XNOR gate                        | 32 |

| Figure 4.6  | : | Test bench simulated output for 8-bit shift register             | 32 |

| Figure 4.7  | : | Test bench simulated output for shift register controller        | 32 |

| Figure 4.8  | : | Test bench simulated output for Top-level CAN controller         | 33 |

| Figure 4.9  | : | Report of Top-level CAN controller simulation on window console. | 33 |

| Figure 4.10 | : | CAN top-level Logic Analyzer output waveform                     | 39 |

# LIST OF APPENDICES

| APPENDIX 1  | : | Project Gantt Chart                                       |

|-------------|---|-----------------------------------------------------------|

| APPENDIX 2  | : | VHDL Source Codes                                         |

| APPENDIX 3  | : | Block Diagram of Top-level CAN controller                 |

| APPENDIX 4  | ; | Test benches Source Codes                                 |

| APPENDIX 5  | : | Translation Report                                        |

| APPENDIX 6  | : | Map Report                                                |

| APPENDIX 7  | : | Place & Route Report                                      |

| APPENDIX 8  | : | FPGA Floorplan                                            |

| APPENDIX 9  | : | Pad Report                                                |

| APPENDIX 10 | : | Asynchronous Delay Report                                 |

| APPENDIX 11 | : | Post-Place & Route Static Timing Report                   |

| APPENDIX 12 | : | BitGen Report                                             |

| APPENDIX 13 | : | User Constraint File                                      |

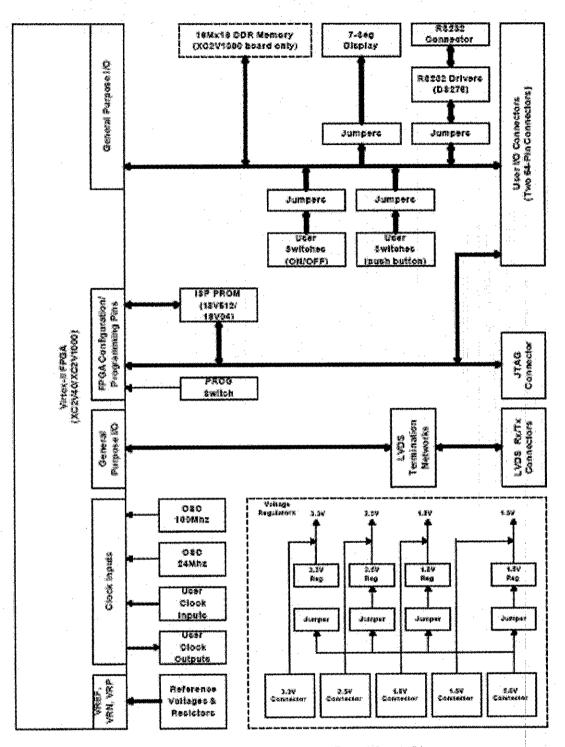

| APPENDIX 14 | : | Layout and caption of Virtex II Xilinx XC2V100 Demo Board |

## CHAPTER 1

## **INTRODUCTION**

This section provides some insights on the topic of interest, Controller Area Network (CAN). In addition, the problem statement of the project has also being defined. Besides, the objectives of the project and the scope of study have also being provided in this section.

#### **1.1 BACKGROUND OF STUDY**

#### 1.1.1 Brief History of CAN

Controller Area Network (CAN) which was developed in the year 1986 was the brainchild of Robert Bosch, a German automotive system supplier. It was initially developed for automotive industry applications to ensure a more robust serial communications for networking in vehicles. CAN is a technology designed for automobiles to be more reliable, safe and efficient while decreasing wiring harness weight and complexity within the interior of vehicle electronics. With the use of CAN, point-to-point wiring in vehicle wiring systems is gradually being replaced by one serial bus connecting all control systems. Besides in-vehicle applications, CAN is also being employed in the industry. It is usually used as a communication bus for message transaction in small-scaled distributed environment.

#### 1.1.2 Introduction

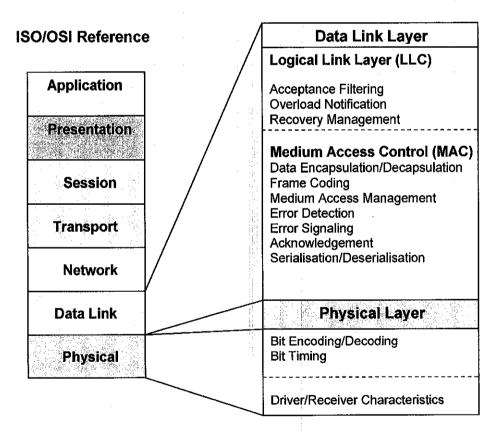

Layered approach is commonly used for network applications in system implementation. This systematic approach provides standards which enables interoperability between products from different manufacturers. Similarly for CAN, a layered approached has been applied in its protocol. CAN is internationally standardized by the International Standardization Organization (ISO) and the Society of Automotive Engineers (SAE) which provide a template for this layered approach. It is called the Open Systems Interconnection (OSI) Network Layering Reference Model (As illustrated in Figure 1.1). The CAN protocol itself implements most of the lower two layers of this reference model, the Data Link Layer and the Physical Layer [4].

Figure 1.1: ISO/OSI Reference Model [4]

As shown in Figure 1.1, the Data Link layer of CAN is further subdivided into two sub layers, which is the Logical Link Control (LLC) and Medium Access Control (MAC) sub layers. The Data Link layer is the only layer that recognizes and understands the format of messages. This layer constructs the messages to be sent to the Physical Layer, and decodes messages received from the Physical Layer [2].

The Physical layer on the other hand, specifies the physical and electrical characteristics of the bus. It is responsible for the transfer of bits between the different nodes in a given network. It defines how signals are transmitted and therefore deals with issues like timing, encoding and synchronization of the bit stream to be transferred. This layer is usually the hardware that converts the characters of a message into electrical signals for transmitted messages. It also converts messages from electrical signals into characters for received messages. Although the other layers may be implemented in either hardware (as chip level functions) or software, the Physical layer is always "real" hardware (usually a twisted pair of wire/cable or any other medium of transmission).

#### **1.2 PROBLEM STATEMENT**

Currently, low-cost CAN controllers and interface devices are available as off-theshelf parts manufactured by several of the leading semiconductor manufacturers such as Fujitsu, Hitachi, Intel, Texas Instruments and Phillips Semiconductors. Custom built devices and popular microcontrollers with embedded CAN controllers are also available. However, most of these CAN controllers are proprietary, and as such customization and further design evolution of the chips will require permission and consultation from respective manufacturers which in turn will incur more cost towards system development.

Besides, CAN technology is relatively new in Malaysia unlike in the United Kingdom where CAN has already received widespread used in different areas of expertise especially in automotive and industrial applications. It is hope that this project will serve as an introduction and familiarization with CAN technology in Malaysia. The results and research work of this project will serve as a foundation for future development of CAN in the country.

#### **1.3 OBJECTIVE AND SCOPE OF STUDY**

The main objective of this project is to be able to implement a section of CAN network bus with a reasonable degree of performance. The implementation will focus on the Transfer layer of CAN (explained further in Section 2.2.) which is responsible for the bit-level non-destructive arbitration of CAN controller.

The design is an FPGA-based implementation which includes the programming of a CAN controller system onto the FPGA demo board with hardware description language like VHDL (VHSIC Hardware Description Language) as the core programming language. One of the main CAN controllers must be able to handle collisions of signals by bit-level non-destructive arbitration process which is important in eliminating message re-transmission and unnecessary network overloading. Another CAN controller in the design will compete in the usage of the network bus with the main CAN controller. This is done to ensure that the arbitration process of the CAN system can be observed and analyzed whenever one or more nodes (represented by the CAN controllers) are sending message to the bus. The output signals of the CAN controller will then be analyzed and captured with a Logic Analyzer to investigate the arbitration of signals behavior in the controller.

In order to ensure that this project will be feasible within the scope and time frame, the concentration of this project will be largely based on the implementation of the message handling and collision section of CAN. The other principal functionality of CAN like error handling and remote data transfer will not be included. This project will be implemented within two semesters where the first semester covers on the understanding of the CAN concept and VHDL modules programming. For the second semester, design flow in accordance to the Xilinx FPGA implementation has been adopted.

## CHAPTER 2

## LITERATURE REVIEW

This section provide more information on the CAN protocol which includes the basic principle of CAN, the three layers significant in CAN, its message format and more on the non-destructive bit-level arbitration process. The information presented is mostly obtained from relevant books and online resources. More information on each section can be obtained from the direct source in which it has been referenced to (The number enclosed within the square brackets corresponds to the referenced item in the References Section). Besides, some information on the hardware description language used for this project, VHDL is included in this section as well.

## 2.1 BASIC CAN PRINCIPLE

With reference to [3] and [4], CAN principle has been described in this section. CAN is an advanced serial bus system that efficiently supports distributed control systems. It is a broadcast bus that has an open, linear structure with one logic bus line and equal nodes. CAN is also a message-based protocol, not an address based protocol. As such, the messages are not transmitted from one node to another node based on addresses but the message is broadcasted to all nodes and each message is referred to by an identifier within the message itself which indicates the message content and the priority of the message. This identifier is unique throughout the network. All other nodes on the network receive the message and each performs an acceptance test on the identifier to determine if the message, and thus its content, is relevant to that particular node. If the message is relevant, it will be processed, otherwise it is ignored. Since the nodes do not have addresses, the number of nodes may be changed dynamically without disturbing the communication of the other nodes.

## 2.2 CAN LAYERS

In order to achieve design transparency and implementation flexibility, CAN has been subdivided into different layers. They are:-

- The Object layer

- The Transfer layer

- The Physical layer

The object layer and the transfer layer comprise all services and functions of the data link layer defined by the ISO/OSI model (As being mentioned in Section 1.1) [11].

## 2.2.1 Object Layer

The scope of the object layer includes:

- Finding which messages are to be transmitted.

- Deciding which messages received by the transfer layer is actually to be used.

- Providing an interface to the application layer related hardware.

## 2.2.2 Transfer Layer

The scope of the transfer layer mainly is the transfer protocol which includes:-

- Controlling the framing

- Performing arbitration

- Error checking and error signaling

- Fault confinement.

#### 2.2.3 Physical Layer

The scope of the physical layer is the actual transfer of the bits between the different nodes with respect to all electrical properties. Within one network the physical layer, of course, has to be the same for all nodes. There may be, however, much freedom in selecting a physical layer.

## 2.3 CAN MESSAGE FRAME

With reference to [11], it is found that CAN protocol define four different types of messages (or Frames). They include:-

- Data Frame

- Remote Frame

- Error Frame

- Overload frame

The most common type of frame is a Data Frame. This is used when a node transmits information to any or all other nodes in the system. The second frame is called a Remote Frame, which is basically a Data Frame with the Remote Transmit Request (RTR) bit set. The other two frame types are for handling errors. One is called an Error Frame and the other one is called an Overload Frame. Error Frames are generated by nodes that detect any one of the many protocol errors defined by CAN. Overload errors are generated by nodes that require more time to process messages already received.

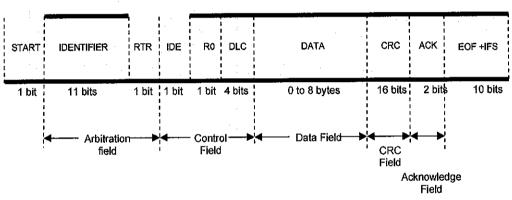

Data Frames and Remote Frames will be further explained. Data Frames consist of fields that provide additional information about the message as defined by the CAN specification. Embedded in the Data Frames are Arbitration Fields, Control Fields, Data Fields, CRC Fields, a 2-bit Acknowledge Field and an End of Frame.

The Arbitration Field is used to prioritize messages on the bus. Since the CAN protocol defines a logical 0 as the dominant state, the lower the number in the arbitration field, the higher priority the message has on the bus. The arbitration field consists of 12-bits (11 identifier bits and one RTR bit) or 32-bits (29 identifier bits, 1-bit to define the message as an extended data frame, an SRR bit which is unused, and an RTR bit), depending on whether Standard Frames or Extended Frames are being utilized. The current version of the CAN specification is Version 2.0B, which defines 29-bit identifiers. They are known as the Extended Frames. Previous versions of the CAN specification defined 11-bit identifiers which are called Standard Frames. The CAN protocol version will be explained further in Section 2.4.

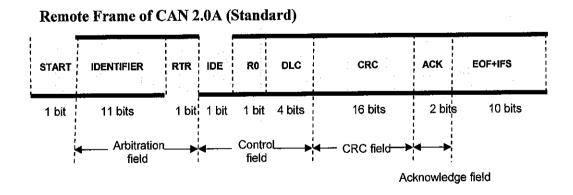

The Remote Transmit Request (RTR) is used by a node when it requires information to be sent to it from another node. To accomplish an RTR, a Remote Frame is sent with the identifier of the required Data Frame. The RTR bit in the Arbitration Field is utilized to differentiate between a Remote Frame and a Data Frame. If the RTR bit is recessive, then the message is a Remote Frame. If the RTR bit is dominant, the message is a Data Frame.

The Control Field consists of six bits. The most significant bit (MSB) is the IDE bit (signifies Extended Frame) which should be dominant for Standard Data Frames. This bit determines if the message is a Standard or Extended Frame. In Extended Frames, this bit is RB1 and it is reserved. The next bit is RB0 and it is also reserved. The four least significant bits (LSB) are the Data Length Code (DLC) bits. The Data Length Code bits determine how many data bytes are included in the message. It should be noted that a Remote Frame has no data field, regardless of the value of the DLC bits.

The Data Field consists of the number of data bytes described in the Data Length Code of the Control Field. The CRC Field consists of a 15-bit CRC field and a CRC delimiter, and is used by receiving nodes to determine if transmission errors have occurred. The Acknowledge Field is utilized to indicate if the message was received correctly. Any node that has correctly received the message, regardless of whether the node processes or discards the data, puts a dominant bit on the bus in the ACK Slot bit

The last two message types are Error Frames and Overload Frames. When a node detects one of the many types of errors defined by the CAN protocol, an Error Frame occurs. Overload Frames tell the network that the node sending the Overload Frame is not ready to receive additional messages at this time, or that intermission has been violated. Figure 2.1 and Figure 2.2 shows the Data Frame and Remote Frame for a Standard CAN (Version 2.0A).

Data Frame of CAN 2.0A (Standard)

Figure 2.2: CAN Remote Frame [13]

#### 2.4 CAN PROTOCOL VERSION

The CAN protocol supports two message frame formats, the only essential difference being in the length of the identifier. The CAN standard frame supports a length of 11 bits for the identifier, and the CAN extended frame, supports a length of 29 bits for the identifier.

## 2.5 DATA TRANSMISSION IN CAN

In any systems, some parameters will change more rapidly than others. It is likely that the more rapidly changing parameters need to be transmitted more frequently and, therefore, must be given a higher priority. To determine the priority of messages, CAN uses an established method known as CSMA/CD that is similar to that used in ETHERNET. However, besides the CSMA/CD technology, CAN have an enhanced capability of non-destructive bitwise arbitration to provide collision resolution, and to deliver maximum use of the available capacity of the bus.

The 'CSMA' stands for Carrier Sense Multiple Access. What this means is that every node on the network must monitor the bus for a period of no activity before trying to send a message on the bus (Carrier Sense). Also, once this period of no activity occurs, every node on the bus has an equal opportunity to transmit a message (Multiple Access). The abbreviation, 'CD' stands for Collision Detection. If two nodes on the network start transmitting at the same time, the nodes will detect the collision and take the appropriate action [2].

#### 2.5.1 Non-Destructive Bitwise Arbitration

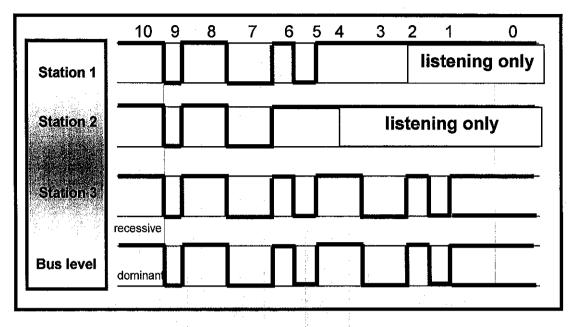

From [5], the following information has been further obtained. Bus access conflicts are resolved by non-destructive bit-wise arbitration in CAN in the transfer layer of the layered structure of CAN which is explained in Section 2.2. The protocol happens in accordance with the "wired-and" mechanism, by which the dominant state overwrites the recessive state. The priority of a CAN message is determined by the numerical value of its identifier. The numerical value of each message identifier

(and thus the priority of the message) is assigned during the initial phase of system design. A fundamental CAN characteristic in this sense is that the lower the message number, the higher its priority. Therefore, an identifier consisting entirely of zeros is deemed to be the highest priority message.

CAN utilize binary signaling with a high and low signal state and an idle signal state that is defined as high. To transmit a logical '0' bit, a node sinks the bus state to low for one bit time. This is called a dominant bit. To transmit a logical '1' bit, the state of the line is left high for one bit time. This is called a recessive bit. Collisionavoidance begins when two or more nodes simultaneously begin to transmit the first bit of their frame-identifier.

At any time during priority arbitration, a node transmitting a dominant bit (logical 0) has a higher priority than any node transmitting a recessive bit (logical 1). A node transmitting a recessive bit effectively monitors the bus state for one bit time. Upon detection of a dominant bit transmission, this node recognizes a higher priority frame and drops out of contention. This process is repeated over the length of the identifier. Given that the frame identifiers are unique, only one node can be left in contention at the end of the bit-wise arbitration. This effectively realizes a priority arbitration mechanism wherein the identifier with the lowest numeric value has the highest priority. Figure 2.3 shows an example of arbitration process in CAN.

Figure 2.3: An example of CAN arbitration process [5]

From Figure 2.3, station one and station two has lost in the arbitration of signals. Station 3 which have the highest priority (lowest identifier value) is thus in the transmitter mode and is successful in transmitting the complete data frame. Station 1 and Station 2 on the other hand, has switched to receiver mode upon detection of its arbitration state. In the receiver mode, the station only "listens" to the messages and will decide whether to accept or reject the messages. Station 1 and Station 2 and will resend the message (data frame) once the bus is free again (in recessive mode).

## 2.5.2 The Benefits of Non-Destructive Bitwise Arbitration

Non-destructive bitwise arbitration provides bus allocation on the basis of need, and delivers efficiency benefits that cannot be gained from either fixed time schedule allocation (e.g. Token ring) or destructive bus allocation (e.g. Ethernet.). With only the maximum capacity of the bus as a speed limiting factor, CAN is indeed more superior in term of message handling across transmission medium. Outstanding transmission requests are dealt with in their order of priority, with minimum delay, and with maximum possible utilization of the available capacity of the bus [2].

## 2.6 VHSIC HARDWARE DESCRIPTION LANGUAGE (VHDL)

From [6], [7] and [9], the following information has been obtained. VHDL is a hardware description language that can be used to describe and simulate the operation of a wide variety of digital systems, ranging in complexity from a few gates to an interconnection of many complex integrated circuits. It can describe a digital system at several different levels, which is behavioral, dataflow and structural. VHDL leads naturally to a top-down design methodology in which system is first specified at a high level and tested using a simulator. The simulator is used to verify the behavior of the digital circuit prior to expensive fabrication After the system is debugged at this level, the design can be refined, eventually leading to a structural description closely related to the actual hardware description.

VHDL program is unlike any conventional program written in either Pascal or FORTRAN. In VHDL, the focus is in describing the behavior of some physical system rather than how a function is computed. The VHDL description can be used to support two complimentary processes found in the design of digital system which is simulation and synthesis. Simulation and synthesis are complementary design processes. In both cases, the specification of the behavior of the digital system is the first step to c onstruct a VHDL model for the desired system. A V HDL simulator executes this model to mimic the behavior of the physical circuit where the behavior is described in terms of the occurrence of events and waveforms of signals. In contrast, digital circuit synthesis is the reverse process. A VHDL program is the input to a synthesis compiler that can process this description to generate the physical design of a circuit. Essentially, the synthesis compiler mimics the activities of what used to be a human chip designer job to generate a hardware design from an initial specification.

## CHAPTER 3

## **METHODOLOGY / PROJECT WORK**

This section describes the procedures and project flow used in implementing this project. Besides, the design stages from the project flow chart will be explained further in this section. The tools used in assisting this project have also been defined.

## 3.1 PROCEDURE IDENTIFICATION

Described in this section is the methodologies applied in order to achieve the final objective set. The methodology used has been illustrated with a project flowchart as shown in Section 3.1.1.

It is important to note that the tasks and workflow for this project is largely based on the Project Gantt Chart. Milestones have been set accordingly and the Gantt chart will be used as a guide along the duration of the project. It is important to note that the Gantt chart will be revised along the course of the project to suit the personal needs of the author as well as to cater for some unforeseen circumstances. Please refer to **Appendix 1** for the Project Gantt Chart.

3.1.1 Project Flow Chart

Figure 3.1 is a flow chart that illustrates the design process used in the implementation of this project.

Figure 3.1: Project Flow Chart

From Figure 3.1, it is observed that the methodology has been divided into two major phases which is Research and Development and FPGA Design Flow. The first phase consists of only one sub-stage which is the Design stage. The Design stage will be explained in Section 3.2.1. The FPGA Design Flow phase is a step-by-step method employed to implement the CAN design in FPGA chip. This phase consists of four sub-stages namely the Design Specification stage, Design Synthesis stage, Design Implementation stage and Device Programming stage which will be elaborated in Section 3.3.1, 3.3.2, 3.3.3 and 3.3.4 respectively.

The Research and Development phase includes preliminary research work on CAN from resources like books and internet as well as mastering the VHDL programming language. In semester one, the author completed the first phase and a section of the second phase which is until the Design Synthesis stage. The second semester is a continuation of work from the first semester until completion. In order to achieve the device programming stage, a systematic approach has been employed in order to achieve the final objective. The FPGA design flow has been adopted in order to be able to successfully program the CAN design into the FPGA chip.

## 3.2 **RESEARCH AND DEVELOPMENT**

3.2.1 Design Stage

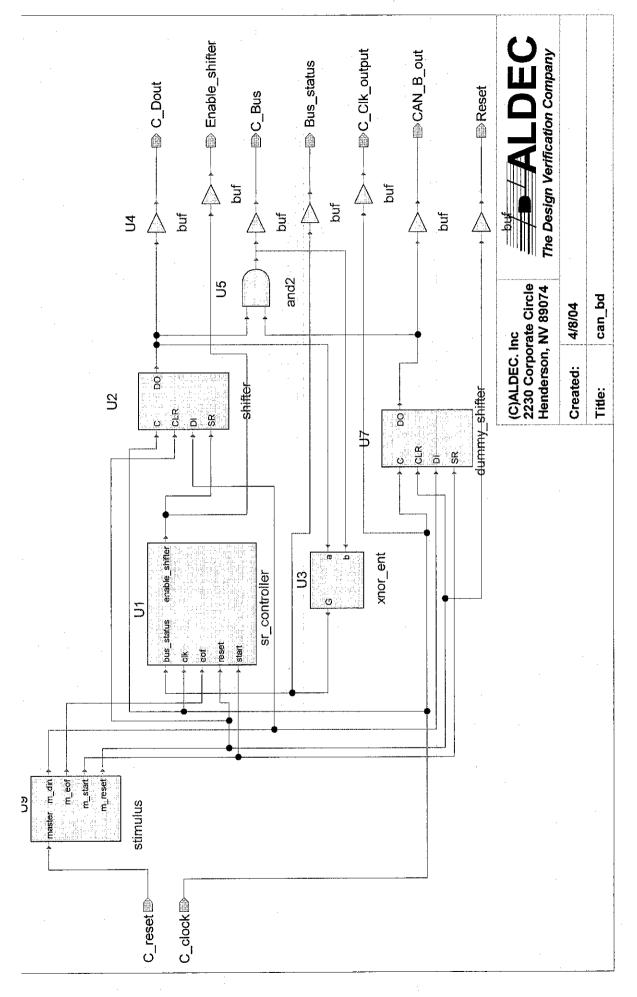

#### 3.2.1.1 Functional Block Diagram

The specification stage involves producing a Functional Block Diagram of a CAN controller with message arbitration capabilities. Figure 3.2 illustrates the block diagram for a CAN controller. From Figure 3.2, it is shown that four main modules are needed to design a CAN system. Enclosed within the double line box are three different modules or entities used to design a single CAN controller, say CAN controller A. The modules are a shift register controller, a shift register and a comparator which is basically an XNOR gate. Outside the double line box is another shift register, a dummy shift register which functions as another CAN controller, say CAN controller B which will only shift out a sequence of bits every clock cycle but

will not posses the arbitration properties of a real CAN controller. CAN controller B will compete in the use of the bus with CAN controller A. An AND gate which acts as the design physical bus is part of the FPGA design implementation to demonstrate the message handling capability of the controller across the bus which behave according to the "wired-AND" mechanism as discussed in section 2.5.1.

Figure 3.2: Functional Block Diagram for CAN controller

#### 3.2.1.2 CAN Message Handling Design System

In the CAN system, CAN controller A and CAN controller B must send out its identifier value to the bus first to determine its priority. As being mentioned in Section 2.5, CAN adopts a message-based protocol and priority of message is determined by its identifier. The lower the identifier value, the higher the priority. As such, any CAN controller with the lower identifier value will win the arbitration process (message handling process) and thus be able to proceed in sending out its message (the whole data frame) to the receiver across the bus. In this design, CAN

controller A will be set to have a higher identifier value than CAN controller B. As such, for this system, CAN controller B will win in the arbitration process as it has been given higher priority due to its lower identifier value as detected by the network system bus. This arbitration process protocol must be achieved to verify the functionality of the CAN message handling system. A diagram which illustrates the CAN message handling system has been shown Figure 3.3.

Figure 3.3: A CAN message handling system

#### 3.2.1.3 Finite State Machine (FSM) Chart

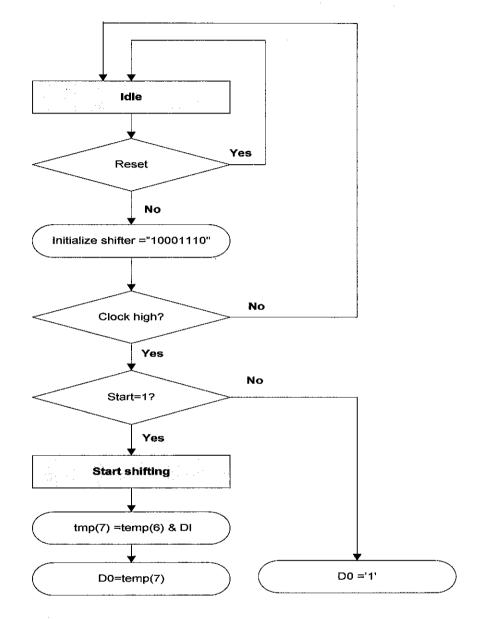

Finite State Machine (FSM ) chart that describes the shift register controller and shift register in accordance to the functional block diagram are then drawn to assist in the HDL programming stage. A Finite State Machine flowchart leads directly to a hardware realization using VHDL. Basically, the VHDL description of these systems is constructed from the FSM Chart and the VHDL codes are then simulated (RTL behavioral simulation described in C hapter 4) to verify its correct operation. The FSM charts of both the shift register controller and shift register are shown in Figure 3.4 and Figure 3.5 respectively.

Finite State Machine Chart For Shift Register Controller

Figure 3.4: Finite State Machine Chart for Shift Register Controller

**Finite State Machine Chart for Shift Register**

Figure 3.5: Finite State Machine Chart for 8-bit Serial-in, Serial-out Shift Register

From Figure 3.4, it can be observed that the shift register controller has only two states. The minimal number of stages used ensures a more efficient approach to handle the controller. This is because the state of the design is synchronous and relies on the system clock. With less state changes when the design is triggered, the results can be observed immediately. This is an important criterion as the design is a time-critical design according to Mealy state machine. As such, the outputs are a function of the inputs and the current state. Hence, with fewer states, state transition can be designed to happen immediately in the current clock cycle instead of changing only during the next clock cycle. This is an important protocol as the message handling process of each controller must be quick in response. Any failure to do that will disrupt the message sending process.

From Figure 3.5, the shift register module is initially idle. At this idle state, its output (D0) is set to be logic '1' to signify that it is idle. It is designed to send out a sequence of bits after reset is initiated and its start input is activated. The bits will be shifted out serially according to its initialization bits. From the figure, the initialization bits are set as "10001110". After the first eight bits being shifted out, the follow-up bit will be in accordance to the state of the shifter input, DI. The similar process repeats after a reset.

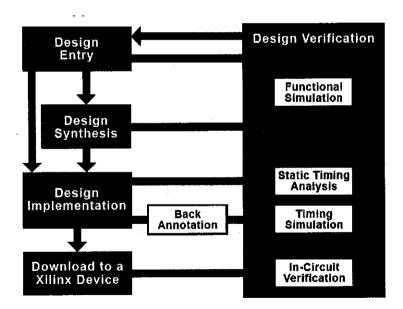

## 3.3 FPGA DESIGN FLOW

The general FPGA design flow diagram employed is shown in Figure 3.6. This is the overall development methodology used in implementing the CAN design in FPGA.

Figure 3.6: FPGA Design Flow [14]

## 3.3.1 Design Specification Stage

After the first phase, intensive coding with VHDL language is done in accordance to the FSM chart produced earlier in Section 3.2.1. Active-HDL 5.1 program is used as the authoring platform. Simpler module like the XNOR gate code is obtained from web resources and being modified accordingly to suit the needs and specification of the design. Block diagram is used to interconnect the smaller module of the design to produce the top-level module which can be automatically generated by the Active-HDL program. The top-level module is used to tie all other modules to form a complete design of the CAN controller. Please refer to Appendix 2 for the VHDL source codes for each entity/module and Appendix 3 for the Top-level module block diagram.

#### 3.3.2 Design Synthesis Stage

Synthesis is the transformation of an idea into a manufacturability device to carry out an intended function. It other words, it can also be described as the transformation of a design from abstract to concrete design [14]. Synthesis will be done using Active-HDL 5.1 and Xilinx Synthesis Technology (XST) program packaged within the ISE Design Environment 4.2i.

The source code for the Comparator, Shift registers, Shift register controller and toplevel CAN controller entities will be compiled and synthesized using the Active-HDL program and later migrated to the Xilinx ISE Design Environment 4.2i tool to be synthesized again. Simulation is performed on each entity to ensure that the design works according to specification. As such, Register Transfer Level (RTL) simulation is done to determine and analyze the functionality of the design and to verify the correctness of the RTL VHDL description. The simulated output can also be used to measure the performance of the design and further improvement on the design can be done to improve its performance. The results and the corresponding discussion on the RTL simulation carried out in this project will be presented in Chapter 4.

#### 3.3.3 Design Implementation Stage

Design implementation stage begins with the mapping of a logical design file to a specified device and is complete when the physical design has been successfully routed and a bitstream is generated [14]. Design implementation is also done using the ISE Design Environment 4.2i. The software uses the following design flow engine to carry out the implementation stage.

- i. **Translate** Merge all input netlist to form a complete full chip netlist. This is done by running the *NGDbuild* program.

- ii. **Map** Optimizes the merged netlist by NGDbuild. This can be accomplished by running the program, *MAP*.

- iii. **Place & Route** All logic blocks are assigned specified location within the die. Routing (connection) of logical blocks are done by the program, *PAR*.

- iv. Configure Configures the physical implementation into binary stream. This is accomplished by the program *BitGen*. *PromGen* program will then converts *BitGen* into PROM file format.

- v. Timing Performs timing analysis by *TRACE* program.

Before an implementation, constraints must first be set. Constraints are instructions placed on symbols or nets in an FPGA schematic or textual entry file such as VHDL or Verilog. They can indicate a number of things such as placement, implementation, naming, signal direction, and timing considerations.

In the Xilinx development system, logical constraints are placed in a file called the User Constraints File. The Xilinx Constraints Editor which is integrated within the ISE Design Environment software is used to create and modify timing and physical constraints of the design. Input files to the Constraints Editor are the UCF file. Constraints created by the user are written to this file and NGD (Native Generic Database) file. This file serves as input to the mapper, which generates the physical design database (NCD file). *NGDBuild* uses the UCF file and design source netlists to produce an NGD file. The NGD is read by the *MAP* program, which generates an

NCD file (a physical design database) and a PCF (Physical Constraints File). The implementation tools use the NCD and PCF files to produce a bitstream. The UCF file can be viewed from Appendix 13.

#### 3.3.4 Device Programming Stage

Device programming is the process of loading a design-specific programming into one or more FPGAs in order to define the functional operation of the internal blocks as well as their interconnections. The Xilinx device which will be used for this project is re-programmable and it also supports in-system programming. Device programming is done using the *iMPACT* program within the ISE Design Environment.

The *iMPACT* configuration tool is a command line and GUI based tool, which allows user to configure FPGA designs using Boundary-Scan, Slave Serial, and Select Map configuration modes. Boundary-Scan mode is an industry standard serial programming mode and will be the selected mode to perform the design. External logic from a cable, microprocessor, or other device is used to drive the JTAG specific pins, Test Data In (TDI), Test Mode Select (TMS), and Test Clock (TCK) and sense device response on Test Data Out (TDO). This mode is the most popular mode of configuration due to its standardization and ability to program FPGAs, PLDs, and PROMs through the same four JTAG pins. [14]

There is a specific order in which commands must be executed using the *iMPACT* tool. The following steps are performed to initiate the device programming process:

- i. Set the configuration mode

- ii. Set up the cable port

- iii. Define the JTAG chain and assign files

- iv. Program the device

- v. Verify the device

- vi. Exit from the programming software

24

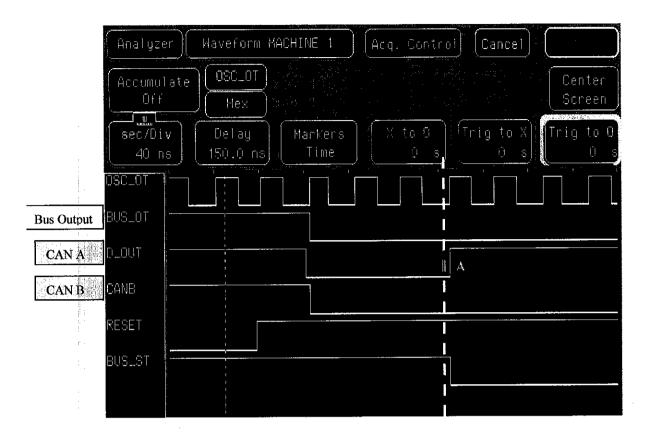

The programmed device will be verified by checking the output signals of the board using a Logic Analyzer. The results will be analyzed and discussed in Chapter 4.

#### 3.4 TOOLS USED

The software required to assist in the implementation of this project are the Active-HDL 5.1 and Xilinx ISE 4.2i Design Environment software which is used to perform the steps in Section 3.2 and Section 3.3.

The FPGA board that used in the project is the Virtex II XC2V1000-FG256 demo board by Insights Electronics Inc, distributed by Memec Design. The Xilinx XC2V1000 FPGA chip used in the project is mounted on the Xilinx FPGA demo board. The FPGA chip on the board contains as much as one million logic gates. The board utilizes the Xilinx XC18V04 ISP PROM, which allows user to download revisions of a design and verify the design changes in order to meet the final systemlevel design requirements. In addition to ISP PROM, the board also provides a JTAG connector for direct configuration of the Virtex II FPGA. The graphical picture as well as the reference board block diagram of the Xilinx Virtex II demo board is shown in **Appendix 14**.

The output signals from the FPGA chip will be analyzed using a Hewlett Packard (HP) 1673G Series Logic Analyzer.

## CHAPTER 4

## **RESULTS AND DISCUSSION**

In this section, the RTL simulation results for all the design modules are shown. The waveforms obtained are then analyzed to check if the results are as desired and whether it conformed to the design specifications and requirements. Besides, the results of design implementation and device programming have also been presented in this section. The final design output from the FPGA captured with the Logic Analyzer is being compared with the RTL simulation and discussed further.

#### 4.1 **DESIGN SIMULATION RESULTS**

Two methods of RTL simulation has been employed in verifying the modules of the design. One is simulation using stimulus and the other is simulation with test benches. Some explanation on both methods is provided in Section 4.1.1 and Section 4.1.2. The corresponding simulation results and discussions for both methods are also provided.

4.1.1 RTL simulation using stimulus

This method of simulation is considered manual simulation as the stimulus is set by the designer itself. In the Active-HDL program, the stimulus is set using "HOTKEY" which is any of the keys from the keyboard to represent a signal state. A stimulus or stimulator that represents the design environment is then used to drive the design and check to make sure that the results produced by the design are as expected. A standard VHDL simulator can be used to read the RTL VHDL description and to verify the correctness of the design. The VHDL simulator reads the VHDL description and then compiles it into an internal format which then executes the compiled format using test vectors [12].

By observing the output waveforms from the simulation, the functionality of the design can be verified. The waveform display shows the values of the signals of the design over time. The results of the simulation using stimulus for XNOR gate, shift register and shift register controller and top-level CAN controller are shown in Figure 4.1, Figure 4.2, Figure 4.3 and Figure 4.4 respectively.

| Name          | Value | Stimula | ı - 50 - i - 100 - i - 150 - i - 200 - i - 250 - i - 300 - |

|---------------|-------|---------|------------------------------------------------------------|

| ₽• a          | 1     | Q       | Input 1                                                    |

| . <b>в-</b> ђ | 1     | W       | Input 2                                                    |

| - <b>9</b> G  | 1     |         |                                                            |

Figure 4.1: RTL simulation using stimulus for XNOR gate

From Figure 4.1, the results obtained is as desired. The output (G) of the XNOR gate is a logic high (logic '1') if both inputs (a and b) is similar (either a = b = '0' or a = b = '1') while the output is logic low (logic '0') if both inputs are not similar. This is the b ehavior expected from that of an XNOR gate. The XNOR gate is used as a comparator in this CAN design to compare the signals transmitted and received again from controller A to check if it has been arbitrated or not. The comparator will compare the output signals obtained from the CAN controller before and a fter its output passed through the AND gate. The AND gate is used to emulate a real physical bus which have the characteristic of an AND gate when it carries messages.

| Name          | Value | Stimulator | 500 ns                                                             |

|---------------|-------|------------|--------------------------------------------------------------------|

| <b>B-</b> ()  | 1     | Clock      |                                                                    |

| er-`DI        | 1     | <= 1       | Skilter_input                                                      |

| ► CLR         | 1     | R          |                                                                    |

| ⊳ SR          | 1     | S          | Start_shifter                                                      |

| E 🖷 Imp       | EF    |            | Internalstorage<br>(UJ X8E XID X3B X77 XEF XDF XBF X6E XID X3B X77 |

| - <b>0</b> DO | 0     |            | Shifter output                                                     |

Figure 4.2: RTL simulation using stimulus for 8-bit shift register

The shift register is an 8-bit serial-in, serial-out shift register and it is set to have input initialization bits of "10001110". The shift register will shift the bits at each clock event (clock high). From Figure 4.2, the clock frequency is set at 25 MHz to emulate the clock frequency of the FPGA on-board oscillator. *CLR* represents a reset and the design must be reset before it is activated. As soon as the shifter is initiated by starting up the shifter (SR = '1'), it is observed that the first eight bits of the shifter output (*D0*) is "10001110", which is the initialization bits of the shifter input value (*D1*) which is "1" until the shifter is reset again. The shifter input (*D1*) allows real time input into the shifter. From the simulation, it is shown that during the second reset, the output will again be similar to the input initialization bits as the shifter is being reset after the eleventh bit. This is the case as after reset, the shifter will be restored with the eight initialization bits again.

The RTL simulation for the dummy shift register module will not be shown as it has similar characteristic to that of this shift register. The only slight difference is in its initialization bits output. The dummy shift register is set to have an initialization bit of "100000000". And as such, it will shift out the initialization bits every clock cycle. Similarly the shifter input (DI) has been set at '1'.

| Vame             | Value | Stimulator T | 50 100 150 200 250 300 350 400 450<br>500 n |

|------------------|-------|--------------|---------------------------------------------|

| ı∎- start        | 1     | S            | Start                                       |

| . ₱~ reset       | 1     | R            | Reset                                       |

| ► clk            | 1     | Clock        |                                             |

| ₽- bus_status    | 0     | 8            | Bus Status                                  |

| P eof            | o     | <= 0         | End of Frame                                |

| • enable_shifter | 0     |              | Enable Shifter                              |

| ≢r Tstate        | 1     |              | Currentstate                                |

| ∎ Tnext          | 1     |              | Next State                                  |

Figure 4.3: RTL simulation using stimulus for shift register controller

The clock frequency is set at 25 MHz. The value 25 MHz is chosen as the on-board oscillator of the FPGA demo board is approximately this frequency range. The input signals are *start*, *reset*, *clk*, *eof* and *bus status* while the output signals are *enable\_shifter*. The *Tstate* and *Tnext* are the internal signals which represent the states of the design.

From Figure 4.3, it is observed that the shift register controller is activated when the signal is fed into its '*start*' input. The *bus\_status* signal as it names implies indicates whether the bus is free or busy. A logic '1' represents the bus is free while logic '0' represents the bus is busy. The shift register controller will output a logic '1' signal (*enable\_shifter* = '1') whenever the bus status is not busy and vice versa. This is the signal that will be used to enable or disable the shift register.

|              | Name             | Value | Stimu | 0 ps - 50 · 1 · 100 · · 150 · 200 · 250 · 300 · 350 · 400 |

|--------------|------------------|-------|-------|-----------------------------------------------------------|

|              | ₽- C_clock       | 0     | Clock |                                                           |

|              | - C_Clk_output   | 0     |       |                                                           |

| Master reset | _∎- C_reset      | 0     | R     |                                                           |

|              | -® Bus_status    | U     |       |                                                           |

| Controller A | _== C_Dout       | U     |       | Lost in arbitration                                       |

| Controller B | P CAN_B_out      | U     |       | Won in arbitration                                        |

| US OUTPUT    | <b>−</b> ∎ C_Bus | U     |       |                                                           |

I.

X

Figure 4.4: RTL simulation using stimulus for top-level CAN controller

Referring to Figure 4.4, C bus is the output from the AND gate, which in this case, acts as a physical bus which carries the messages transmitted by the transmitter (Controller A and Controller B) to the receiver. C Dout is the output from CAN controller A, the main CAN controller which exhibits the arbitration characteristics. C\_clock is the clock input which has been set at 25 MHz. C\_Clk output is the clock output. The reason the clock output is checked is to ensure that the clock goes into the design during the design implementation stage. C reset is the master reset of the system. Before the start of the message sending process, the C reset input must be set to low (Logic '0') to reset the whole system. Bus status is an output which represents the status of the bus whether the bus is free or busy. Comparing the waveform of C\_bus, C Dout and C CAN B\_out, it was found that the waveform for C bus and C CAN B out is similar. Hence, the bus is actually carrying the sequence of bits sent by CAN Controller B. This shows that CAN controller B has actually won in the arbitration process. CAN controller A has lost in the arbitration process at X (please refer to Figure 4.4) because it has a higher identifier value as compared to CAN controller B. This means that controller B actually has a higher priority than controller A and is given the bus allocation.

The results obtained indicate that the design has met with the specification of a CAN system during message handling. The arbitration of signals has been exhibited by the controller when it lost in the bus allocation due to its lower priority identifier.

#### 4.1.2 RTL simulation using Test Bench

A test bench is a design entity which serves as a host environment for another design being tested. Test bench is not real device or a system that must communicate with its environment and as such it does not need any inputs or outputs. The tested entity is called Unit Under Test (UUT) and it is instantiated in the test bench architecture. The ports of the UUT instantiation will be assigned stimuli signals by the test bench architecture. The heart of each test bench is a set of stimuli which is a sequence of values for each UUT input signal applied over time. Since test bench does not communicate with its environment through signals, all stimuli must be declared internally in the test bench architecture like any other signals inside the VHDL architecture declarative part. Test vectors used to simulate the UUT entity can be furnished in an external file or encoded immediately in the test bench architecture [10].

The advantage of using test bench is the fact that once test bench is generated as well as its test vectors are specified, it can be reused many times to perform simulation and automatic verification of our design regardless of any successive revisions of the VHDL designs. The predicted outputs can also be coded into the test bench. As such, the test bench not only prepares the test vectors but can verify the expected output from the design. As such, the outputs can be check once the test bench is run and the outcome or results for the simulation can be reported. Report clause is used in the test bench to display messages when something goes wrong or if the simulation is not successful. The report of simulation can be viewed from the console window of the VHDL program.

Due to constant revisions being done on the design entities, test benches are written for the shift register module, shift register controller module as well as the top-level CAN controller module to verify their functionality. The results of the test bench simulations are shown in Figure 4.5, Figure 4.6, Figure 4.7 and Figure 4.8. The results of the test bench can be viewed from the *ERR\_STATUS* (error status) output. Besides, a report will be generated on the console window by the Active-HDL program to indicate the successful simulation status. An example of the generated report for the top-level CAN controller module is shown in Figure 4.9. The test benches source codes can be viewed at **Appendix 4**.

| Name         | Value       | Stimulator / | ı 50     | , 100 i | 150 200 | 1 250 1 300   |

|--------------|-------------|--------------|----------|---------|---------|---------------|

| ≠r STIM_a    | 1           |              |          |         |         |               |

| ≉ STIM_b     | 1           |              |          |         |         |               |

| ⊯ Actual_g   | 1           |              |          |         |         |               |

| ■ EXPECT_G   | •           |              | <u> </u> |         |         |               |

| ⊞ # WPL      | [?,(stimulu |              |          | XX      | X       | X X(7,(stimul |

| ■ ERR_STATUS | L           |              |          | 1       |         |               |

Figure 4.5: Test bench simulated output for XNOR gate.

| Name         | Value        | Stim           | 1         | 60 |           | 100 | i i | 150      | 14         | 200 |        | 25 |         | . 3 | ọo ∙      | •      | 350 | 1.4 | 400 | 1.1      | 450 5 | 00 ps |

|--------------|--------------|----------------|-----------|----|-----------|-----|-----|----------|------------|-----|--------|----|---------|-----|-----------|--------|-----|-----|-----|----------|-------|-------|

| • STIM_C     | 0            |                | ு         |    | $\square$ |     |     |          |            |     |        |    |         | 1   |           | ſ      |     |     |     | Г        |       |       |

| ■ \$TIM_DI   | 1            |                |           |    |           |     |     |          |            |     |        |    |         |     |           |        |     |     |     |          |       |       |

| ≠ STIM_CLR   | 1            |                |           |    | <u></u>   |     |     |          |            |     |        |    |         |     |           |        |     |     |     |          |       |       |

| STIM_SR      | 1            |                |           |    |           |     |     |          |            |     |        |    |         |     |           |        |     |     |     |          |       |       |

| ■ ACTUAL_DO  | 0            |                | F         |    |           |     |     | 7        |            |     |        |    | <u></u> |     |           |        |     |     |     | <u> </u> |       |       |

| # EXPECT_DO  | -            | alonda Helibla | <u>77</u> |    |           |     |     |          |            |     | . I    |    |         |     | Π         |        | ·   | [   |     |          |       |       |

| ⊕ # WPL      | (0?,(stim.,. |                | $\square$ |    | $\Sigma$  |     | χ_  | $\Sigma$ | $\bigcirc$ |     | $\Box$ | X  | Χ       | X   | $\square$ | $\Box$ |     |     | χ   | $\sum$   |       | XIOEL |

| # EAR_STATUS | L            |                |           |    |           |     |     |          |            |     | :      |    |         |     |           |        |     |     |     |          |       |       |

Figure 4.6: Test bench simulated output for 8-bit shift register.

| Name                    | Value    | Stim |          | <u>, </u>      | 50       | •     | 100     | 1       | 150     |   | 200       | i 25 | j0 i | 30 | 0 1          | 350          |         | 400          | <u>, </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 450                 | - 52 | 0 ns  |

|-------------------------|----------|------|----------|----------------|----------|-------|---------|---------|---------|---|-----------|------|------|----|--------------|--------------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|

| ≠ STIM_start            | [1       |      |          |                |          |       |         |         |         |   |           |      |      |    |              |              |         |              | d=H-17HP17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |      |       |

| #" STIM_reset           | 0        |      |          |                |          |       |         |         |         |   |           |      |      |    |              |              | unnanti |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |      | L     |

| ≠ STIM_ck               | 0        |      |          |                |          | ٦.    |         | ٦       | ſ       |   | <u>רר</u> |      |      | ப  |              |              |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ப                   |      |       |

| ■ STIM_bus_status       | l0       |      |          | 0000000        | n-m-11-1 |       |         |         | -       |   | <u></u>   |      |      |    | 101000000000 |              | mannika |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | **** |       |

| ≖ STIM_eof              | Ø        |      | <u> </u> |                |          |       |         |         |         |   |           | ·    |      |    |              |              |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |      |       |

| # ACTUAL_enable_shifter | 0        |      |          |                |          |       |         |         |         |   |           |      |      |    |              |              |         |              | and the second s |                     |      |       |