### CAR'S OBJECT DETECTION AND AVOIDANCE SIMULATION USING VERILOG

By

### MOHD KHUWARIZMI BIN MOHAMAD ROSLAN 4104

### FINAL PROJECT REPORT

Submitted to the Electrical & Electronics Engineering Programme in Partial Fulfillment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2007 by Mohd Khuwarizmi Bin Mohamad Roslan, 2007

ii

### **CERTIFICATION OF APPROVAL**

### CAR'S OBJECT DETECTION AND AVOIDANCE SIMULATION USING VERILOG

by.

Mohd Khuwarizmi Bin Mohamad Roslan

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved:

Ms Salina Bte Mohamad Project Supervisor

> UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

> > June or December 2007

iii

### **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Mohd Khuwarizmi Bin Mohamad Roslan

### ABSTRACT

The advancement of automotive industry in the last century has produced better and faster car. However, all that comes with worrying trend of increasing accident on the road. A key challenge today is to develop electronics gadgets or equipment that can help to reduce the statistic significantly. Advanced safety systems that sense impending danger – such as a collision or a potential rollover – and alert the driver can be introduced on the vehicle to achieve the target of reducing accidents. Multiple high-end sensors can be used to diagnose the car conditions or to detect nearby objects and irregularities. On-board processing will then be performed to determine the appropriate actions to be taken. The processor will then communicate with one of the actuators in view of alerting the driver or avoiding the danger. This project aims to simulate the necessary action to be taken when the car is within the danger range. For this project, the scope of the accident causality is only focus on crushing the object/vehicle in front and the necessary action taken are to be the driver alert system and engaging Anti-lock Brake System (ABS).

### ACKNOWLEDGEMENTS

First and foremost, thank to Allah swt, the most Gracious & the most Merciful. Much gratitude to Ms Salina Mohamad for her guidance and advice through out the project development. Thanks to my friends who help me along the way in the projects.

## TABLE OF CONTENTS

| LIST OF TAE | BLES    |                                                      | ix |  |  |  |  |

|-------------|---------|------------------------------------------------------|----|--|--|--|--|

| LIST OF FIG | URES.   |                                                      | x  |  |  |  |  |

| LIST OF ABE | BREVL   | ATIONS                                               | xi |  |  |  |  |

| CHAPTER 1   | : INTH  | RODUCTION                                            | 1  |  |  |  |  |

| 1.1         | Backg   | round                                                | 1  |  |  |  |  |

| 1.2         | Proble  | m Statement                                          | 2  |  |  |  |  |

| 1.3         | Object  | bjectives and Scope of Study 3                       |    |  |  |  |  |

| CHAPTER 2   | • 1 171 | ERATURE REVIEW                                       | А  |  |  |  |  |

| 2.1         |         | se of Research in Improving Vehicle Safety Features  |    |  |  |  |  |

| 2.1         |         | e-Safety System                                      |    |  |  |  |  |

|             | 2.1.1   | 2.1.1.1 Adaptive Brake Lights                        |    |  |  |  |  |

|             |         | 1 0                                                  |    |  |  |  |  |

|             |         | 2.1.1.2 Automatic Headlight                          |    |  |  |  |  |

|             |         | 2.1.1.3 Driver Condition Monitoring                  |    |  |  |  |  |

|             |         | 2.1.1.4 Dynamic Control Systems                      |    |  |  |  |  |

|             |         | 2.1.1.5 Lane Departure Warning                       |    |  |  |  |  |

|             |         | 2.1.1.6 Obstacle & Collision Warning                 | 6  |  |  |  |  |

|             | 2.1.2   | Cooperative Intersection Collision Avoidance Systems |    |  |  |  |  |

|             |         | (CICAS)                                              | 7  |  |  |  |  |

|             |         | 2.1.2.1 CICAS Overview                               | 7  |  |  |  |  |

| 2.2         | Progra  | mming Language Used for the Project                  | 9  |  |  |  |  |

|             | 2.2.1   | Design Styles                                        | 10 |  |  |  |  |

|             |         | 2.2.1.1 Bottom-Up Design                             | 10 |  |  |  |  |

|             |         | 2.2.1.2 Top-Down Design                              | 10 |  |  |  |  |

| CHAPTER 3   | : ME    | rhodology                                            | 11 |  |  |  |  |

| 3.1         |         | luction                                              |    |  |  |  |  |

| 5.1         | 3.1.1   | Understanding on How the System Works                | 12 |  |  |  |  |

|             | 3.1.2   | Planning the Process Flow of the System              |    |  |  |  |  |

|             | 3.1.2   | Develop Behavioral Code                              |    |  |  |  |  |

|             |         | Simulation                                           |    |  |  |  |  |

|             | 3.1.4   | Simulation                                           | 12 |  |  |  |  |

| CHAPTER 4 | : RES  | ULT AND DISCUSSION                                     | 13   |

|-----------|--------|--------------------------------------------------------|------|

| 4.1       | Under  | standing on How the System Works                       | 13   |

| 4.2       | Planni | ng the Process Flow of the System                      | 15   |

| 4.3       | Develo | op Behavioral Code                                     | 16   |

|           | 4.3.1  | Speed Converter Module                                 | 16   |

|           |        | 4.3.1.1 Truth Table for Speed Converter Module         | 17   |

|           | 4.3.2  | Time to Collision (ttc) Module                         | 18   |

|           | 4.3.3  | Response to be Taken                                   | 18   |

| 4.4       | Simul  | ation                                                  | 19   |

|           | 4.4.1  | Simulation result of Speed Converter Module            | 19   |

|           | 4.4.2  | Simulation result of Time to Collision Module          | 20   |

|           | 4.4.3  | Simulation result of Action Taken Module               | 21   |

|           | 4.4.4  | Simulation result of the overall system : Car's Object |      |

|           |        | Detection and Avoidance (CODA)                         | 22   |

|           |        |                                                        |      |

| CHAPTER 5 | : COI  | NCLUSION AND RECOMMENDATION                            | 23   |

| 5.1       | Conc   | lusion                                                 | . 23 |

| 5.2       | Reco   | mmendation                                             | 23   |

|           |        |                                                        |      |

| REFERENCE | S      |                                                        | 24   |

| APPENDICE | s      |                                                        | 25   |

### LIST OF TABLES

.

| Table 1 : Truth table of Speed Converter Module                    | 17         |

|--------------------------------------------------------------------|------------|

| Table 2 : Category based on time to collision value                | 1 <b>7</b> |

| Table 3 : Summary of time to collision with the respected category | 18         |

| Table 4 : Test set values for the Speed Converter Module           | 19         |

| Table 5 : Test set values for the Time to Collision Module         | . 20       |

| Table 6 : Test set values for the Action Taken Module              | 21         |

| Table 7 : Test set values for CODA                                 | 22         |

## LIST OF FIGURES

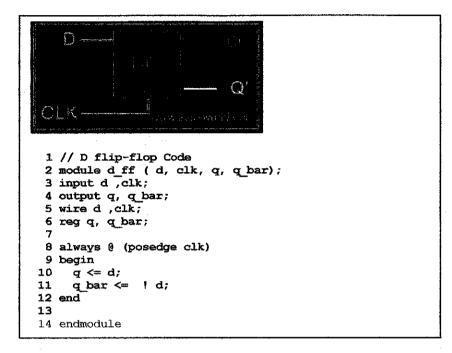

| Figure 1 : Example of Verilog coding              | 9    |

|---------------------------------------------------|------|

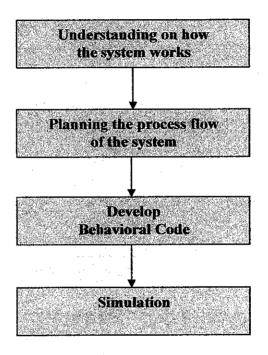

| Figure 2 : Process flow of the project            | 11   |

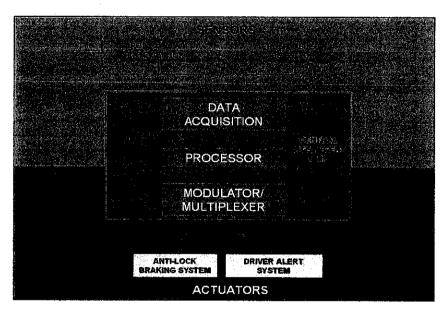

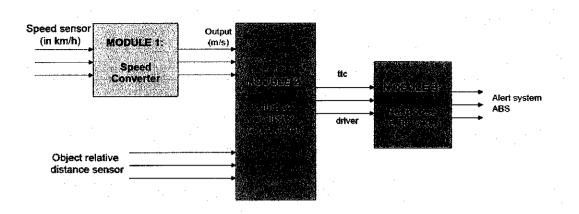

| Figure 3 : Conceptual diagram                     | 14   |

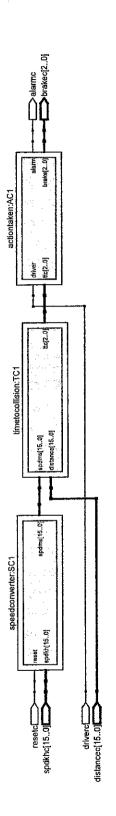

| Figure 4 : System block diagram                   | 14   |

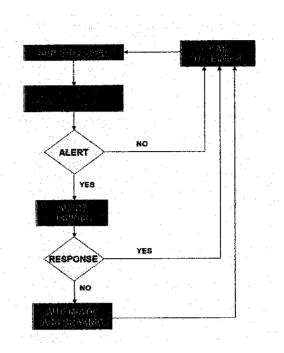

| Figure 5 : Process flow of the system             | 15   |

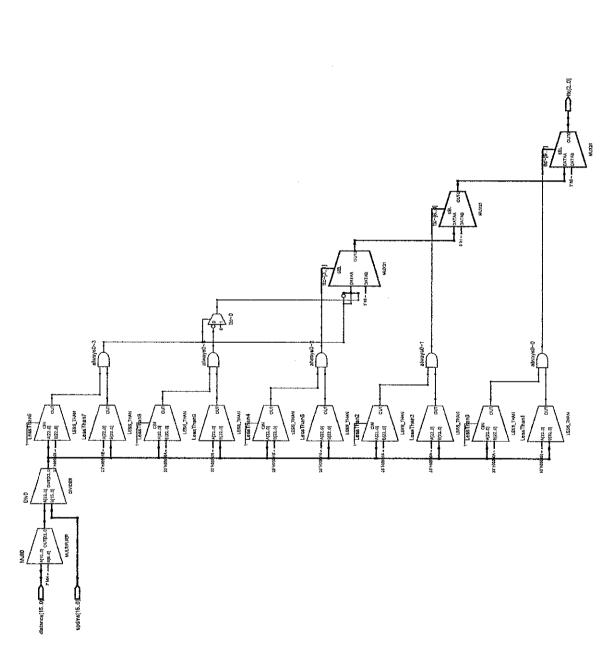

| Figure 6 : Modules of the System                  | 16   |

| Figure 7 : Simulation of Speed Converter Module   | 19   |

| Figure 8 : Simulation of Time To Collision Module | . 20 |

| Figure 9 : Simulation of Action Taken Module      | . 21 |

| Figure 10 : Simulation of CODA                    | 22   |

|                                                   |      |

## LIST OF ABBREVIATIONS

| Car's Object Detection and Avoidance Simulation using Verilog (CODA) | 1 |

|----------------------------------------------------------------------|---|

| Anti Lock Brake System (ABS)                                         | 1 |

| Electronic Stability Control (ESC)                                   | 6 |

| Active Body Control (ABC)                                            | 6 |

| Long Range/Near Range Radar Sensors (LIDAR)                          | 6 |

| Cooperative Intersection Collision Avoidance Systems (CICAS)         | 7 |

| Hardware Description Language (HDL)                                  | 9 |

## CHAPTER 1 INTRODUCTION

### 1.1 Background

Car accident's rate has been increasing from time to time. This results in severe injuries and deaths. As vehicle are generally traveling faster and the roads are getting more crowded than before, driving has become more difficult than before. Many reasons have been associated with the accidents, but by being extra alert to their driving, a driver can avoid the imminent collision.

A Car's Object Detection and Avoidance Simulation using Verilog (CODA) is a simulation of a system that helps the driver to be alerted to the incoming danger or even takes necessary action automatically. The system consists of a list of sensors, a central electronics system and some actuators. An accelerometer is being used to determine the running state of the vehicle.

Other sensors such as front detector is added to detect the nearby objects and together with the car running data, the intelligent electronics system can determine whether the driver is in danger or not. The driver will be alerted first once the system triggered the distance between car and the object is within the danger zone. If there are no responses taken from the driver, the system will automatically execute the Anti Lock Brake System (ABS). The force to be applied to the ABS depends on the distance between the car and the object. The shorter the distance the more force will be applied.

### 1.2 Problem Statement

Many alternatives and methods have been done to reduce the accident rates in Malaysia. However, there is still no positive result and yet the accident rate is increasing. Base on the analysis done by the Ministry of Transportation, the main cause of the accident is the drivers themselves; the attitude of driving, carelessness and others. On the other hand, there are also factors that can cause the driver to lost control of the vehicles such as road and the vehicle conditions.

Even though the car's manufacturers nowadays have applied the advanced technology in order to increase the safety features of their cars, accident rate is still at the critical level. Obviously, it is not what the technology applied that affluence the accident to occur, it is a matter of how the technology and the safety features are used. In other words, it is the responsibility of the drivers to ensure their safety. However, human are not machines. The tendency of being fatigue, less focus or panic can cause them not to use the technologies or safety features provided when they are supposed to use them.

Accidents can occur in milliseconds time and under critical time human normally cannot think and react rationally. This is where an intelligent system can 'assist' the driver. They can 'think' for the driver and even 'react' if the driver's response is slow. The system however has to be very accurate in order to ensure the best corrective action is taken to avoid any accident.

### 1.3 Objectives and Scope of Study

The main goal of this project is to simulate a system of Car's Object Detection and Avoidance Simulation using Verilog. The system is capable of determining an event where a car approaches an object or vice a versa. By knowing the approaching speed and also the car speed, the circuit shall be able to determine the collision time and take necessary actions such as warn the driver and engaging Anti-lock Braking System (ABS). In developing the simulation, the Quartus Version 6 is used.

......

## CHAPTER 2 LITERATURE REVIEW

### 2.1 Increase of Research in Improving Vehicle Safety Features.

For the past few years, automotive industries are more focus on producing powerful engine that can increase the power and the speed of a car. Many researches and studies have been done in order to achieve their vision. However, they are neglecting the side effect of having a greater engine in a car, which is the safety. Providing the powerful engine in the car not only increase the speed of a car but also increase the possibility of having a collision or accident. As a result of the 'imbalance' automotive improvement, the accidents rate is increase globally. Nowadays, car manufacturers have realize this issue and have played their parts in overcome this problem. New cars not only have greater power but also better safety features. For instance, the invention on auto cruise control, airbag system, Anti-lock Braking System (ABS) and money others. Nevertheless, the accident rate does not decrease as expected and yet, it is still increasing from year to year. Studies have been done on this matter and it suggest that providing the driver with as many safety features as possible does not ensure the accident avoidance unless the technologies are used. Therefore, intelligent system which can integrate all the technologies and an 'communicate' with the driver is a best solution in this matter. Lately, many parties have joined the effort of inventing such system. The next page shows the examples of the studies and invented intelligent system. [1] [2]

### 2.1.1 e-Safety System [3]

eSafety systems - formally called Intelligent Vehicle Safety Systems (IVSS) are new automotive systems combining mechanical, microelectric, communication and information technology. They create superior safety through active technology. eSafety systems contribute to safety on roads by preventing vehicle collisions and consequently helping to reduce injuries and deaths on the roads.

Below you can find information regarding a number of *e*Safety systems - vehicle based and infrastructure based systems. These can be divided into active and passive safety applications. Passive safety features help people stay alive and uninjured in a crash, while active safety features help drivers avoid accidents.

### 2.1.1.1 Adaptive Brake Lights

Triggered by the strengths of brake activation the rear brake lights are illuminated in different kinds to indicate emergency braking maneuvers to the following vehicles.

#### 2.1.1.2 Automatic Headlight Activation

When activated, the system switches on the headlights automatically when major environmental conditions for the use of headlights are present. The system detects the darkness and the light conditions in the environment.

#### 2.1.1.3 Driver Condition Monitoring

The system monitors the condition of the driver. Discussed parameters today are drowsiness, distraction, and inattention.

### 2.1.1.4 Dynamic Control Systems

Active Front Steering: The AFS allows - electronically controlled -a variable steering transmission and steering force support. Two different inputs overlap, the steering angle from the steering wheel and a correction angle given by a controller through a special gearbox.

**Electronic Stability Control (ESC):** Stabilises the vehicle under all driving conditions and driving situations within the physical limits. Helps to stabilise the vehicle and prevent skidding when cornering or driving off through active brake intervention on one or more wheels and intelligent engine torque management.

Active Body Control (ABC): Active damping and suspension system minimising car body roll and pitch motion, adjusting ground clearance according to speed, allowing for a two stage ride height including loadindependent all-round self-levelling.

### 2.1.1.5 Lane Departure Warning

Warning given to the driver in order to avoid leaving the lane unintentionally. Video image processing is the most important technology.

### 2.1.1.6 Obstacle& Collision Warning

System detects obstacles and gives warnings when collision is imminent. Current solutions with limited performance are a separate feature of Adaptive Cruise Control systems, which use information obtained from radar sensors to give visual and acoustic warnings. Future systems will use long range/near range radar sensors or LIDAR and video image processing.

### 2.1.2 Cooperative Intersection Collision Avoidance Systems (CICAS) [4]

In 2003, more than 9,000 Americans died and roughly 1.5 million Americans were injured in intersection related crashes. Intersection collision avoidance systems can help save lives by preventing these crashes. Through the Cooperative Intersection Collision Avoidance Systems initiative, the USDOT is working in partnership with the automotive manufacturers and State and local departments of transportation to pursue an optimized combination of autonomous-vehicle, autonomousinfrastructure and cooperative communication systems that potentially address the full set of intersection crash problems.

### 2.1.2.1 CICAS Overview

Intelligent intersection systems offer a significant opportunity to improve safety by enhancing driver decision-making at intersections that will help drivers avoid crashes. Intersection collision avoidance systems use both vehicle-based and infrastructure-based technologies to help drivers approaching an intersection understand the state of activities within that intersection. Cooperative intersection collision avoidance systems (CICAS) have the potential to warn drivers about likely violations of traffic control devices and to help them maneuver through cross traffic. Eventually, CICAS may also inform other drivers (i.e., potential victims) about impending violations as well as identify pedestrians and cyclists within an intersection. CICAS consists of:

- Vehicle-based technologies and systems—sensors, processors, and driver interfaces within each vehicle.

- Infrastructure-based technologies and systems—roadside sensors and processors to detect vehicles and identify hazards and signal systems, messaging signs, and/or other interfaces to communicate various warnings to drivers.

- Communications systems—dedicated short-range communications (DSRC) to communicate warnings and data between the infrastructure and equipped vehicles.

### 2.2 Programming Language Used for the Project [5]

For this project, the language used is Verilog. Verilog is a hardware description language (HDL) used to describe a digital system: for example, a network switches, a microprocessor or a memory or a simple flip-flop. It means that, by using a HDL, one can describe any digital hardware at any level.

Figure 1 : Example of Verilog coding

One can describe a simple flip flop as that in Figure 1, as well as a complicated design having one million gates. Verilog is one of the HDL languages available in the industry for hardware designing. It allows us to design a digital design at Behavioral Level, Register Transfer Level (RTL), gate level and switch level. Verilog allows hardware designers to express their designs with behavioral constructs, deferring the details of implementation to a later stage in the final design.

### 2.2.1 Design Styles

Verilog, like any other hardware description language, permits a design in either Bottom-up or Top-down approach.

### 2.2.1.1 Bottom-Up Design

The traditional method of electronic design is bottom-up. Each design is performed at the gate-level using the standard gates. With the increasing complexity of new designs this approach is nearly impossible to maintain. New systems consist of ASIC or microprocessors with a complexity of thousands of transistors. These traditional bottom-up designs have to give way to new structural, hierarchical design methods. Without these new practices it would be impossible to handle the new complexity.

### 2.2.1.2 Top-Down Design

The desired design-style of all designers is the top-down approach. A real top-down design allows early testing, easy change of different technologies, a structured system design and offers many other advantages. But it is very difficult to follow a pure top-down design. Due to this fact most designs are a mix of both methods, implementing some key elements of both design styles.

## CHAPTER 3 METHODOLOGY

### 3.1 Introduction

Figure 2 : Process flow of the project

Figure above shows the entire process flow of the project. There are four major steps in completing this project. The first two steps is generally the understanding and designing of the system. These steps are crucial since they will determine the type of the system. Thorough understanding and analysis is necessary. For the last two steps, they are more on the system development; develop the coding and simulation of the coding. On the next page, each of the steps will be discussed in detail.

### 3.1.1 Understanding on how the system works

Understanding the whole system is the fundamental of this project. The simulation of the system should base on the real and actual conditions so that it can be used as a guide or reference for future development of the system. The understanding includes the location of the sensors, data processing and concept of physics.

### 3.1.2 Planning the process flow of the system

Upon understanding how the system works, the process flow of the system is determined based on the specification and requirements need. The flow includes all the process from the beginning until the end considering all possibilities.

### 3.1.3 Develop behavioral code

From the process flow, the module of the system is determined in order to develop the behavioral code. Dividing the system into different module will make the system easier to develop/trouble shoot or to be improved in the future.

### 3.1.4 Simulation

Completing the behavioral code, the simulation of the system can be done. The results from the simulation will be analyzed and correction or improvement can be made should there are any changes required.

## CHAPTER 4 RESULT AND DISCUSSION

### 4.1 Understanding on how the system works

Figure 3 shows the probable locations of the sensors and actuators. Figure 4 shows the connections between them and the components of the Intelligence Processing Unit (IPU). Most of the times the data produced or accepted by each of the sensors and actuators are not in the same format or standard. The data can be in analog format (voltage or current levels) or even in digital format. That is why the sensors are being connected to the processor's Data Acquisition Module (DAM) that will process the data before it can be used in data processing.

IPU will accept data from the sensor through DAM and process them immediately. IPU is programmed in a loop that processes all the sensors' inputs and translates them into the vehicle running state. The state will then be compared to safe condition data stored in the IPU. Any irregularities will trigger the driver's alarm system. Should there are no response taken by the driver, the IPU will then execute the Antilock Brake System (ABS) automatically.

Figure 3 : Conceptual diagram

Figure 4 : System block diagram

#### 4.2 Process flow of the system

Figure 5 : Process flow of the system

Figure 5 shows the process flow of the Car's Object Detection and Avoidance Simulation using Verilog (CODA). It is very important that this algorithm is tested thoroughly before being used. All the possible conditions will be included in the test program. The Central Electronics Processor or previously described as IPU is the key towards the success of this project. The processor must be able to interpret the data accurately before making the split-microsecond decision. The robustness and the accuracy of the system come directly from the performance of the processor. All the logics must be properly defined and tested. Decision of engaging the ABS is very complex and needs a lot of verification process. It would not be easy to really determine and command a car that loses it's control and stability.

Figure 6 : Modules of the System

Figure 6 shows the entire module of the system which are determined base on the process flow. The modules consist of three module which will be explained in the details :

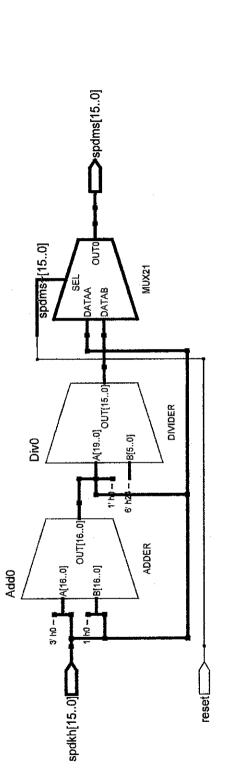

### 4.3.1 Speed Converter Module

The information of the vehicle's speed which is fed from the speed sensor is in km/h. This parameter will be converted to m/s in order to standardize the measurement parameters. The output of the module (in m/s) will then be fed to the next module; time to collision (ttc) module.

Generally, the speed converter module will start to convert the input speed measurement (in km/h) into m/s when reset = 1 and clock cycle is at positive edge (please refer to the truth table in the next page). Speed in km/h will be converted to m/s using the formula :

### 4.3.1.1 Truth table for Speed Converter Module

| Reset | Clock         | spdms         | spdkh |

|-------|---------------|---------------|-------|

| 0     | Positive edge | 0             | 0     |

| 0     | Negative edge | 0             | 0     |

| 1     | Positive edge | spdkh * 10/36 | input |

| 1     | Negative edge | 0             | 0     |

|       |               | 1             |       |

Table 1 : Truth table of Speed Converter Module

### 4.3.2 Time to Collision (ttc) Module

Combining the 'converted' speed measurement (form speed converter module) and the input from the object relative distance sensor, anticipated time of collision to happen is calculated based on the formula:

time to collision = distance / speed

For the Time to Collision analysis, the following condition is followed:

Maximum distance = 10m Maximum speed = 200 km/h (55.56 m/s)

From the calculation of time to collision (ttc) using formula above, the ttc will be categorized into five different category, which will taken different type of reaction for the next module (Response to be taken Module). The categories are :

| Category | ttc (sec)   |

|----------|-------------|

| A        | 0-0.10      |

| В        | 0.10 - 0.20 |

| С        | 0.20 - 0.30 |

| D        | 0.30-0.40   |

| E        | 0.40 - 0.90 |

Table 2 : Category based on time to collision value

| Speed /        | 9-10.     | è n  | 7 0  | 6-7  | 5        | 4-5  |      |      | 1 2  |      |

|----------------|-----------|------|------|------|----------|------|------|------|------|------|

| Distance       | 2-103<br> |      | / 0  |      | 2-0<br>- |      |      |      |      |      |

| -36.41755.56   | 0.18      | 0.16 | 0.14 | 0.13 | 0.11     | 0.09 | 0.07 | 0.05 | 0.04 | 0.02 |

|                | 0.28      | 0.25 | 0.22 | 0.19 | 0.17     | 0.14 | 0.11 | 0.08 | 0.06 | 0.03 |

| 16.67-25940    | 0.40      | 0.36 | 0.32 | 0.28 | 0.24     | 0.20 | 0.16 | 0.12 | 0.08 | 0.04 |

| 41.11 = 10.673 | 0.60      | 0:54 | 0.48 | 0.42 | 0.36     | 0.30 | 0.24 | 0.18 | 0.12 | 0.06 |

| 0-11:17        | 0.90      | 0.81 | 0.72 | 0.63 | 0.54     | 0.45 | 0.36 | 0.27 | 0.18 | 0.09 |

Table 3 : Summary of time to collision with the respected category

Category A Category B Category C Category D

Category E

### 4.3.3 Response to be taken

There are two types of action to be taken in this project which are the Antilock Braking System (ABS) and the driver alert system. These responses will be only initiated if there are no responses or action taken by the driver. If there are any action or reaction by the driver, the system will be disengaged until the next 'collision to be' moment.

The action of the ABS is categorized into five categories which are differs in the force to be applied onto the brake. The category is based on the time to collision category determined from the previous module (time to collision module).

Practically, a set of actuator system will be implemented on the braking system and the response to be taken determined by the system shall be translated in term of voltage values. The actuator response will be based on the output voltage values.

### 4.4 Simulation

The following are the simulation result of each module. The test values for each module are as shown in the table before each of the simulation figure:

### 4.4.1 Simulation result of Speed Converter Module

| spdkh | spdms |

|-------|-------|

| 50    | 13.89 |

| 90    | 25.00 |

| 120   | 33.33 |

Table 4 : Test set values for the Speed Converter Module

| Har    | ter Time Bac      |                 | 420.0 nz           | 4) Pointer           | 2465 na          | Interval:      | -173.5 ne  | Stat         | ana an | End                       |               |

|--------|-------------------|-----------------|--------------------|----------------------|------------------|----------------|------------|--------------|-----------------------------------------|---------------------------|---------------|

|        | Name              | Val.e.<br>420.( | 0.ps 40.p re       | 80.pn#               | 120,0 ms 160,0 m | ≠ 200,0 r      | s 240,0 ns | 280,0 ma 320 | ļūns 350,0ms                            | 400,0 ns 440,<br>420,0 ns | ມີຕຣ 430,0 ຕຣ |

| 10 E 4 | reset<br>El spökh | U<br>U          | F - F              |                      |                  | <b>[</b>       |            | ]<br>p       | 1<br>X125                               |                           | 0             |

| 2      | a sparse          | 0               |                    |                      | <u> </u>         | <u>x esses</u> |            | 5            |                                         | K                         | 0             |

|        |                   |                 | Negative Clock Cyr | e Poslive Clock Cycl | •                |                | 1.0°<br>   |              |                                         |                           |               |

Figure 7: Simulation of Speed Converter Module

The waveform in blue shows the value of the input for the speed converter module which is the speed in km/h (spdkh). On the other hand, the waveform in yellow and red colour indicates the output of the module which is the converted measurement of the speed from km/h into speed in m/s (spdms). Based on the module design, the input, will be converted into spdms only when the reset if at the positive edge, otherwise, the spdkh will be converted.

Based on Figure 9, when the reset is at the positive edge, the output waveform of spdms shows the expected value of the converted spdkh. In this project, only integer value is taken into consideration since it is easier to design and troubleshoot. During the negative cycle of the, the spdms value is the same as the spdkh value.

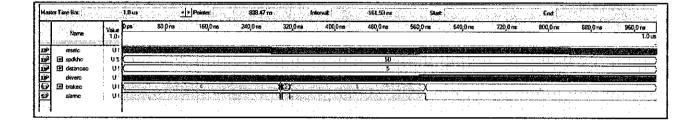

### 4.4.2 Simulation result of Time to Collision Module

| Table 5 : Test                                                                     | spdms                                          | distance                                                                                                        | ttc                                             | category          | set values for                                                                                                  |

|------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|

| the Time to                                                                        | 10                                             | 5                                                                                                               | 0.50                                            | A (1)             | Collision                                                                                                       |

| the 1 tme to                                                                       | 30                                             | 5                                                                                                               | 0.17                                            | B (4)             | Consion                                                                                                         |

| Module                                                                             | 50                                             | 5                                                                                                               | 0.10                                            | C (5)             |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

| an un an ann an t-an -an -an -an - <u>an -an -an -an -an -an -an -an -an -an -</u> | mayaaniya ga ka <u>ayaaya k</u> asarin maninin | n the start of the first start of the start start of the start start of the start start of the start start of t | n - Maria and an an ann ann ann ann ann ann ann |                   | u gene um a montre en anticipitado de la constanción de la constanción de la constanción de la constanción de l |

| 100 m                                                                              | <u>≺(•</u> Pointer.)                           | 7aa                                                                                                             |                                                 | Stat              | End                                                                                                             |

|                                                                                    |                                                |                                                                                                                 |                                                 |                   |                                                                                                                 |

| Annas Valus Ope 80,0 ms                                                            | 160,0ns 240,0ns                                | 320,0mi 400,0mi                                                                                                 | 480jilins 560jilins                             | 540,0 ns 720,0 ns | 830,0 ns 880,0 ns 950,                                                                                          |

|                                                                                    | 150,0 ms 240,0 ms                              |                                                                                                                 | 420,16ns 560,0ns                                | 540,0 ns 720,0 ns | 820,0ns 680,0ns 950,                                                                                            |

Figure 8 : Simulation of Time to Collision Module

The time to collision (ttc) is calculated based on the formula :

### ttc = distance/speed

In this module, once the ttc is calculated, it will be categorized into five different categories based on ttc value. The smaller the value of ttc the higher the category will be. For instance, in Table 5, the value shows the decreases value of ttc but increases value of the category.

Based on the waveform in Figure 10, the ttc shows the correct category as stated in Table 5. There are some delay in the process of determine the category of the ttc. Referring to the orange waveform, there is lagging between each of the new set of input. This is because of the propagation delay occurred within the module.

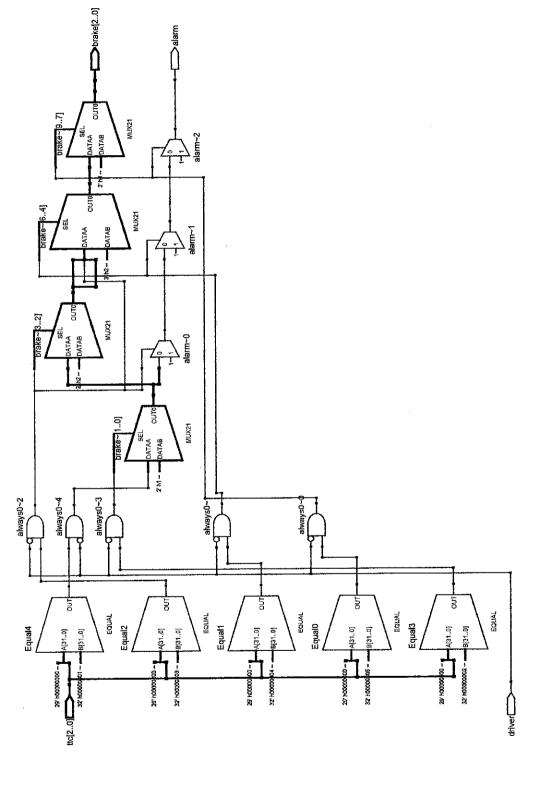

### 4.4.3 Simulation result of Action Taken Module

| driver | ttc | brake | alarm |

|--------|-----|-------|-------|

| 0      | 1   | 5     | 1     |

| 1      | 1   | 0     | 0     |

| 0      | 2   | 4     | 1     |

| 1      | 2   | 0     | 0     |

Table 6 : Test set values for the Action Taken Module

| The factor of the | Value Dos |                   |                       |             |        |              |    |               |                                                                                                                 | 950,     |          |                    |  |

|-------------------|-----------|-------------------|-----------------------|-------------|--------|--------------|----|---------------|-----------------------------------------------------------------------------------------------------------------|----------|----------|--------------------|--|

| Name              | 990.0     |                   |                       |             |        |              |    |               |                                                                                                                 |          |          |                    |  |

| Be driver         | 01        |                   | 1                     |             | 1      | ſ            | l. | <u></u>       |                                                                                                                 | r        |          |                    |  |

| P H Ho<br>D brake | 0         | 1 4               | × X                   |             | X      | 11.4.4.4.4   | X  | na satabili 🔐 | <u> </u>                                                                                                        | <u> </u> | X        | 0                  |  |

| Diske             | : n:}⊂    | 5 <b>\$</b> 12 12 | X                     | <u>x x</u>  | 0      | <u>X X X</u> | 0  |               | (                                                                                                               | <u> </u> | <u> </u> | <u> </u>           |  |

| atam.             | 1 u -     | 1 1 1 L           | <b>T</b> e 2 x 19 è é | 00000000000 | 化甘油 机活 | 2000000000   |    | en percula a  | a generation de la companya de la co |          | <u></u>  | <u> 1111 - 111</u> |  |

### Figure 9 : Simulation of Action Taken Module

Action to be taken will be initiated if only there is no response form the driver. In this condition, the system will overtake the driver in order to avoid the car to be collided. Based on Table 6, it shown that whenever there is any action taken by the driver (which is indicate as in state "1"), both of the output will be at "0" state, which means the system did not overtake the driver role.

Referring to the waveform above, if the driver state is "0", the output; brake will be varies and the output alarm will be "1". The brake output varies depends on the category of time to collision (ttc) obtained from the previous module (time to collision module). The higher the category of ttc the smaller the brake value. The brake category determine of how much forces to be applied onto the brake (which will be carried out by a set of actuator).

## 4.4.4 Simulation result of the overall system : Car's Object Detection and Avoidance (CODA)

| reset | spdkh | distance | driver | brake | alarm |

|-------|-------|----------|--------|-------|-------|

| 1     | 50    | - 5      | 0      | 1     | 1     |

| 0     | 50    | 5        | 0      | 4     | 1     |

| 1     | 50    | 5        | 1      | 0     | 0     |

| 0     | 50    | 5        | 1      | 0     | 0     |

Table 7 : Test set values for CODA

### Figure 10 : Simulation of CODA

Figure 12 shows the simulation result of the completed module of the Car's Object Detection and Avoidance system. With speed in km/h (spdkh) and the distance to be constant, driver action will determine the system response.

As shown in above figure, the waveform in blue colour shows that the driving control is overtake by the system whilst the waveform in yellow colour shows no response by the system. This is because of the driver action at particular condition. It shows that if the driver is not taking any action, then only the system will play it's role.

The reset value will only determined whether the spdkh will be converted into spdms. This operation occur within the speed converter module, where in this 'big picture' of the overall module, the operation is not shown.

## CHAPTER 5 CONCLUSION AND RECOMMENDATION

### 5.1 Conclusion

The objective of the project which is to simulate the Car's Object Detection and Avoidance is achieved. The designated system however is a very basic system which does not consider the actual and real life situation. The idea is not to develop a practical system but more to get familiar with the process and procedure on how to design a system which can be implemented on an intelligent circuit (IC). Further improvement is needed in order to get this project to be practical and marketable.

### 5.2 Recommendation

It is recommended that the data and information used in the design process to be based on the reliable and accurate. In this project, all the data and information used in the design process is generally based on assumption which is not good if the system is design for marketable purpose.

### REFERENCES

- [1] Wikipedia, The Free Encyclopedia, "Accident Statistic" (26/8/2006) <u>http://en.wikipedia.org/wiki/Road\_accident\_statistics\_on\_a\_model-by-model\_basis</u>

- [2] Wikipedia, The Free Encyclopedia, "Car Accident" (26/8/2006) http://en.wikipedia.org/wiki/Car\_accident

- [3] eSafety Support, European Commission funded project coordinated by ERTICO, (13/1/07) <u>http://www.esafetysupport.org/en/learn\_about\_esafety\_systems/esafety\_systems.htm</u>

- [4] United States Department of Transportation Intelligent Transport System, Cooperative Intersection Collision Avoidance System, (13/1/07) http://www.its.dot.gov/cicas/index.htm

- [5] Verilog Introduction for Digital Design, Dr Hyde of <u>Bucknell</u> University, Lewisburg PA, (18/9/07) <u>http://www.see.ed.ac.uk/~gerard/Teach/Verilog/index.html?http://oldeee.see.e</u> <u>d.ac.uk/~gerard/Teach/Verilog/index.html</u>

- [6] Emerald System, IC Design Services/EDA & PCB Design Tools, Digital Design Training, Universiti Teknologi PETRONAS Training Material.

### **APPENDICES**

# APPENDIX A

```

le speedconverter (reset,spdkh,spdms);

```

```

t reset;

t [15:0]spdkh;

ut [15:0]spdms;

[15:0]spdms;

```

```

meter a = 10;

meter b = 36;

:d is converted only if clock and reset = 1

```

```

ys @(spdkh or reset)

if (reset == 1)

spdms = (spdkh * a)/b;

else

spdms = spdkh;

```

.odule

**RTL Viewer**

Page 1 of 1

| Resource                                    | Usage |

|---------------------------------------------|-------|

| Total logic elements                        | 264   |

| - Combinational with no register            | 264   |

| Register only                               | 0     |

| Combinational with a register               | 0     |

|                                             |       |

| Logic element usage by number of LUT inputs |       |

| 4 input functions                           | 39    |

| - 3 input functions                         | 84    |

| 2 input functions                           | 83    |

| - 1 input functions                         | 58    |

| 0 input functions                           | 0     |

| Combinational cells for routing             | 0     |

|                                             |       |

| Logic elements by mode                      |       |

| normal mode                                 | 160   |

| arithmetic mode                             | 104   |

| qfbk mode                                   | 0     |

| register cascade mode                       | 0     |

| synchronous clear/load mode                 | 0     |

| asynchronous clear/load mode                | 0     |

|                                             |       |

| Total registers                             | 0     |

| Total logic cells in carry chains           | 134   |

| I/O pins                                    | 33    |

| Maximum fan-out node                        | reset |

| Maximum fan-out                             | 16    |

| Total fan-out                               | 648   |

| Average fan-out                             | 2.18  |

Project: speedconverter

| Option                                                                         | Setting | Default Value |

|--------------------------------------------------------------------------------|---------|---------------|

| Use smart compilation                                                          |         | Off           |

| Generate Serial Vector Format File (.svf) for Target Device                    | Off     | Off           |

| Generate a JEDEC STAPL Format File (.jam) for Target Device                    | Off     | Off           |

| Generate an uncompressed Jam STAPL Byte Code 2.0 File (.jbc) for Target Device | Off     | Off           |

| Generate a compressed Jam STAPL Byte Code 2.0 File (.jbc) for Target Device    | On      | On            |

| Compression mode                                                               | Off     | Off           |

| Clock source for configuration device                                          |         | Internal      |

| Clock frequency of the configuration device                                    | 10 MHZ  | 10 MHz        |

| Divide clock frequency by                                                      | 1       | 1             |

| JTAG user code for target device                                               |         | Fffffff       |

| Auto user code                                                                 | Off     | Off           |

| Use configuration device                                                       | On      | On            |

| Configuration device                                                           | Auto    | Auto          |

| JTAG user code for configuration device                                        |         | Fffffff       |

| Configuration device auto user code                                            | Off     | Off           |

| Auto-increment JTAG user code for multiple configuration devices               | On      | On            |

| Disable CONF_DONE and nSTATUS pull-ups on configuration device                 | Off     | Off           |

| Generate Tabular Text File (.ttf) For Target Device                            | Off     | Off           |

| Generate Raw Binary File (.rbf) For Target Device                              | Off     | Off           |

| Generate Hexadecimal (Intel-Format) Output File (.hexout) for Target Device    | Off     | Off           |

| Hexadecimal Output File start address                                          | 0       | 0             |

| Hexadecimal Output File count direction                                        | Up      | Up            |

| Release clears before tri-states                                               | Off     | Off           |

| Auto-restart configuration after error                                         | On      | On            |

Page 1 of

.

Fitter Settings

| AUTO           Timing Optimization Level         Off           Effort Multiplier         1.0           Constraining         Off           Filting         Normal compilation           Constraining         Off           One Fitting Attempt         Off           One Fitting Attempt         Off           Constraining         Off           One Fitting Attempt         Off           Automatically         Automatically           Bus-Hold Circuitry         Off           Ital Placement Seed         Off           Ital                                                                                                                                                                                                            | Option                                            | Setting                        | Default Value                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|--------------------------------|

| Use smart compilation         Off         Off         Off           Router Timing Optimization Level         Normal         Normal         Normal           Router Timing Optimization Level         10         10         10           Router Timing Optimization Level         10         10         10           Router Timing Optimization Level         10         10         10           Optimize Hold Timing         0ff         0ff         0ff           Optimize Fast-Corner Timing         0ff         0ff         0ff           Optimize IOC Register Placement for Timing         0ff         0ff         0ff           Optimize IOC Register Placement for Timing         0ff         Automatically         Automatically           Dimit to One Fitting Attempt         Automatically         Automatically         Automatically           Fittar Aggressive Routability Optimizations         Automatically         Automatically         Off           Slow Slew Rate         Off         Off         Off         Of                                                                        | Device                                            |                                |                                |

| Router Timing Optimization Level         Normal         Normal           Placement Effort Mutippler         1.0         1.0           Detwore Effort Mutippler         1.0         1.0           Detwore Effort Mutippler         0 ff         1.0           Detwore Effort Mutippler         0 Paths and Minnum TPD Paths         1.0           Detwore Effort Mutippler         0 Paths and Minnum TPD Paths         0 Paths           Detwore Effort Mutippler         0 Paths         0 Paths         0 Paths           Detwore Effort Mutippler         0 Paths         0 Paths         0 Paths           Detwore IOC Register Placement for Timing         0 Path         0 Paths         0 Paths           Detwore IOC Register Placement for Timing         0 n         0 n         0 n           Detwore IOC Register Placement for Timing         0 n         0 n         0 n           Detwore IOC Register Placement for Timing         0 n         0 n         0 n           Detwore IOC Register Placement Seed         0 n         0 n         0 n           Slow Slew Rate         0 n         0 n         0 n         0 n           Slow Slew Rate         0 n         0 n         0 n         0 n           Slow Slew Rate         0 n         0 n         0 n                                                          | Use smart compilation                             |                                | Off                            |

| Placement Effort Multiplier         1.0         1.0           Router Effort Multiplier         1.0         1.0           Router Effort Multiplier         1.0         1.0           Router Effort Multiplier         0.0         1.0           Optimize Hold Timing         0         0           Optimize Filter Multiplier         0.0         0           Optimize Filter Timing         0         0           Optimize IOC Register Placement for Timing         0         0           Dimit to One Fitting Attempt         0         0           Fitter Aggressive Routability Optimizations         Automatically         Automatically           Slow Slew Rate         0ff         0         0           Nowak Pull-Up Resistor         0ff         0         0           Multi Placement Seed         1         1         1           Slow Slew Rate         0         0         0         0           Veak Pull-Up Resistor         0         0         0         0           Auto Bus-Hold Circuitry         0         0         0         0           Auto Bolas Nuckee         0         0         0         0           Mult Delay Veak         0         0         0                                                                                                                                                       | Router Timing Optimization Level                  | Normal                         | Normal                         |

| Router Effort Mutriplier         1.0         1.0           Optimize Hold Timing         IO Paths and Minum TPD Paths[O Paths and Minum TPD Paths]         Off         Automatically         Off         Off <td>Placement Effort Multiplier</td> <td></td> <td>1.0</td> | Placement Effort Multiplier                       |                                | 1.0                            |

| Optimize Hold Timing         IO Paths and Minimum TPD Paths O Paths and Minimum TPD Paths           Optimize Tast-Corner Timing         Off                                                                                                           | Router Effort Multiplier                          | 1.0                            | 1.0                            |

| Optimize Fast-Corner Timing         Off         Off           Optimize Timing         Normal compilation         Normal compilation         Normal compilation           Optimize IOC Register Placement for Timing         Of         Normal compilation         On           Limit to One Fitting Attempt         Attempt         Automatically         Automatically         Automatically           Fitter Initial Placement Seed         1         1         1         1           Slow Slew Rate         Off         Off         Off         Off           PCI I/O         Off         Off         Off         Off           Auto Blas-Hold Circuitry         Off         Off         Off           Auto Delay Chains         Off         Off         Off           Auto Blas-Hold Circuitry         Off         Off         Off           Auto Bela                                                                                                                                      | Optimize Hold Timing                              | IO Paths and Minimum TPD Paths | IO Paths and Minimum TPD Paths |

| mal compilation<br>omatically<br>omatically<br>o<br>o<br>o<br>o<br>fit<br>mal<br>o<br>o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Optimize Fast-Corner Timing                       | Off                            | Off                            |

| omatically<br>omatically<br>o<br>Fit<br>mal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Optimize Timing                                   |                                | Normal compilation             |

| omatically<br>omatically<br>o Fit<br>mal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Optimize IOC Register Placement for Timing</b> |                                | O                              |

| omatically<br>omatically<br>o<br>o<br>o<br>fit<br>mai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                | Off                            |

| omatically<br>o<br>o<br>Fit<br>mai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Final Placement Optimizations                     | Automatically                  | Automatically                  |

| o<br>o Fit<br>o o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fitter Aggressive Routability Optimizations       |                                | Automatically                  |

| o<br>Fit<br>mai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fitter Initial Placement Seed                     |                                |                                |

| o<br>Fit<br>o<br>o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Slow Slew Rate                                    |                                | Off                            |

| o Fit<br>mai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PCI I/O                                           |                                | Off                            |

| o<br>o Fit<br>mai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Weak Pull-Up Resistor                             |                                | Off                            |

| o<br>o Fit<br>mai<br>o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Enable Bus-Hold Circuitry                         |                                | Off                            |

| o<br>o Fit<br>mai<br>o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Contro                                            |                                | Off                            |

| o Fit<br>bo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Auto Packed Registers – Stratix/Stratix GX        |                                | Auto                           |