# DIRECT DIGITAL CONTROL OF PERMANENT MAGNET BLDC MOTOR FOR AIR CONDITIONING

By

# HARYATTIE BINTI AZIZI

## FINAL YEAR PROJECT REPORT

Submitted to the Department of Electrical & Electronics Engineering in Partial Fulfillment of the Requirements for the Degree Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

> Universiti Teknologi Petronas Bandar Seri Iskandar 31750 Tronoh Perak Darul Ridzuan

© Copyright 2007 by Haryattie binti Azizi, 2007

# **CERTIFICATION OF APPROVAL**

# DIRECT DIGITAL CONTROL OF PERMANENT MAGNET BLDC MOTOR FOR AIR CONDITIONING

by

Haryattie binti Azizi

A project dissertation submitted to the Electrical & Electronics Engineering Programme Universiti Teknologi PETRONAS in partial fulfilment of the requirement for the Bachelor of Engineering (Hons) (Electrical & Electronics Engineering)

Approved:

lac

Dr. K. S. Rama Rao Project Supervisor

UNIVERSITI TEKNOLOGI PETRONAS TRONOH, PERAK

June 2007

# **CERTIFICATION OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this project, that the original work is my own except as specified in the references and acknowledgements, and that the original work contained herein have not been undertaken or done by unspecified sources or persons.

Haryattie binti Azizi

# ACKNOWLEDGEMENTS

Firstly, I would like to express my gratitude to Allah S.W.T for His grace to enable completion of the final year project. With strength and knowledge that blessed by Him, I was able to carry out and accomplish.

My heartfelt thank goes too my supervisor, Dr. K.S. Rama Rao for his guidance and patience that lead to accomplishment of this project. Under his supervision, I encountered a lot of new things. Thanks to him, the project is very resourceful and easy to understand. His sharing of knowledge, kindness and patience will always be appreciated.

Next, thanks to my family and friends for willingly to understand my needs in the making of the projects. From the bottom of my heart, I would like to thank them for being very supportive and sharing word of wisdom together.

Not to forget Vivian Huyen from Lin Engineering who always being helpful during my projects. Thanks to her, I understand better the concept of BLDC motor.

Lastly to all lecturers, staffs and students whose names are not mentioned here but actively being helpful with guidance, directly or indirectly, thanks a lot. Without the help that I got from everyone, this project would be a failure. Thank You.

# ABSTRACT

This is a design project which to design a direct digital control of permanent magnet BLDC motor for air conditioning. Mainly the task of this to developed a control to the speed of BLDC motor that will determine the speed of compressor inside in an air-conditioner. The project is divided into two main tasks; the simulation part and circuitry part. This report will delivered results, discussion and feedbacks of the both parts that had been handled. The simulation is build inside MATLAB/SIMULINK while the circuitry part is built by using equipments of Lab-Volt. It composed from blocks that are mainly based on calculation or theoretical value. So it is completely logical blocks and shall not interface with other Power Electronic block set components inside MATLAB. From here the author learns relationship between Sensorless BLDC motor and BLDC motor with Hall Sensor. In circuitry part, the IGBT inverter by supplying PWM control signals. From here the author learns that the output voltage depends on switching process and the DC input. Due to lots of advantages deliver by BLDC motor, this project brings a lot of benefit.

# **TABLE OF CONTENTS**

| CERTIFICATIONiii                         |

|------------------------------------------|

| ABSTRACTvi                               |

| LIST OF TABLESix                         |

| LIST OF FIGURESx                         |

| LIST OF ABBREVIATIONSxii                 |

| CHAPTER 1 INTRODUCTION                   |

| 1.1 Background of Project1               |

| 1.2 Problem Statement1                   |

| 1.3 Objectives2                          |

| 1.4 Project Planning2                    |

| CHAPTER 2 LITERATURE REVIEW AND THEORY   |

| 2.1 Brushless DC Motor                   |

| 2.2 Simulation Tools                     |

| 2.3 Pulse Width Modulation Inverter      |

| 2.3.1 Operation of PWM Inverter          |

| CHAPTER 3 METHODOLOGY                    |

| 3.1 Flowchart                            |

| 3.2 Tools                                |

| CHAPTER 4 RESULTS AND DISCUSSION         |

| 4.1 Simulation with Matlab/Simulink12    |

| 4.1.1 The mybldc block                   |

| 4.1.2 The estimation block               |

| 4.1.3 Zero crossing block                |

| 4.1.4 IC and 120 deg trigger blocks      |

| 4.1.5 The Controller block               |

| 4.1.6 The All Phase block                |

| 4.2 Results and Discussion of simulation |

| 4.2.1 Stator phase currents              |

| 4.2.2 Rotor speed                        |

| 4.2.3 Voltage applied to BLDC motor      |

| 4.2.4 Back Electromotive Force           |

| 4.2.5 Currents after controller                                                   |

|-----------------------------------------------------------------------------------|

| 4.2.6 Zero crossing                                                               |

| 4.3 Construct the digital controller and power circuits                           |

| 4.3.1 Designing boost converter                                                   |

| 4.3.2 Experimental test on BLDC motor                                             |

| 4.3.3 Test BLDC motor without Hall Sensor feedback to the Lab-<br>Volt controller |

| 4.3.4 Test BLDC motor while Hall Sensor are attached to the designed controller   |

| 4.3.4.1 Designed controller hardware                                              |

| 4.3.5 Test BLDC motor with the designed controller                                |

| 4.3.6 Correction to the controller                                                |

| CHAPTER 5 CONCLUSION AND RECOMMENDATION                                           |

| REFERENCES                                                                        |

| Appendix A Gantt Chart                                                            |

| Appendix B BLDC Motor Specification                                               |

| Appendix C Results of Simulation                                                  |

| Appendix D coding for microcontroller                                             |

| Appendix E Datasheets                                                             |

.

# LIST OF TABLES

| Table 1 Design parameters |  |

|---------------------------|--|

| Table 2 Results of test   |  |

# LIST OF FIGURES

| Figure 1 BLDC drive system                                                                                           |

|----------------------------------------------------------------------------------------------------------------------|

| Figure 2 BLDC motor                                                                                                  |

| Figure 3 Torque-speed characteristic for BLDC motor                                                                  |

| Figure 4 Stator of BLDC motor                                                                                        |

| Figure 5 Arrangement of permanent magnet in rotor                                                                    |

| Figure 6 PWM inverter with R-L load7                                                                                 |

| Figure 7 Sine-triangle, pulse-width-modulated control waveforms, phase voltages<br>Vag and Vbg, and line voltage Vab |

| Figure 8 Flowchart 10                                                                                                |

| Figure 9 Matlab software 11                                                                                          |

| Figure 10 Lab-Volt Power Electronics Equipment                                                                       |

| Figure 11 BLDC motor simulator                                                                                       |

| Figure 12 mybldc block 13                                                                                            |

| Figure 13 Inside of mybldc block                                                                                     |

| Figure 14 my state space parameters 14                                                                               |

| Figure 15 S function parameters                                                                                      |

| Figure 16 Estimation block                                                                                           |

| Figure 17 Zero crossing block15                                                                                      |

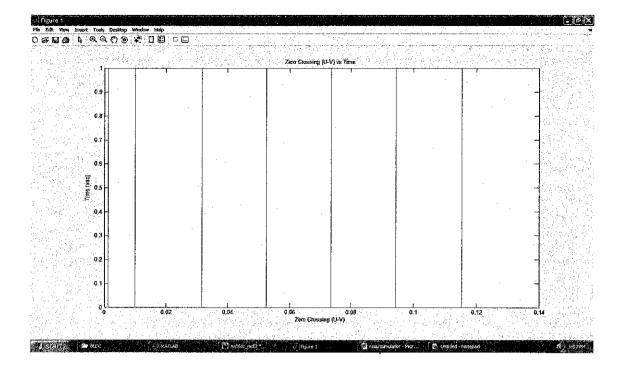

| Figure 18 Zero crossing detection for Back EMF phase U and phase V 16                                                |

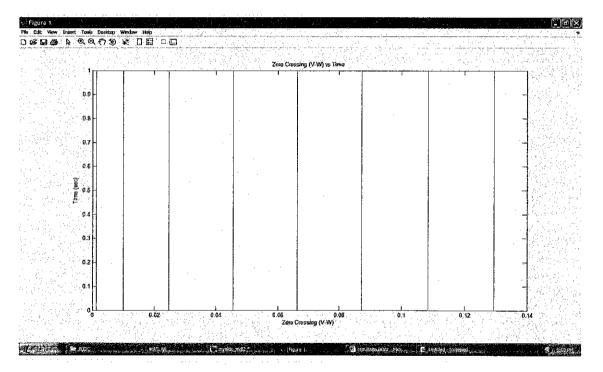

| Figure 19 Zero crossing detection for Back EMF phase V and phase W16                                                 |

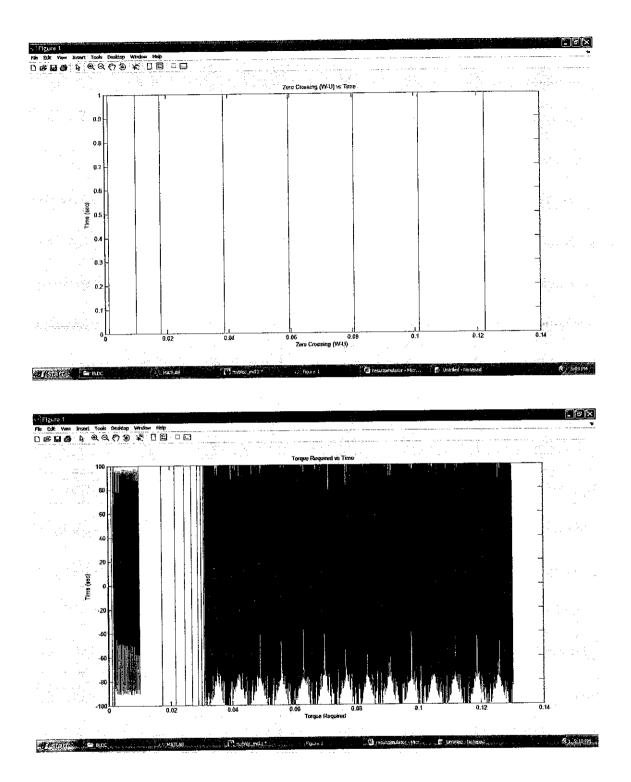

| Figure 20 Zero crossing detection for Back EMF phase U and phase W 17                                                |

| Figure 21 IC block 17                                                                                                |

| Figure 22 120 deg trigger block 17                                                                                   |

| Figure 23 Sub block of IC 18                                                                                         |

| Figure 24 Controller block                                                                                           |

| Figure 25 Reference structure of Inverter 19                                                                         |

| Figure 26 Sub system of controller block                                                                             |

| Figure 27 All Phase Block                                                                                            |

| Figure 28 Output of voltage at phase U 20                                                                            |

| Figure 29 Instantaneous currents in phase U,V and W                                                                  |

| Figure 30 Actual rotor speed                                                                                         |

|                                                                                                                      |

| Figure 31 Voltage applied to Phase U, V and W                           |             |

|-------------------------------------------------------------------------|-------------|

| Figure 32 Back EMF for Phase U, V and W                                 | 24          |

| Figure 33 Current generated after controller to Phase U, V and W        | 25          |

| Figure 34 Zero crossing to Phase U, V and W                             | 26          |

| Figure 35 Boost converter topology                                      | 27          |

| Figure 36 The switch and diode current                                  | 27          |

| Figure 37 Experimental setup                                            | 29          |

| Figure 38 Lab-Volt control unit and inverter                            | 29          |

| Figure 39 Test BLDC motor without Hall Sensor feedback to controller    |             |

| Figure 40 Chopper/Inverter control unit                                 |             |

| Figure 41 At 20% duty cycle                                             |             |

| Figure 42 At 30% duty cycle                                             |             |

| Figure 43 At 40% duty cycle                                             | 32          |

| Figure 44 At 50% duty cycle                                             |             |

| Figure 45 At 60% duty cycle                                             |             |

| Figure 46 At 80% duty cycle                                             | 34          |

| Figure 47 At 100% duty cycle                                            |             |

| Figure 48 Test BLDC motor while Hall Sensor are attached to designed co | ntroller.35 |

| Figure 49 Circuit diagram-part1                                         | 36          |

| Figure 50 Circuit diagram-part2                                         |             |

| Figure 51 Test BLDC motor with designed controller alone                |             |

| Figure 52 The correction of controller circuit                          |             |

# LIST OF ABBREVIATIONS

DDC - Direct Digital Control

AC – Alternating Current

DC - Direct Current

BLDC motor – Brushless DC Motor

PWM - Pulse Width Modulation

**EMF - Electromotive Force**

L-Inductor

C-Capacitor

# CHAPTER 1 INTRODUCTION

#### 1.1 Background of Project

BLDC abbreviation for Brushless DC motor had been widely used due to its advantages. In air conditioning, BLDC motor had been used in compressor to enable the compressor to start at high revolution speed as soon the air conditioning system is turned on. [1] This project mainly focused on the application of BLDC motor for compact and small car air conditioner.

The drive system, use Direct Digital Control or DDC as electronic control interface for BLDC motor. Under DDC, microcontroller is implemented. This system had contributed to hybrid vehicle such as Toyota's new Prius, Toyota Harrier Hybrid and Toyota Kluger Hybrid. This system had many advantages over universal DC motor or brushed DC motor as stated under "Permanent Magnet Brushless DC motors for Consumer Products". [2]

#### 1.2 Problem Statement

Originally, the most common brushed motor had been widely used in many facilities such as in vacuum cleaners and washing machines as the manufacturing cost being quite low. However, many flaw arise such as relatively inefficient and having high acoustic noise emissions. The BLDC motor had offers with potential of increasing the efficiency and reliability.

Basically the purpose of this project is to control the speed of a BLDC motor for a car air conditioner.

#### 1.3 Objectives

The objectives of this project are as follow:

- To develop a digital controller to control the speed of BLDC motor for a car air conditioner

- To design the control circuit, power circuit to operate the BLDC motor from a battery source

- To model and simulate design with MATLAB/SIMULINK

- To construct the digital controller and power circuits

## 1.4 Project Planning

During this semester, it is proposed to design and construct the controller for BLDC motor. The process also involves simulation of the drive system using MATLAB/SIMULINK. Also it is proposed to implement the microcontroller for direct digital control. The full Gantt chart for the plan time frame is presented in Appendix.

# CHAPTER 2 LITERATURE REVIEW AND THEORY

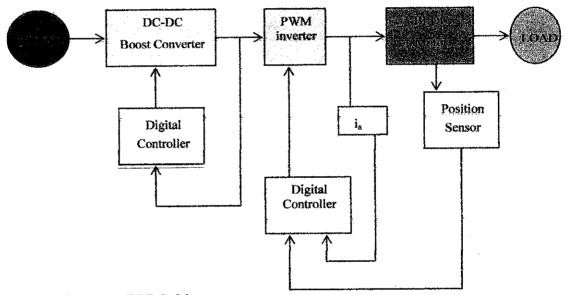

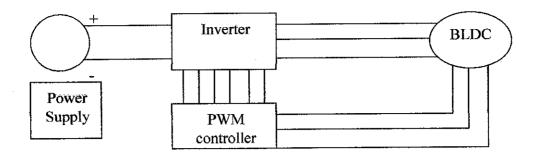

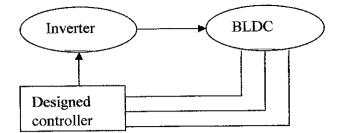

In continuation of preliminary report submitted in the first semester, the following chapters explain the project objectives of the second semester. Figure 1 show the BLDC drive system.

Figure 1 BLDC drive system

#### 2.1 Brushless DC Motor

Figure 2 BLDC motor

The information provided by a vendor for a Brushless DC motor with integral Electronics as shown in Figure 2 published [3] that it is typical for scientific applications (stirring equipment, pumps, mixing machine) and industrial applications (fans and conveyor). The motor itself is already equipped with internal drive electronics that provides control. There are two main components inside the motor; internal speed regulation and electronic commutation. The full specification of the motor are listed in the Appendix.

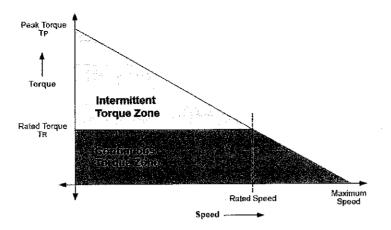

Generally the motor's speed can be controlled by changing the terminal voltage. As shown in Figure 3 it is observed that by increasing the terminal voltage, the speed will also increase. [7]

Figure 3 Torque-speed characteristic for BLDC motor.

A BLDC motor is a type of synchronous motor. As usual it consists of two main parts- stator and rotor. The stator, it consists of piled steel laminations with windings placed in the slots that are axially cut along the inner periphery. [7]

Figure 4 Stator of BLDC motor.

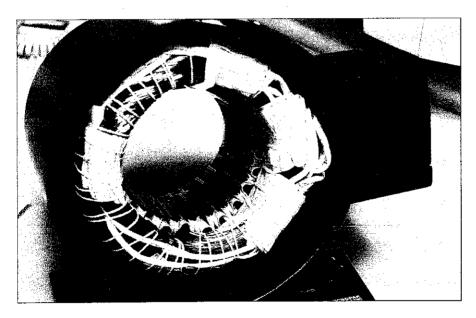

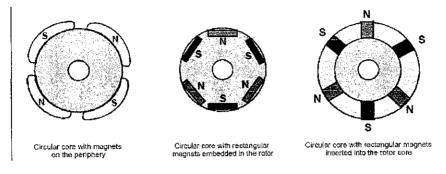

The rotor, it is made from permanent magnets that can vary from two to eight pole pairs with alternate North (N) and South (S) poles. [7]. Figure 5 show the arrangement of permanent magnets in rotor.

Figure 5 Arrangement of permanent magnet in rotor.

## 2.2 Simulation Tools

As explained earlier, the main simulation tools that will be used are PSPICE and Matlab/Simulink. The project will be concentrated on first part; the simulation. Matlab/Simulink is the most suitable simulation tools for an electromechanical system. It is essential to develop the simulation model.

For a drive system such as a BLDC motor drive, the simulation tool would be Matlab/Simulink to model the control aspects.

#### 2.3 Pulse Width Modulation Inverter

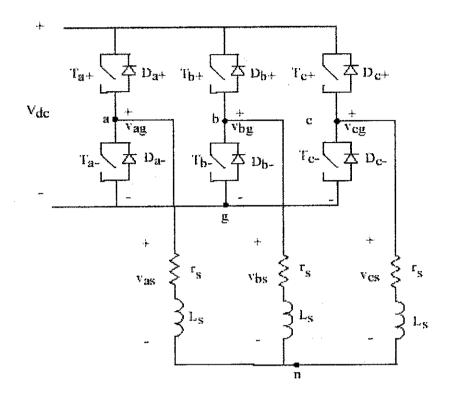

Figure 6 PWM inverter with R-L load

A PWM inverter as shown in Figure 6 is a part of the BLDC drive system. The purpose of inverter itself is simply to invert DC to AC. The objective of using specifically PWM inverter is to shape and control the three-phase output voltages in magnitude and frequency with respect to the DC input voltage. The stator of the motor is represented by the three phase loads. The input source voltage to inverter is DC voltage,  $V_{DC}$ . The output will be displaced by 120° with respect to each other. The output voltage for each leg ( $V_{ag}$ ,  $V_{bg}$ ,  $V_{cg}$ ) depends on the input voltage,  $V_{DC}$  and the switch status and independent of the output current. It also means that the output voltage is independent of the load current.

#### 2.3.1 Operation of PWM Inverter

The inverter is fed by a dc voltage and has three phase-legs each consisting of two transistors and two diodes (labeled with subscripts a, b, c). With Sine-Triangle Pulse Width Modulated (STPWM) control, the switches of the inverter are controlled based on a comparison of the sinusoidal control signal and a triangular switching signal. The sinusoidal control waveform establishes the desired fundamental frequency of the inverter output, while the triangular waveform establishes the switching frequency of the inverter. The ratio between the frequencies of the triangle wave and the sinusoid is referred to as the modulation frequency ratio. The switches of the phase legs are controlled based on the following comparison [10]:

$$\begin{split} v_{control(phase-a)} &> v_{triangle}, \ T_{a+} \ \text{is on} \\ v_{control(phase-a)} &< v_{triangle}, \ T_{a-} \ \text{is on} \\ v_{control(phase-b)} &\geq v_{triangle}, \ T_{b+} \ \text{is on} \\ v_{control(phase-b)} &< v_{triangle}, \ T_{b-} \ \text{is on} \\ v_{control(phase-c)} &> v_{triangle}, \ T_{c+} \ \text{is on} \\ v_{control(phase-c)} &< v_{triangle}, \ T_{c-} \ \text{is on} \end{split}$$

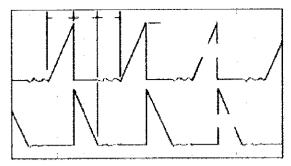

Figure 7 Sine-triangle, pulse-width-modulated control waveforms, phase voltages Vag and Vbg, and line voltage Vab

As shown in Figure 7, when the comparison is made, the output voltage range varies from the input voltage value and zero. For the line voltage, the dc components will cancel out. Thus the range will be from  $+V_{DC}$  to  $-V_{DC}$ .

# CHAPTER 3 METHODOLOGY

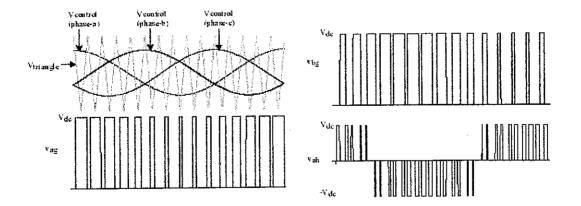

#### 3.1 Flowchart

The flowchart shown in Figure 8 indicates the methodology of this project.

Figure 8 Flowchart

#### 3.2 Tools

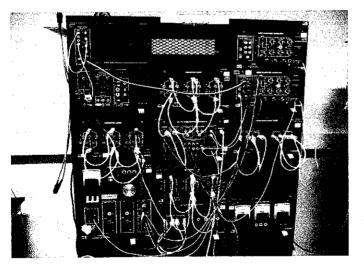

The following tools are used for software and hardware requirements of the project:

- Matlab/Simulink

- Lab-Volt Power Electronics Equipment

The simulation is conducted using Matlab/Simulink. The results of the simulation are discussed in Chapter 4 where the usage of this software is optimized. Most of the circuits for this project are built in the Power Electronics laboratory using the Lab-Volt Power Electronics Equipment. The prototype circuit is built from the available modules in the laboratory and the motor purchased from vendors.

Figure 9 Matlab software

aboratory Instrumentation System (438)

Figure 10 Lab-Volt Power Electronics Equipment

# CHAPTER 4 RESULTS AND DISCUSSION

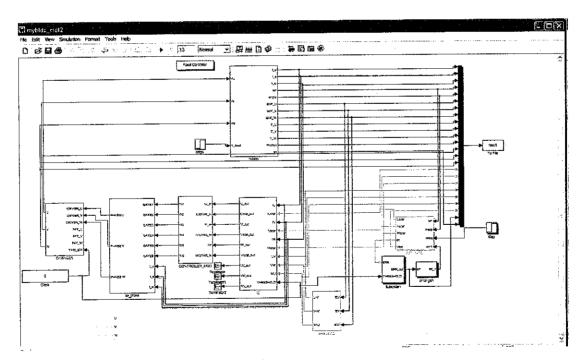

## 4.1 Simulation with Matlab/Simulink

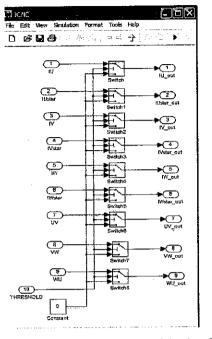

The main task of simulation is to handle the model and run it with the specified design requirements. Initially the simulation is run for the inverter and BLDC motor parts. The converter part is then simulated separately. Following is the explanation of each block that is used for the simulation. The blocks are:

- mybldc block

- estimation block

- zero crossing block

- IC block

- 120 deg trigger block

- Controller block

- All phase block

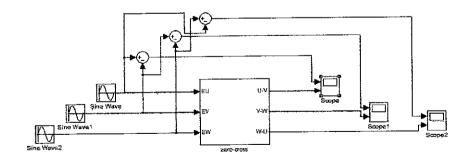

Figure 11 BLDC motor simulator

## 4.1.1 The mybldc block

Figure 12 mybldc block

This block act as a BLDC motor, where it will take inputs of three-phase voltage and load torque values. This block consists of two sub blocks; my state-space and S function. The state space model is developed from the mathematical model representing the motor equations.

Figure 13 Inside of mybldc block

| itale Space                        |                        |                                            |

|------------------------------------|------------------------|--------------------------------------------|

| State-space model:                 |                        |                                            |

| dev/dt=Ax+Bu<br>y≡Cx+Bu            |                        |                                            |

| ga ca + bu                         |                        |                                            |

| arameters                          |                        |                                            |

| A                                  |                        | 100 A. |

| 0-1.658268e+002-1.161137e+0        | 01 0; -3.386321e-015   | -245 245 -188; 0 00 2 0                    |

| R                                  |                        |                                            |

| (236.96 0 0 0; 0 236.96 0 0; 0 0 2 | 85 96 8· 0 /) 0·5060:1 | 0000                                       |

|                                    |                        |                                            |

| 10000010000100:000                 | 11000001               |                                            |

|                                    | 510,00001              |                                            |

| 0:                                 |                        |                                            |

| 0000;0000;0000;0000;               | 8000                   |                                            |

| (nitial conditions:                |                        |                                            |

| [00000]                            |                        |                                            |

| Absolute interance:                |                        |                                            |

| SUIC                               |                        |                                            |

|                                    | A                      |                                            |

Figure 14 my state space parameters

| alameters           |                   |                    |           |                     |         |

|---------------------|-------------------|--------------------|-----------|---------------------|---------|

| lamber of turns p   | er phase          |                    |           |                     |         |

| 101                 |                   |                    |           |                     |         |

| Rezistance per ph   | ase               |                    |           |                     |         |

| 0.7                 | <del></del>       |                    |           |                     |         |

| ell'inductance pa   | a phase           |                    |           |                     |         |

| 272e-3              |                   |                    |           |                     | ا ، بېا |

| notual inductace    | per phase         |                    |           |                     |         |

| 1.5e-3              |                   |                    |           |                     |         |

| lavinum value o     | kur density       |                    |           | - Falendari Surrita |         |

| 45/60               | ·····             |                    |           |                     |         |

| Totor length        |                   |                    | · · · · · |                     |         |

| 0.03                |                   | and for any states |           |                     |         |

| otor radius         |                   |                    |           |                     |         |

| 0.02                |                   |                    |           |                     |         |

| ralue of viscous f  | riction           |                    |           |                     |         |

| 0.002               |                   |                    |           |                     |         |

| aoment of intertia  |                   |                    |           |                     |         |

| 0.0002              |                   |                    |           |                     |         |

| ( atal number of p  | oles              |                    |           |                     |         |

| 4                   |                   |                    |           |                     |         |

| statting value of c | outionsb (riction |                    |           |                     |         |

| 12-1089             |                   |                    |           |                     |         |

| Static hickion      |                   |                    |           |                     |         |

| 0.089               | ·                 |                    |           |                     |         |

Figure 15 S function parameters

If the models of the BLDC motor changes, the armature resistance and inductance will need to change. However due to lack of information, the changes will be made on resistance only. This are the outputs that produce from mybldc block:

- I\_u, I\_v, I\_w are the individual phase currents

- wn is the rotor electrical speed in rad/s

- angle is the rotor electrical position as compared to the initial position

- *EMF\_U,EMF\_V,EMF\_W* are the back emf values generated in the three phases.

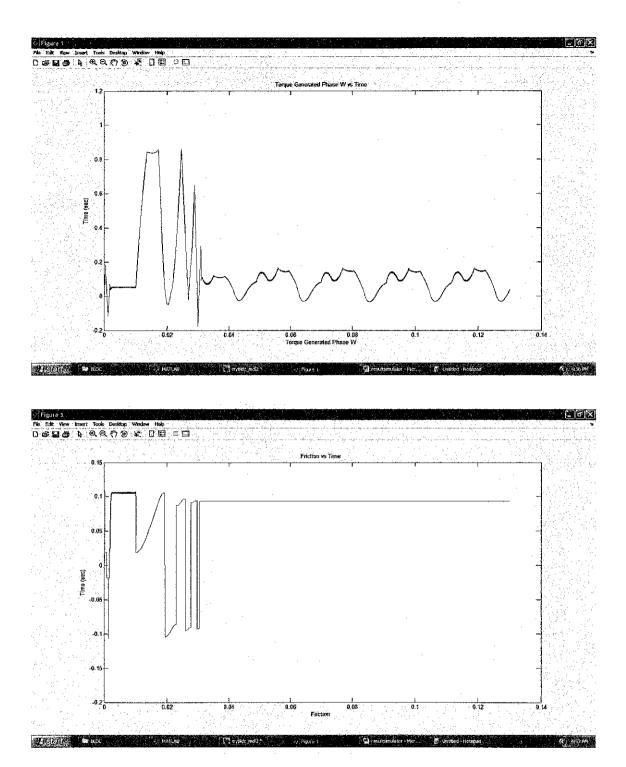

- $T_U, T_V, T_W$  are the individual phase torques.

- *Friction*: the values of the friction faced by the rotor. Contains both static and coulomb friction.

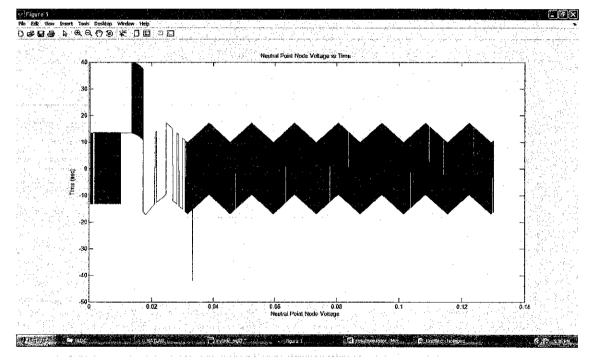

- vn is the neutral point node voltage.

### 4.1.2 The estimation block

Figure 16 Estimation block

This block calculates the error between the actual and command speed. The input to this block is taken from the mybldc block and error gen block. The inputs will be the actual value of the motor speed, rotor shaft position, the required rotor speed and lastly the fed back from the output. From this block the outputs such as command phase currents, error between command speed and actual speed and value of torque to be generated are observed.

This block can be considered to be inside the BLDC motor itself in real world and cooperates with the next block to perform the Hall Sensor part of the motor.

## 4.1.3 Zero crossing block

Figure 17 Zero crossing block

This block performs the translation of Hall Sensor inside the BLDC motor. The input parameters to this block are the back EMF for all the three phases from the motor. Then the zero crossing will translate the input into 1 and 0 output only. The inputs and output of all three phases are shown in Figure 18 to 20.

Figure 18 Zero crossing detection for Back EMF phase U and phase V

Figure 19 Zero crossing detection for Back EMF phase V and phase W

| , some<br>∋≘⊘,₽,₽, <b>₽</b> ,₽, <b>₽</b> , <b></b> | 88 T     |                                          |                                          |                       |                                                 |                 |

|----------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------|------------------------------------------|-----------------------|-------------------------------------------------|-----------------|

|                                                                                                                      |          |                                          |                                          |                       |                                                 |                 |

| 2-<br>22-<br>22-                                                                                                     |          |                                          |                                          |                       |                                                 |                 |

|                                                                                                                      |          |                                          |                                          |                       |                                                 |                 |

| 3<br>                                                                                                                |          |                                          |                                          | and the approximation | t, standardardardardardardardardardardardardard |                 |

|                                                                                                                      | <u> </u> | an a |                                          | <u> </u>              | <u>Elitz i Atte a e</u>                         |                 |

|                                                                                                                      |          |                                          |                                          |                       |                                                 |                 |

| े <u>।</u><br>स्टब्स्<br>इन्द्र                                                                                      |          |                                          |                                          |                       |                                                 |                 |

|                                                                                                                      |          |                                          | an a | <b>1</b> 9-2-2-7      | San an an Anna an A                             | 2 N. 7 N. 19 N. |

Figure 20 Zero crossing detection for Back EMF phase U and phase W

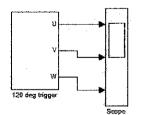

## 4.1.4 IC and 120 deg trigger blocks

Figure 21 IC block

Figure 22 120 deg trigger block

According to the author [9], the 'IC' block is used to hold the controller to its initial state till the time motor picks up sufficient speed and the back EMF voltages are significant. This system however resembles the sensorless BLDC. But it still would

be significant for the use of the present work. Inside the IC block, there are a number of switches to select the output. These switches will be changing with the threshold time that had been set.

Figure 23 Sub block of IC

Next would be the 120 deg trigger block which will give initial value to the system to ramp up the motor for a threshold time. Then it will disconnect the 120 deg trigger block from the system to perform the closed loop operation.

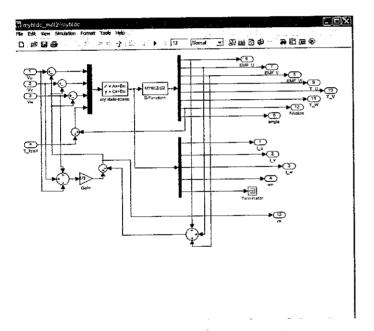

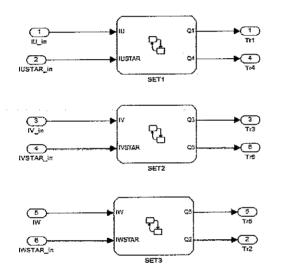

## 4.1.5 The Controller block

| >              | lU_in     | Trile        |  |  |

|----------------|-----------|--------------|--|--|

| >              | IUSTAR_E  | Ti2 >        |  |  |

| >              | IV_is.    | Tr3 p        |  |  |

| ×              | IVSTAR_in | Tr4 >        |  |  |

| >              | NV .      | Tr5 >        |  |  |

| >              | IWSTAR_in | ₹ <b>J</b> ® |  |  |

| CONTROLLER_MOB |           |              |  |  |

Figure 24 Controller block

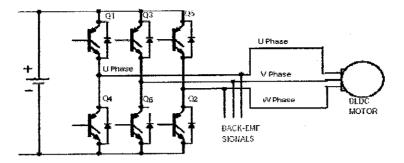

The controller block takes the output of the IC block and triggers the appropriate gates of inverter. This system will work as inverter to supply the input voltages to the BLDC motor. The reference of inverter structure is as shown in Figure 25:

Figure 25 Reference structure of Inverter

The sub system of the controller block can be viewed in Figure 26:

Figure 26 Sub system of controller block

Figure 27 All Phase Block

This block takes input from the controller which is meant for the gates of the inverter. The output voltage at Phase U is observed. The results can be seen below. Due to constant value in Gate 4, the phase voltage will take the positive terminal of the voltage source.

Figure 28 Output of voltage at phase U

### 4.2 Results and Discussion of simulation

The simulation is iniated with a specific the amount of DC input voltage to the inverter. In this simulation it is assumed that the output from the converter is ideal and without any losses. The specified amount that been change in the model are the excitation voltage, resistance per phase, inductance per phase and speed reference.

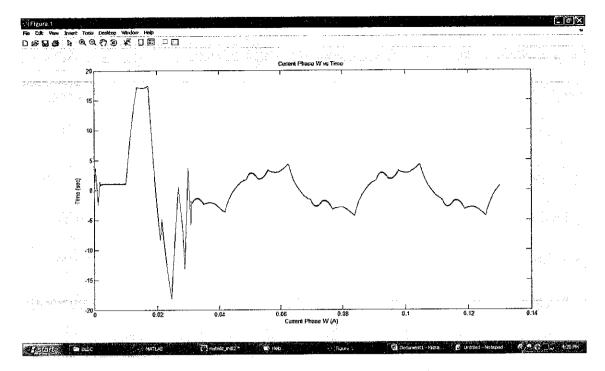

#### 4.2.1 Stator phase currents

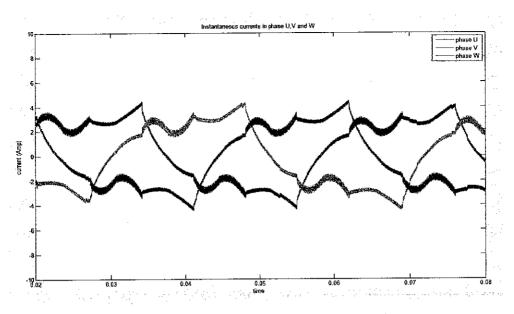

Figure 29 show the result of simulation of stator phase currents. This stator currents support the equation given where its will pass through resistance and inductance. These currents are also proportional to the torque load on the motor shaft.

$V_{i} = IR + pLI + BEMF \dots (1)$

*Torque* =  $K_t \times I \cdots (2)$

$V_t$  = Voltage applied to motor per phase I = Stator currents per phase p = d/dtL = Inductance per phase R = Resistance per phase BEMF = back EMF per phase

Figure 29 Instantaneous currents in phase U,V and W

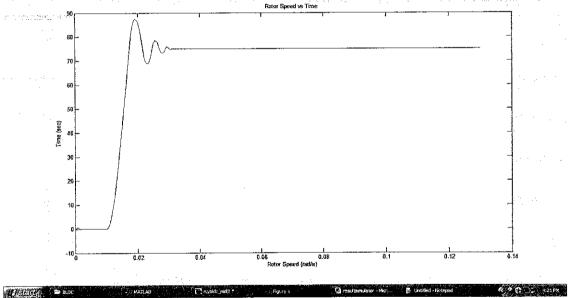

#### 4.2.2 Rotor speed

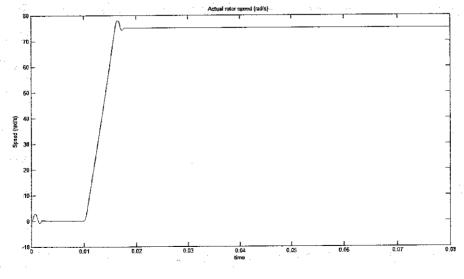

The BLDC motor must produce speed that is equivalent to the reference speed. This reference speed is entered into the estimate block. For this analysis the value had been chosen to be 75 rad/s. Inside the estimate block, it will calculate error (difference of actual to reference speed). Next, a simple PID controller will give required torque. This will directly pass the information to BLDC motor that will force the motor to require reference speed. Figure 30 show the rotor speed.

Figure 30 Actual rotor speed

At the early period, the motor does not react to any changes. At time 0.01, the speed started to increase and experienced some overshoot. The overshoot maybe due to the PID controller that had been used but the speed does not have oscillations and able to achieve required speed at 0.02 sec.

#### 4.2.3 Voltage applied to BLDC motor

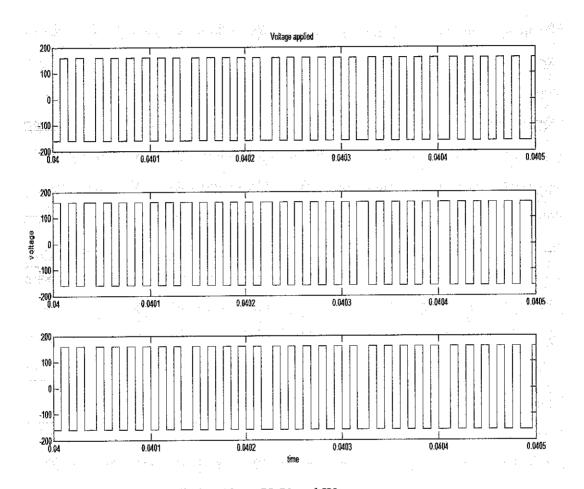

Figure 31 Voltage applied to Phase U, V and W

The voltage applied to motor is the output from changer block and all\_phase block. This combination of blocks can be defined as inverter. The output will have variation in frequency. This can be seen from Figure 31. The output is affected by Pulse Width Modulation (PWM) which is based on voltage to frequency ratio. For a fixed voltage, the frequency can be varied. The voltage is varied from +160V to -160V. This will be same to the other two phases.

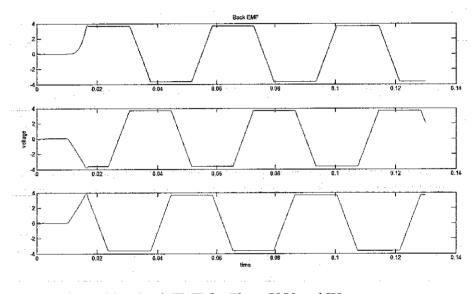

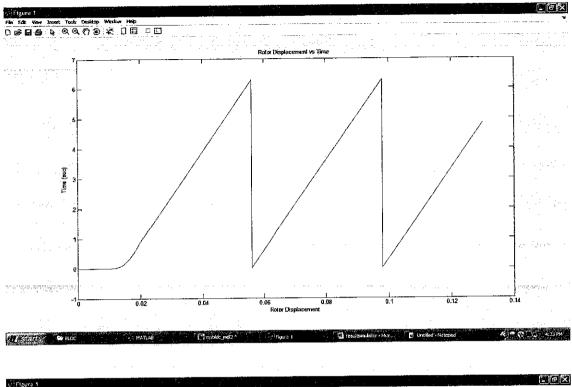

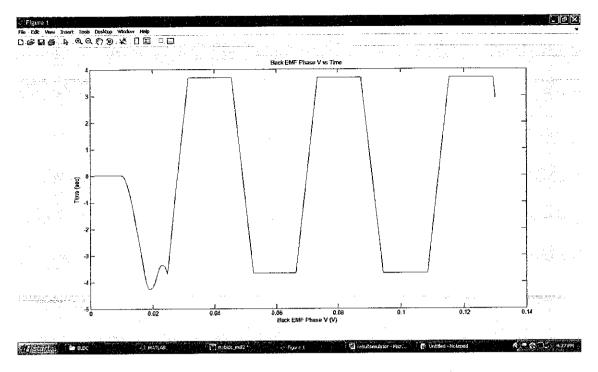

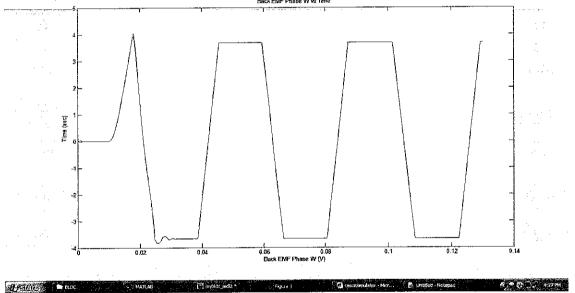

#### 4.2.4 Back Electromotive Force

Back EMF or Back Electromotive Force is the potential difference experienced by the stator coils induced by rotating permanent magnet of BLDC motor. Back EMF is produced when the motor starts to spin. It will be directly proportional to the speed. Figure 32 shows the shape of back EMF produced in the three phases. Each of the phases will experience +3.65 V to -3.65 V. The back EMFs' also experience difference of  $120^{\circ}$  with each phase. For an ideal motor, assuming that the impedance is equal to zero from equation 1 the back EMF will be equal to voltage supplied.

Figure 32 Back EMF for Phase U,V and W

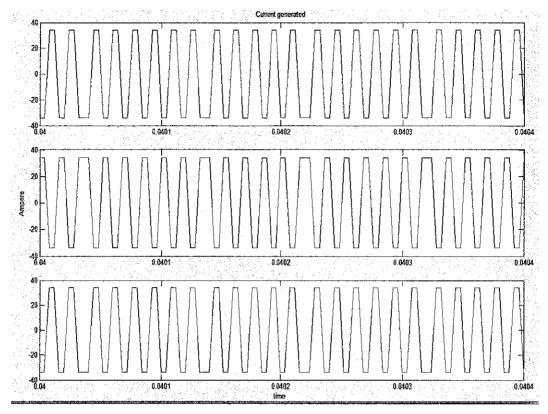

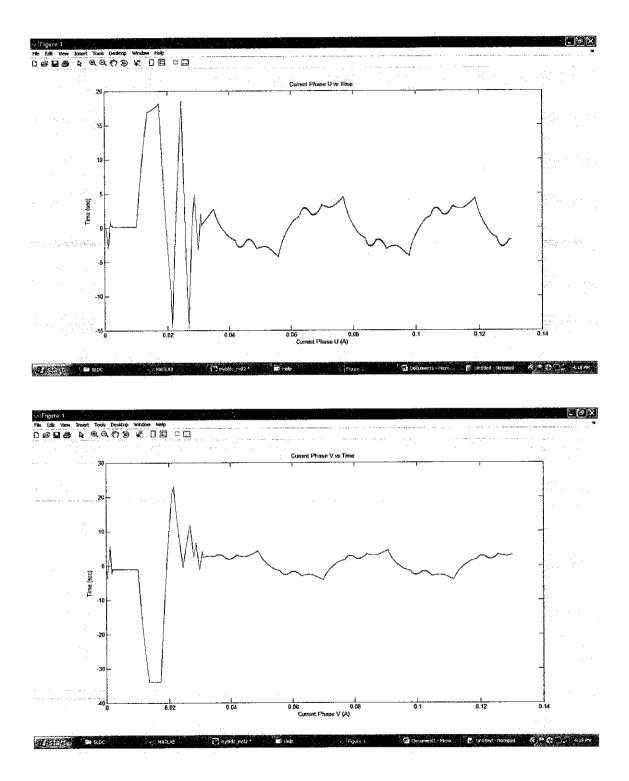

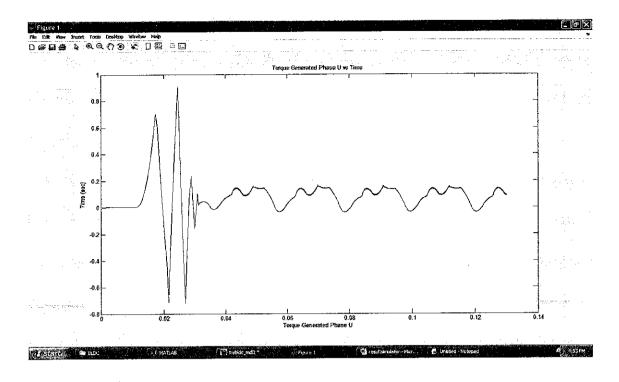

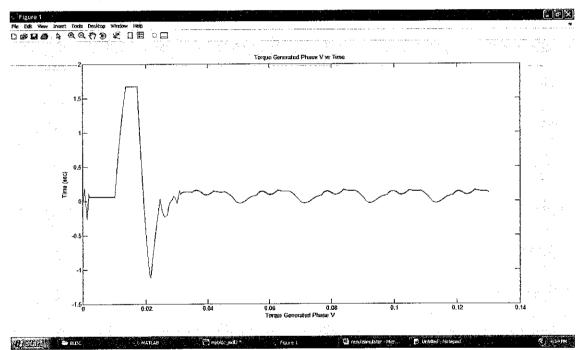

#### 4.2.5 Currents after controller

The currents from the controller are shown in Figure 33 as affected by PWM. The PWM is acting as a limiter to affect the excessive current which is limited by the applied voltage at start up. The torque required is evaluated from the PID controller. The output current is bounded together with the base current. To simplify the simulation, only one phase is calculated and the other two is only repeated but shifted by  $120^{\circ}$ . The currents generated from the controller is labeled as *IUstar*, *IVstar and IWstar*.

Figure 33 Current generated after controller to Phase U, V and W

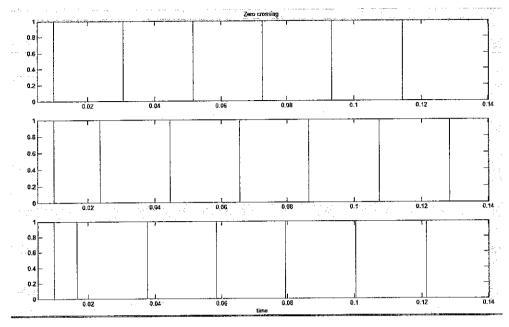

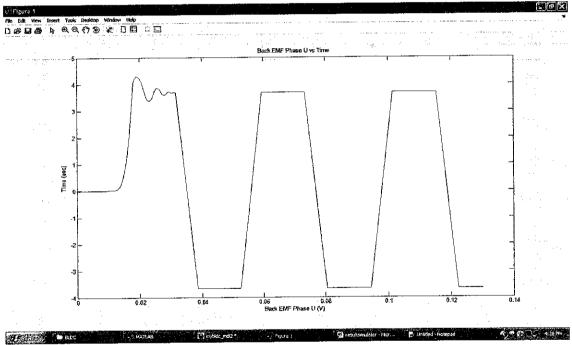

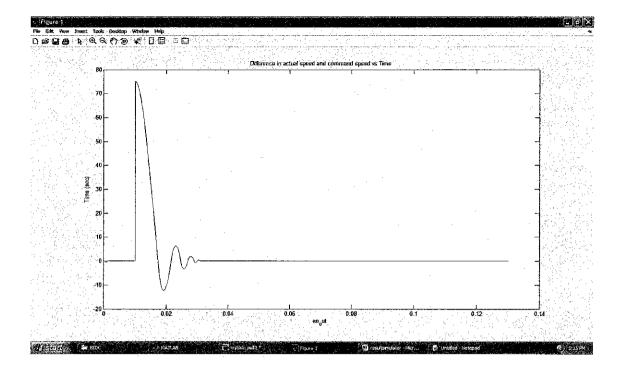

# 4.2.6 Zero crossing

Zero crossing is to evaluate the zero crossing between two phases of back EMF. This also will act like output from Hall sensor that gives 1 and 0. This signal can help to synchronize the inverter and controller.

Figure 34 Zero crossing to Phase U, V and W

In Appendix C, the output waveforms of the whole simulation are presented. The steady state simulation results are satisfactory and as expected.

# 4.3 Construct the digital controller and power circuits

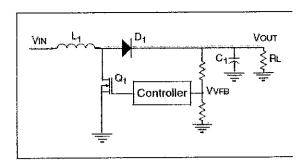

# 4.3.1 Designing boost converter

Adc-dc boost converter with a controller connected to the gate of the MOSFET is shown in Figure 35. The circuit is a type of flyback circuit. The basic concept is easy to understand. When the MOSFET, Q, turns on, the current flows through the inductor, L, begins to ramp up linearly resulting in energy storage in the inductor. The MOSFET turns off before the inductor saturates. At this time, the inductor releases its energy to the storage capacitor, C, and the load. Thus the output voltage is more than the input voltage.

Figure 35 Boost converter topology

Figure 36 The switch and diode current

The proposed design parameters for the boost converter are listed in Table1.

| Table | 1 | Design | parameters |

|-------|---|--------|------------|

| raute | T | Losign | parameters |

| Parameters                                | Value      |

|-------------------------------------------|------------|

| V <sub>IN</sub>                           | 12V        |

| V <sub>OUT</sub>                          | 30V        |

| P <sub>OUT</sub>                          | 40W        |

| F=1/T                                     | 1.5 kHz    |

| η(efficiency)                             | 80%        |

| $\Delta V_{DROP}$ (output ripple voltage) | 50 mV (2%) |

From the parameters, the L and C components are designed for continuous current operation as follows:

Duty cycle, D:

$$D = 1 - \frac{V_{in}}{V_{out}} = 1 - \frac{12}{30} = 0.6 \dots (3)$$

The inductance minimum value, L<sub>CRIT</sub>:

$$L_{crit} = \frac{RT}{2} (1-D)^2 D \dots (4)$$

$$T = 0.6667 ms$$

$$R = \frac{V_{out}^2}{P_{out}^2} = \frac{(30)^2}{40} = 22.5\Omega \dots (5)$$

$L_{crit} = 720 \,\mu H$

L=1 mH, since L must be greater than  $L_{CRIT}$ .

Output ripple voltage:

$$\frac{\Delta V_{drop}}{V_o} = \frac{D}{RCf} \dots (6)$$

$$0.02 = \frac{0.6}{(22.5)C(1.5k)}$$

$$C = 888\,\mu F$$

The values of capacitor and inductor are implemented from above calculation to design the boost converter for the system. The converter is connected to the inverter to supply a constant value of voltage. The boost converter is assumed to work in continuous conduction mode.

# 4.3.2 Experimental test on BLDC motor

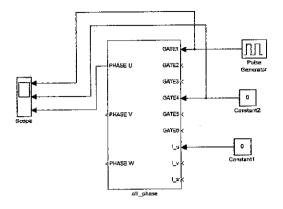

The experimental setup for testing the BLDC motor is as shown in Figure 37. The power supply as mentioned earlier comes from boost converter providing a fixed value of DC voltage to the inverter. For this project, the main aim is to build a controller that will be able to control the speed of BLDC motor, which takes the response of BLDC motor and reference speed as input to the controller.

Figure 37 Experimental setup

The PWM controller provides gating pulses to turn-on the IGBT/MOSFET switches of the inverter. These pulses correspond to the signals generated by the Hall Sensor of BLDC motor. Finally the inverter converts the DC voltage to an AC voltage translated by the effect of pulses provided by the controller. This procedure continues until the speed of BLDC motor match the reference speed.

Three types of tests are conducted on BLDC motor.

- Test BLDC motor without Hall Sensors feedback to the Lab-Volt controller

- Test BLDC motor while Hall Sensor are attached along with constructed controller

- Test BLDC motor with designes controller

Figure 38 Lab-Volt control unit and inverter

Figure 39 Test BLDC motor without Hall Sensor feedback to controller

In the first part, the test is conducted in the Power Electronics laboratory where the Lab-Volts equipments are being used. The equipments that are involved in testing are:

- Mobile Workstation (8110)

- Power Supply (8821-2X)

- Enclosure/power supply (8840)

- Connection leads and accessories (8951)

- Chopper/Inverter Control Unit (9029)

- Resistive loads (8311)

- Smoothing Inductors (8325-1X)

- IGBT Chopper/inverter module (8837-AX)

A variable DC voltage power supply is selected where the DC input can be varied from zero to 315V. In the Chopper/Inverter control unit, the mode is chosen to be V/F to obtain PWM response. The responses of pulses trigger the IGBT switches of the controlled inverter by the control unit. There will be a knob call DC SOURCE 1 that will regulate the duty cycle which will correspond to the frequency of the voltage applied to the BLDC motor. Figure below show the Chopper/Inverter control unit.

Figure 40 Chopper/Inverter control unit

When DC SOURCE 1 is tuned from minimum to middle range of the knob, the shaft of BLDC motor will turn in clockwise, and when turned from middle to maximum, the shaft turns anticlockwise. From the conducted test the waveforms observed are voltage supply, voltage from inverter, current from inverter and speed of motor. For this part, the test is conducted in anticlockwise manner.

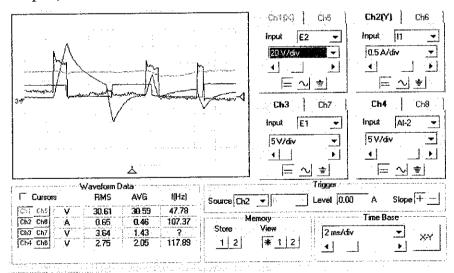

Figure 41 At 20% duty cycle

Figure 42 At 30% duty cycle

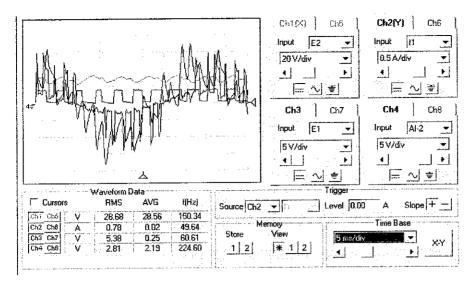

Figure 43 At 40% duty cycle

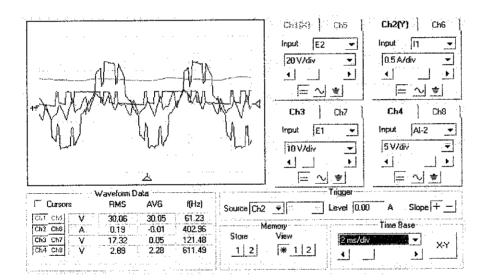

|                         |                               |                 | געעעעעעעעעעעעעעעעעעעעעעעעעעעעעעעעעעעע | E2 ↓<br>//div ↓<br>= △ €<br>3 Ch7<br>E1 ↓<br>/div ↓ | Ch2(Y)     Ch6       Input     I1       0.5 A/div     ▼       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶       ↓     ▶ |

|-------------------------|-------------------------------|-----------------|---------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cursors                 | ↔<br>Waveform Data<br>BMS AVG | [[Hz]           | Source Ch2 →                          | Trigger                                             | <u>≢</u><br>AStape[+ -]                                                                                                                                                                                                                       |

| Cist Ch5 V<br>Ch2 Ch6 A | 28.35 28.25<br>0.77 0.01      | 148.13<br>57.71 | Store View                            |                                                     | Time Base                                                                                                                                                                                                                                     |

| Ch3 Ch7 V<br>Ch4 Ch8 V  | 9.70 0.14<br>2.86 2.28        | 56.86<br>506.75 |                                       | 2 5ms/dv                                            |                                                                                                                                                                                                                                               |

Figure 44 At 50% duty cycle

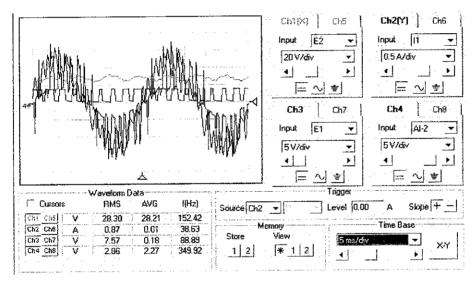

Figure 45 At 60% duty cycle

|                        |                           |          |              | )V/div<br> | Ch2[Y]       Input       [1]       [0.5 A/div       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       • <td< th=""><th><br/>Ch8 ]</th></td<> | <br>Ch8 ] |

|------------------------|---------------------------|----------|--------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                        | Waveform Data             |          |              | Trigger    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|                        | RMS AVG                   | f(Hz) Sc | uice Ch2 👻 🕅 | Level 0.   | 00 A Slope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | F         |

| Ch1 Ch5 V<br>Ch2 Ch6 A | 29.51 29.47<br>0.37 -0.01 | 83.50    | Memory       |            | Time Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ······    |

| Ch2 Ch6 A              | 0.37 -0.01                | 104.57   | Store View   | 5 ms/c     | fiv ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1         |

| Ch4 Ch8 V              | 2.81 2.19                 | 525.75   | 12 *         | 1 2 1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | X·Y       |

Figure 46 At 80% duty cycle

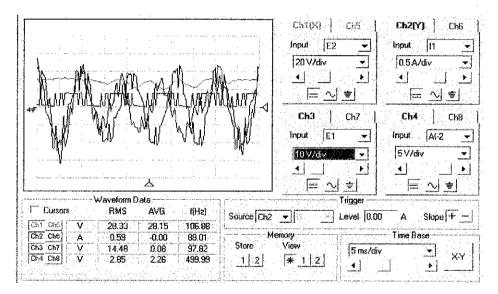

Figure 47 At 100% duty cycle

| Table | 2 | Results | of test |

|-------|---|---------|---------|

|       |   |         |         |

120*F*

| Duty Cycle | Input Voltage | Voltage line to line | Speed<br>(rpm) |

|------------|---------------|----------------------|----------------|

| 20%        | 30V           | 3.64V                | 390.3          |

| 30%        | 30V           | 5.38V                | 746.3          |

| 40%        | 30V           | 7.57V                | 1173.2         |

| 50%        | 30V           | 9.70V                | 1700.1         |

| 70%        | 30V           | 14.48V               | 310.25         |

| 80%        | 30V           | 15.49V               | 3646.7         |

| 100%       | 30V           | 17.32V               | 3805.1         |

The input voltage applied is 30 V but due to some losses the output display is less. The control unit provides the PWM pulses to the IGBT inverter module. The controller had established internally the triangular-wave and sine-wave signals to generate the PWM control signals.

The difference can be detected from the duty cycle where the frequencies of PWM control signals are changing. From reference, the frequency that supplied to motor must be at least 10 times more than the frequency inside motor. So if the output frequency from inverter is 600Hz, the exact motor frequency responds to this only 60Hz. To calculate the speed equation 7 below will be used

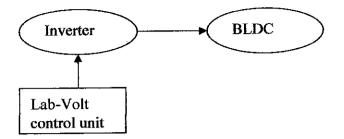

Figure 48 Test RIDC motor while Hall Sensor are attached to designed

Figure 48 describes how the test is conducted. The Hall Sensor signals from motor are passed on to the designed controller. The performance of the controller is explained in the following section.

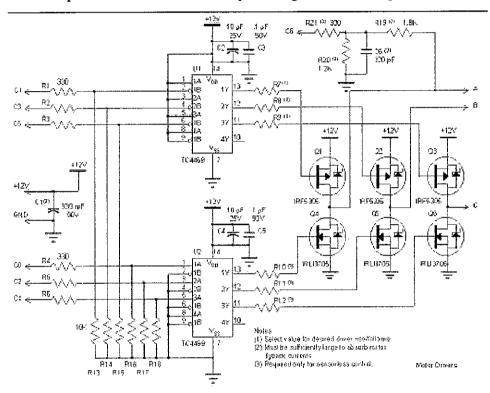

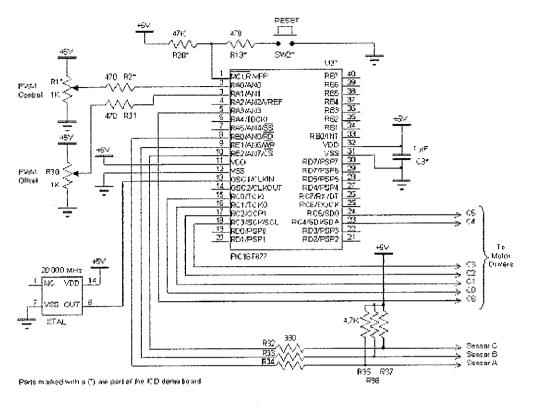

### 4.3.4.1 Designed controller hardware

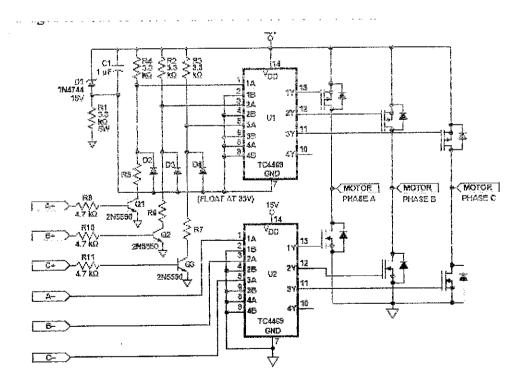

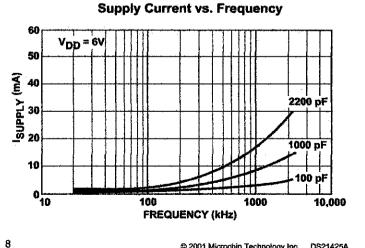

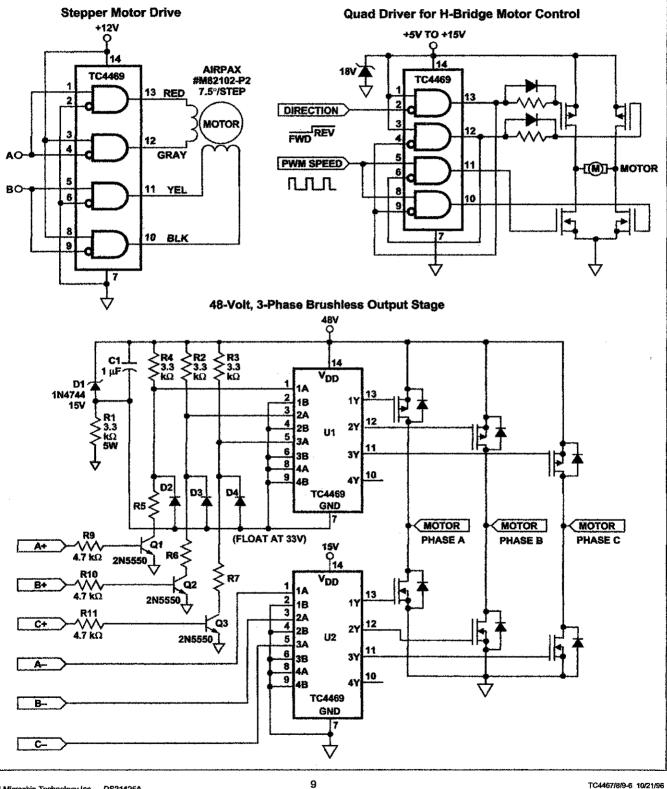

The designed controller circuit diagram is constructed based on the report of Microchip AN857. The circuit is easy to design and to be implemented.

Figure 49 Circuit diagram-part1

Figure 50 Circuit diagram-part2

The controller is designed using PIC16F877. The coding to be implemented for the microcontroller is presented in Appendix D. Pin 1 is to reset the whole process if a fault occurs. There is a reset button attached to this pin which the user can press it when reset condition is needed. Pins 2 and 3, determine the value of duty cycle to be entered to the microcontroller. At Pin 13, the clock input to the microcontroller is given. The component attached is a crystal oscillator that provides a frequency of 20 MHz. There will be three pins 8, 9 and 10 that lead to Hall Sensors of the motor. Pins that will give output pulses to the motor drive are Pins 15, 16, 17, 18, 23 and 24.

## 4.3.5 Test BLDC motor with the designed controller

This is the final part of fabrication of circuit, where the designed controller is fully installed with the system. From here the controller will receive signals from the Hall sensors and give the pulses to inverter without depending on Lab-Volt control unit.

Figure 51 Test BLDC motor with designed controller alone

### 4.3.6 Correction to the controller

The reference of Microchip AN857 had some error that gives some flaw to the performance of the controller. Following is the correction to the controller circuit. From previous circuit we can see that there is fatal error where the Vcc is connected directly to ground. This will cause fault to the circuit where it will gives overload reading at the power supply. The correction below shows that there will be diode with parallel capacitor and together with resistor between Vcc and ground connection. This will overcome the problems that arise. Due to time constraint, the author only

Figure 52 The correction of controller circuit

# CHAPTER 5

# CONCLUSION AND RECOMMENDATION

BLDC motor had started to take over in industrial applications due to its advantages over the conventional motor. This project presents one of BLDC motor application in every day life. The project task is to control the speed of a permanent magnet BLDC motor for air conditioning. The project is divided into two parts; simulation and design of power and control circuits.

The simulation of the drive system is performed with Matlab/Simulink and the circuitry part is being assembled in the Power Electronics laboratory. From the simulation results, the author observed the similarity between Sensorless BLDC motor and BLDC motor with Hall Sensors. The system of sensorless drive takes the value back EMF and translate it as a parameter to control the motor but a BLDC motor with sensor control takes the output of Hall Sensors. The simulation mainly depends on the reference speed and impedance together with the excitation voltage supply to the simulation block. This would directly give the correct output of actual speed from the BLDC motor.

In designing the power circuit, there are a few considerations that must be taken into consideration. The supply is from 12V battery which shows that this circuit is efficiently able to work inside an air conditioner of a car. The design starts with designing the boost converter provides an exact output of voltage. This voltage will then supplied to inverter that controlled by PWM controller. The PWM control signals play a main role to determine the output voltage of the inverter. To complete it the system will be attach to a BLDC motor. From here, the author learned that the output voltage is dependent on input voltage. To vary the output means to vary the DC input voltage.

The Lab-Volt modules had been the main components in designing hardware of the

system circuits. In control circuits, the PIC microcontroller is fully used to create control to system drive. The tests are done with two bases; first with Lab-Volt control unit and second with designed controller. Most of the electronics components are provided from Microchips Company. The BLDC motor is bought from LIN Engineering.

As the design of the circuit is made in open loop manner, a closed-loop control can be made for future work. Although there is some reference value added but there is no implementation of PID controller for the feedback loop. Due to time constraint, the tests could not be conducted on closed loop system. In closed loop method, the tasks will be quite the same with additional work to find the proportional, integral and derivative gain. Next is to fine tune each of the gains to get the best result.

# REFERENCES

# [1] http://globaldensoproducts.com/cc/cacs/electrical\_compressor.html

[2] http://mag-net.ee.umist.ac.uk/reports/P11/p11.html

[3] http://my.farnell.com/jsp/endecaSearch/partDetail.jsp?sku=4158428

[4] Dawson III, Charlie H, Simulation Tools: a descriptive analysis, The Electromechanical Systems Lab, Department of Electrical and Computer Engineering, The University of Alabama.

[5] http://www.instructables.com/id/ELJ34XZMO4EP286HGO/

[6] http://www.edn.com/article/CA382783.html

[7] http://www.linengineering.com/site/BLDC/BL24A.htm

[8]Davendra Rai, Simulink Simulator Usage Manual: Brushless DC Motor, Department of Electronics and Communication engineering, National Institute of Technology Karnataka, India.

[9] http://www.ewh.ieee.org/soc/es/Nov1998/08/PWMINV.HTM

[10] http://146.83.6.6/electricar/files/00857a.pdf

[11] http://www.instructables.com/id/ELJ34XZMO4EP286HGO/

[12] http://www.denso.com.sg/tpl/pdtlineup\_car\_compressor.html

[13] http://ww1.microchip.com/downloads/en/DeviceDoc/21425b.pdf

# APPENDIX A GANTT CHART

|          |                                                                    |   |   |   |   |   | WĒ | WÈEKS | 1                |      |    |    |    |    |

|----------|--------------------------------------------------------------------|---|---|---|---|---|----|-------|------------------|------|----|----|----|----|

|          | Activities                                                         | 2 | 3 | 4 | 5 | 9 | 7  | 8     | 6                | 10   | 11 | 12 | 13 | 14 |

|          | Conduct literature review on project                               |   |   |   |   |   |    |       |                  |      |    |    |    |    |

| R        | 2 Configure the hardware specification.                            |   |   |   |   |   |    |       |                  |      |    |    |    |    |

| m        | Simulate system inside MATLAB/SIMULINK                             |   |   |   |   |   |    |       |                  |      |    |    |    |    |

| <b>*</b> | Model of each component inside MATLAB (mathematical model)         |   |   |   |   |   |    |       |                  |      |    |    |    |    |

| 2        | Using microcontroller to design a direct digital control for motor |   |   |   |   |   |    |       |                  |      |    |    |    |    |

| 9        | Fabricate system                                                   |   |   |   |   |   |    |       | n<br>L<br>Hen Ne |      |    |    |    |    |

| <b>F</b> | Documentation of project                                           |   |   |   |   |   |    |       |                  | 3.0) |    |    |    |    |

|          |                                                                    |   |   |   |   |   |    |       |                  |      |    |    |    |    |

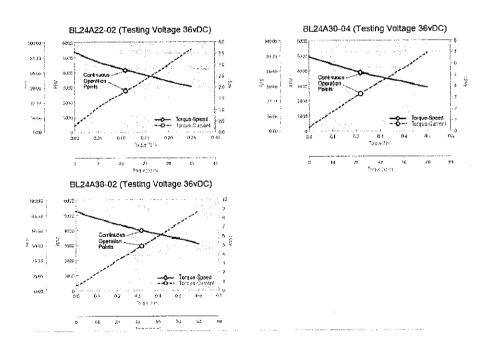

# APPENDIX B BLDC MOTOR SPECIFICATION

| Model                           | BL24A22-02 | BL24A30-04 | BL24A38-02 |

|---------------------------------|------------|------------|------------|

| Number of Poles                 | 4          | 4          | 4          |

| Number of Phase                 | 3          | 3          | 3          |

| Rated Voltage (VDC)             | 36         | 36         | 36         |

| Rated Speed (RPM)               | 4000       | 4000       | 4000       |

| Rated Torque (Oz-in)            | 15.58      | 31.15      | 45.32      |

| Power (W)                       | 46         | 92         | 133        |

| Peak Torque (Oz-in)             | 55.23      | 99.13      | 141.61     |

| Peak Current (A)                | 6.8        | 14.5       | 17.6       |

| Torque Constant (Oz-in/A)       | 8.92       | 8.92       | 8.92       |

| Back E.M.F. (V/KRPM)            | 6.6        | 6.6        | 6.6        |

| Rotor Inertia (oz.in^2)         | 0.41       | 0.65       | 0.94       |

| Body Length (am)                | 55         | 75         | 95         |

| Body Length<br>(in)-Dimension A | 2.17       | 2.95       | 3.74       |

| Mass (Kg)                       | 0.5        | 0.75       | 1          |

# APPENDIX C RESULTS OF SIMULATION

and the second secon

Refigure 1 Re Edit Wew Insert Tools Desitop Window Heb D 공장되 중 및 국 국 국 왕 가 옷 [] 몸 그 다 \_\_\_\_ ..... ..... Back EMF Phase W vs Time

0 0.02 0.04 0.06 0.08 0.1 0.12 3-W star (A) [United-Narceeth Classic control of the star o

S. SOFPL

~

# APPENDIX D CODING FOR MICROCONTROLLER

```

; *

; Filename: sensored.asm *

Date: 11 Feb. 2002 *

2

; File Version: 1.0 *

*

:

; Author: W.R. Brown *

; Company: Microchip Technology Incorporated *

;

*

2

; *

; Files required: pl6f877.inc *

2

2

ł

; *

; Notes: Sensored brushless motor control Main loop uses 3-bit *

; sensor input as index for drive word output. PWM based on *

; TimerO controls average motor voltage. PWM level is determined *

PWM level is determined from ADC reading of potentiometer. *

; *

.

list p=16f877 ; list directive to define processor

#include <pl6f877.inc> ; processor specific variable definitions

_____CONFIG__CP_OFF & _WDT_OFF & _BODEN_ON & _PWRTE_ON & _HS_OSC & _WRT_ENABLE_OFF &

LVP ON &

DEBUG OFF & CPD_OFF

*

;* Define variable storage

· *

CBLOCK 0x20

ADC ; PWM threshold is ADC result

LastSensor ; last read motor sensor data

DriveWord ; six bit motor drive data

ENDC

;*

.

;* Define I/O

*

#define OffMask B'11010101'

#define DrivePort PORTC

#define DrivePortTris TRISC

#define SensorMask B'00000111'

#define SensorFort PORTE

#define DirectionBit PORTA,1

******

org 0x000 ; startup vector

nop ; required for ICD operation

clrf PCLATH ; ensure page bits are cleared

goto Initialize ; go to beginning of program

ORG 0x004 ; interrupt vector location

;*

;* Initialize I/O ports and peripherals

;*

Initialize

clrf DrivePort ; all drivers off

banksel TRISA

; setup I/O

clrf DrivePortTris : set motor drivers as outputs

moviw B'000000011' ; A/D on RAO, Direction on RA1, Motor sensors on RE<2:0>

movwf TRISA ;

; setup TimerO

movlw B'11010000'; TimerO: Fosc, 1:2

```

```

movwf OPTION REG

; Setup ADC (bank1)

movlw B'00001110' ; ADC left justified, ANO only

movwf ADCON1

banksel ADCONO

; setup ADC (bank0)

moviw B'11000001' ; ADC clock from int RC, ANO, ADC on

movwf ADCON0

bsf ADCON0,GO ; start ADC

clrf LastSensor ; initialize last sensor reading

call Commutate ; determine present motor position

clrf ADC ; start speed control threshold at zero until first ADC

reading

;****

;*

;* Main control loop

;*

Loop

call ReadADC ; get the speed control from the ADC

incfsz ADC,w ; if ADC is 0xFF we're at full speed - skip timer add

goto PWM ; add Timer0 to ADC for PWM

movf DriveWord, w ; force on condition

goto Drive ; continue

PWM

movf ADC,w ; restore ADC reading

addwf TMR0,w ; add it to current Timer0

movf DriveWord, w ; restore commutation drive data

btfss STATUS,C ; test if ADC + Timer0 resulted in carry

andlw OffMask ; no carry - suppress high drivers

Drive

movwf DrivePort ; enable motor drivers

call Commutate ; test for commutation change

goto Loop ; repeat loop

ReadADC

;*

;* If the ADC is ready then read the speed control potentiometer

;* and start the next reading

btfsc ADCON0, NOT DONE ; is ADC ready?

return ; no - return

movf ADRESH,w ; get ADC result

bsf ADCON0,GO ; restart ADC

movwf ADC ; save result in speed control threshold

return ;

··· · ·

* *

;*

* Read the sensor inputs and if a change is sensed then get the

;* corresponding drive word from the drive table

Commutate

movlw SensorMask ; retain only the sensor bits

andwf SensorPort,w ; get sensor data

xorwf LastSensor, w ; test if motion sensed

btfsc STATUS,Z ; zero if no change

return ; no change - back to the PWM loop

xorwf LastSensor,f ; replace last sensor data with current

btfss DirectionBit ; test direction bit

goto FwdCom ; bit is zero - do forward commutation

; reverse commutation

movlw HIGH RevTable ; get MS byte of table

movwf PCLATH ; prepare for computed GOTO

movlw LOW RevTable ; get LS byte of table

goto Com2

FwdCom ; forward commutation

movlw HIGH FwdTable ; get MS byte of table

movwf PCLATH ; prepare for computed GOTO

movlw LOW FwdTable ; get LS byte of table

Com2

addwf LastSensor,w ; add sensor offset

btfsc STATUS,C ; page change in table?

incf PCLATH, f ; yes - adjust MS byte

call GetDrive ; get drive word from table

movwf DriveWord ; save as current drive word

return

GetDrive

movwf PCL

```

```

57

```

```

***********

**

;*

;* The drive tables are built based on the following assumptions:

;* 1) There are six drivers in three pairs of two

;* 2) Each driver pair consists of a high side (+V to motor) and low side (motor to

ground) drive

;* 3) A 1 in the drive word will turn the corresponding driver on

(* 3) A 1 in the drive word will turn the corresponding driver on

(* 4) The three driver pairs correspond to the three motor windings: A, B and C

(* 5) Winding A is driven by bits (>) and (>) where (>) is A's high side drive

(* 6) Winding B is driven by bits (>) and (>) where (>) is B's high side drive

(* 7) Winding C is driven by bits (>) and (>) where (>) is C's high side drive

(* 7) Winding C is driven by bits (>) and (>) where (>) is C's high side drive

(* 7) Winding C is driven by bits (>) and (>) where (>) is C's high side drive

(> 7) Winding C is driven by bits (>) and (>) where (>) is C's high side drive

;* 8) Three sensor bits constitute the address offset to the drive table

;* 9) A sensor bit transitions from a 0 to 1 at the moment that the corresponding

;* winding's high side forward drive begins.

;* 10) Sensor bit <0> corresponds to winding A

;* 11) Sensor bit <1> corresponds to winding B

;* 12) Sensor bit <2> corresponds to winding C

FwdTable

retlw B'00000000' ; invalid

retlw B'00010010' ; phase 6

ret1w B'00001001' ; phase 4

retlw B'00011000' ; phase 5

retlw B'00100100' ; phase 2

retlw B'00000110' ; phase 1

retlw B'00100001' ; phase 3

retlw B'00000000' ; invalid

RevTable

retlw B'00000000' ; invalid

retlw B'00100001' ; phase /6

retlw B'00000110' ; phase /4

retlw B'00100100' ; phase /5

retlw B'00011000' ; phase /2

retlw B'00010001' ; phase /1

retlw B'00010010' ; phase /3

retlw B'00000000' ; invalid

END ; directive 'end of progra

```

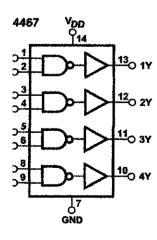

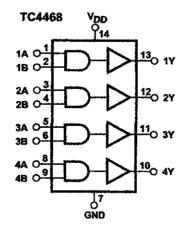

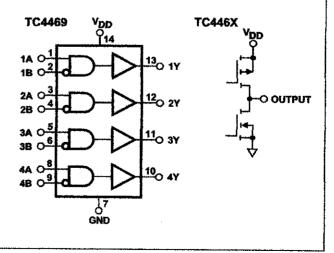

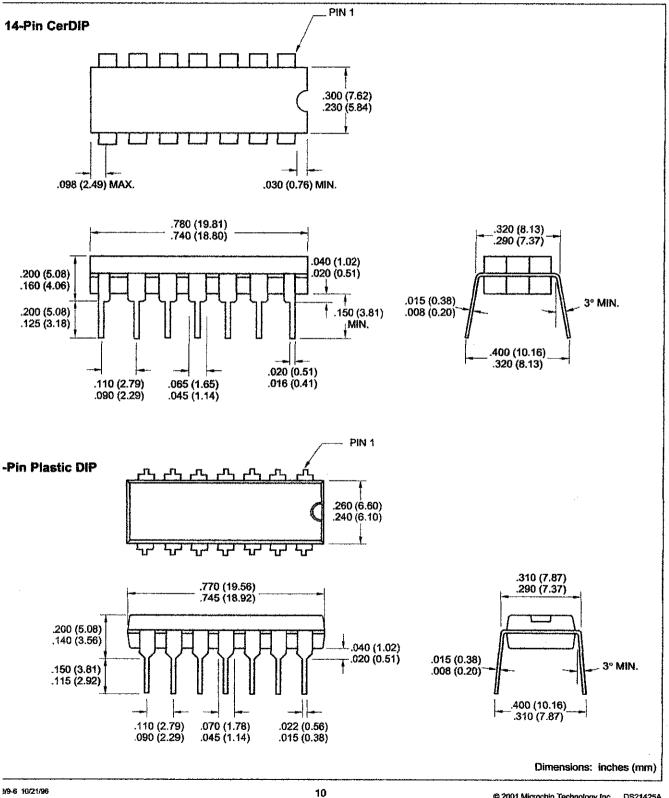

# GIC-INPUT CMOS QUAD DRIVERS

### **\TURES**

| High Peak Output Current              | 1.2A       |

|---------------------------------------|------------|

| Nide Operating Range                  | 4.5 to 18V |

| Symmetrical Rise and Fall Times       |            |

| Short, Equal Delay Times              |            |

| .atchproof! Withstands 500mA inductiv | e Kickback |

| 3 Input Logic Choices                 |            |

| - AND / NAND / AND + Inv              |            |

| <b>?kV ESD Protection on All Pins</b> |            |

|                                       |            |

# **'LICATIONS**

Seneral-Purpose CMOS Logic Buffer Driving All Four MOSFETs in an H-Bridge Direct Small Motor Driver Relay or Peripheral Drivers CD Driver 'in-Switching Network Driver

# **GENERAL DESCRIPTION**

The TC446X family of four-output CMOS buffer/drivers are an expansion from our earlier single- and dual-output drivers. Each driver has been equipped with a two-input logic gate for added flexibility.

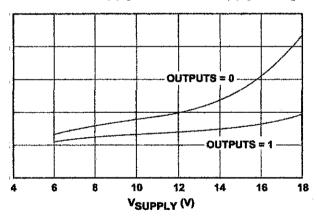

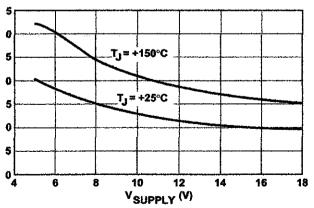

The TC446X drivers can source up to 250 mA into loads referenced to ground. Heavily loaded clock lines, coaxial cables, and piezoelectric transducers can all be easily driven with the 446X series drivers. The only limitation on loading is that total power dissipation in the IC must be kept within the power dissipation limits of the package.

The TC446X series will not latch under any conditions within their power and voltage ratings. They are not subject to damage when up to 5V of noise spiking (either polarity) occurs on the ground line. They can accept up to half an amp of inductive kickback current (either polarity) into their outputs without damage or logic upset. In addition, all terminals are protected against ESD to at least 2000V.

# **ORDERING INFORMATION**

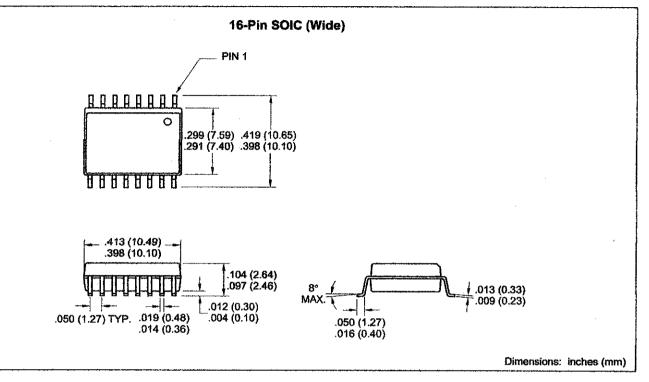

| Part No.  | Package            | Temp. Range     |

|-----------|--------------------|-----------------|

| TC446xCOE | 16-Pin SOIC (Wide) | 0° to +70°C     |

| TC446xCPD | 14-Pin Plastic DIP | 0° to +70°C     |

| TC446xEJD | 14-Pin CerDIP      | - 40° to +85°C  |

| TC446xMJD | 14-Pin CerDiP      | - 55° to +125°C |

\*A digit must be added in the "x" position to define the device input configuration: TC446x — 7 NAND

8

AND

9 AND with INV

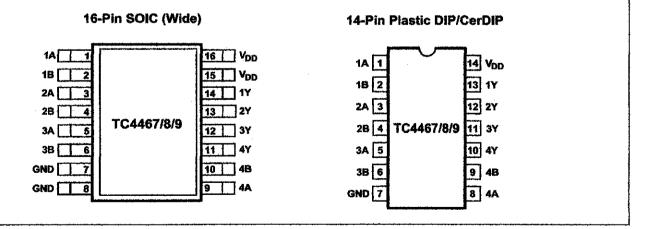

## **IC DIAGRAMS**

Microchip Technology Inc. DS21425A

TC4467/8/9-6 10/21/96

# LOGIC-INPUT CMOS QUAD DRIVERS

# 467 468 469

# **DLUTE MAXIMUM RATINGS\***

| / Voltage<br>/oltage                           |                 |

|------------------------------------------------|-----------------|

| perating                                       | +150°C          |

| orage                                          | - 65° to +150°C |

| ium Lead Temperature                           |                 |

| oldering, 10 sec)                              | +300°C          |

| ting Ambient Temperature Range                 |                 |

| Device                                         | 0° to +70°C     |

| Device                                         | 40° to +85°C    |

| Device                                         | - 55° to +125°C |

| ge Power Dissipation ( $T_A \le 70^{\circ}C$ ) |                 |

| -Pin CerDIP                                    | 840mW           |

| -Pin Plastic DIP                               | 800mW           |

| -Pin Wide SOIC                                 |                 |

|                                                |                 |

| Package Thermal Resis | stance            |         |

|-----------------------|-------------------|---------|

| 14-Pin CerDIP         | R <sub>0J-A</sub> | 100°C/W |

| :                     | R <sub>0J-C</sub> |         |

| 14-Pin Plastic DIP    | R <sub>8J-A</sub> |         |

| ,                     | R <sub>6J-C</sub> |         |

| 16-Pin Wide SOIC      | R <sub>0J-A</sub> |         |

|                       | R <sub>®J-C</sub> |         |

\*Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

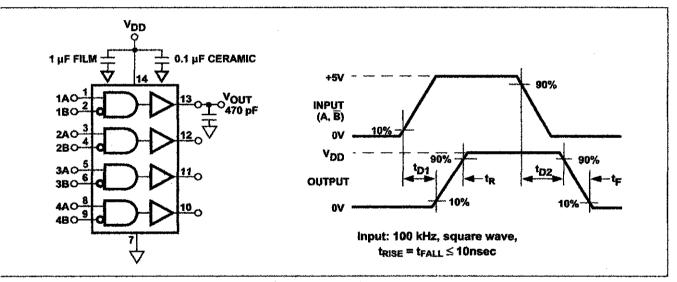

# **TRICAL CHARACTERISTICS:** Measured at $T_A = +25^{\circ}$ C with $4.5V \le V_{DD} \le 18V$ , unless otherwise specified.

| öl           | Parameter                                        | Test Conditions                                | Min                     | Тур | Max                                   | Unit    |

|--------------|--------------------------------------------------|------------------------------------------------|-------------------------|-----|---------------------------------------|---------|

|              | · · · ·                                          |                                                |                         |     |                                       |         |

|              | Logic 1, High Input Voltage                      | Note 3                                         | 2.4                     |     | VDD                                   | V       |

|              | Logic 0, Low Input Voltage                       | Note 3                                         | 0                       |     | 0.8                                   | V       |

|              | Input Current                                    | $0V \le V_{IN} \le V_{DD}$                     | 1                       |     | 1                                     | μA      |

| it           |                                                  |                                                |                         |     | • • • • • • • • • • • • • • • • • • • |         |

|              | High Output Voltage                              | ILOAD = 100µA (Note 1)                         | V <sub>DD</sub> - 0.025 |     |                                       | V       |

|              | Low Output Voltage                               | ILOAD = 10mA (Note 1)                          |                         |     | 0.15                                  | V       |

|              | Output Resistance                                | I <sub>OUT</sub> = 10mA, V <sub>DD</sub> = 18V |                         | 10  | 15                                    | Ω       |

|              | Peak Output Current                              | · · · · · · · · · · · · · · · · · · ·          |                         | 1.2 |                                       | A       |

|              | Continuous Output Current                        | Single Output<br>Total Package                 |                         |     | 300<br>500                            | mA      |

| , <b>_</b> , | Latch-Up Protection<br>Withstand Reverse Current | $4.5V \le V_{DD} \le 16V$                      | 500                     |     |                                       | mA      |

| hing         | Time                                             |                                                | <u> </u>                |     |                                       | **      |

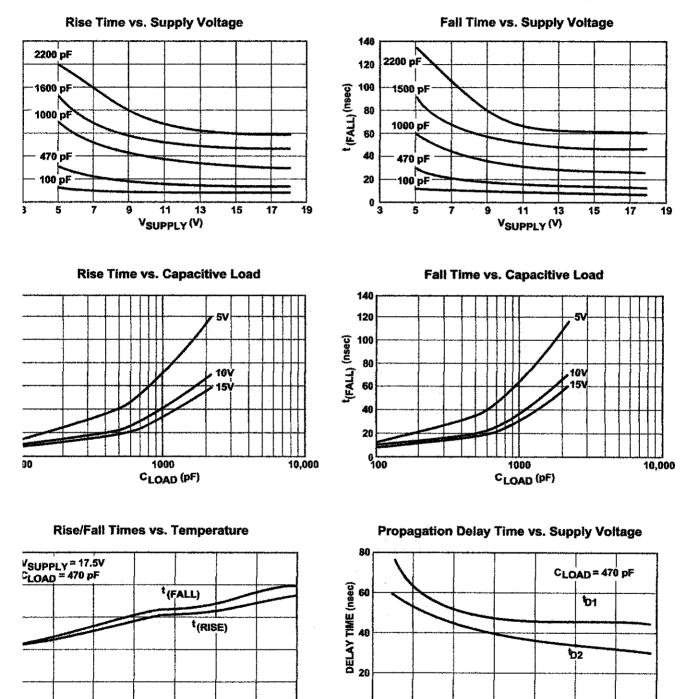

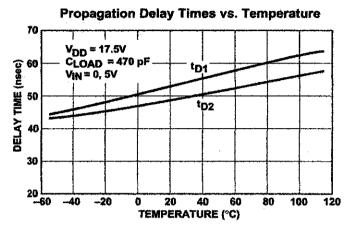

| ·····        | Rise Time                                        | Figure 1                                       |                         | 15  | 25                                    | nsec    |

| , <u>.</u> , | Fall Time                                        | Figure 1                                       |                         | 15  | 25                                    | пзес    |

|              | Delay Time                                       | Figure 1                                       |                         | 40  | 75                                    | nsec    |

|              | Delay Time                                       | Figure 1                                       |                         | 40  | 75                                    | nsec    |

| r Sup        | ply                                              |                                                |                         |     |                                       | ·harron |

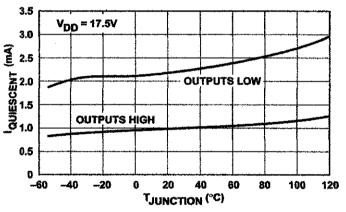

|              | Power Supply Current                             |                                                | ]                       | 1.5 | 4                                     | mA      |

|              | Power Supply Voltage                             | Note 2                                         | 4.5                     |     | 18                                    | V       |

# **TH TABLE**

| 0.         | TC4467 NAND |   |   |   | 1 | TC4468 AND |   |    | TC4469 AND/INV |   |   |   |

|------------|-------------|---|---|---|---|------------|---|----|----------------|---|---|---|

| SA         | Н           | н | L | L | н | н          | Ĺ | L  | Н              | н | L | L |

| SB         | н           | L | H | Ĺ | H | L          | н | L. | н              | Ĺ | н | L |

| JTS TC446X | L           | н | Н | Н | н | L          | L | L, | L              | Н | L | L |

h L=Low

**}-6 10/21/96**

# **GIC-INPUT CMOS QUAD DRIVERS**

# **ECTRICAL CHARACTERISTICS:** Measured throughout operating temperature range with $4.5V \le V_{Dd} \le 18V$ , unless otherwise specified.

| ıbol                                  | Parameter                   | Test Conditions                                | Min                     | Тур         | Max      | Unit |

|---------------------------------------|-----------------------------|------------------------------------------------|-------------------------|-------------|----------|------|

| ıt                                    |                             |                                                |                         | L           | <u> </u> |      |

|                                       | Logic 1, High Input Voltage | (Note 3)                                       | 2.4                     |             |          | V    |